# H-8200 処 理 装 置

H-8200 Processor

山 岸 峻 Takeshi Yamagishi

朝 倉 俊 彦\* Toshihiko Asakura 高 瀬 拓 士<sup>\*</sup> Takushi Takase

### 要旨

HITAC 8200 システムは、小規模のデータ処理や、低価格の衛星計算機として設計された、データ処理装置である。H-8200 処理装置は独立した計算機として、より大きなシステムの衛星計算機としてあるいはデータ通信システムのリモートターミナルとしての機能と大形機並の高速性を有している。本処理装置はプログラム内蔵式の汎用計算機として、内部記憶容量 4 KB、8 KB、16 KB の 3 種があり、その構成、特長および仕様概略について解説する。

### 1. 緒 言

1965年電子工業審議会が出した予想によると、わが国の電子計算機の設置台数は、1970年台には15,000台にのぼると推測されている。このうち11,000台は、使用料100万円/月以下の、小形電子計算機で占められるものと予想されている。

このように,ここ数年急激に小形電子計算機の需要が伸びてきた のは, 市場の要求に, つぎのような傾向がみられるからである。 (1) 超小形電子計算機(1) (PCS, 電子会計機など) ユーザーが, 本 格的 EDPSにレベルアップするため小形電子計算機を求めているこ と。(2) すでに、保有しているユーザーは、事業の規模によって計 算機械化が拡張できる EDPS のファミリシリーズに大きな魅力を もっていること。(3)企業内でのトータル・システムの一環とし て小形計算機を望んでいることなどにある。このような, 小形電子 計算システムの市場要求に対し、HITAC 8200 は、高速小形電子計 算システムとして開発設計されたのである。たとえば(1)他機種 への互換性一他の HITAC 8000 シリーズのプログラムとデータ上の 互換性をもち, さらに大形システムの基本的機能を備えているため システム移行が可能である。(2) 高速性と低価格―小形計算機に 属しながら価格に対し高性能の処理装置および入出力装置を配して いる。(3) HITAC 3010/4010 の実績と経験から、より使いやすい 充実したソフトウェアが開発されている。(4)供給電力が商用200 Vをそのまま使用できるなど市場の各分野ですぐれた力を発揮する ものと期待されている。 すでに HITAC 8200 は, 昭和 41 年 4 月, 日立ソフトウェアセンタに納入して以来, 二十数台の受注実績をも っている。本論文では、HITAC 8200 システムと処理装置のハード ウェアの面を主体に、特長と構成について解説する。

#### 2. システムの特長

HITAC 8200 は、コスト・パフォーマンスの強化を計るため H-8200 処理装置の記憶容量を、4Kバイトから 16Kバイトの 3 種類とし、システム・プログラムにおいて COBOL、FORTRAN の使用を可能にする設計方式とした。納入現地におけるメモリ増設は、メモリスタックとメモリ周辺回路のプラグインを組み込むことにより数時間内で顧客引渡しが可能である。また入出力装置においては、HITAC 8200 専用機器として、H-8422 形磁気テープ装置(情報処理速度 15Kバイト/秒、記憶密度 400 BPI)を開発し接続できる方式をとった。これにより本システムは、他の HITAC 8000 システムに比較し 15K、30K、60K、120Kバイトの磁気テープ装置と広範囲なしかも完全なハードウェア上の互換性をもち、そして HITAC 8100とは磁気テープを介して情報の互換性を備えている。特に小形

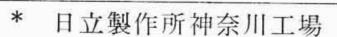

図1 処理装置

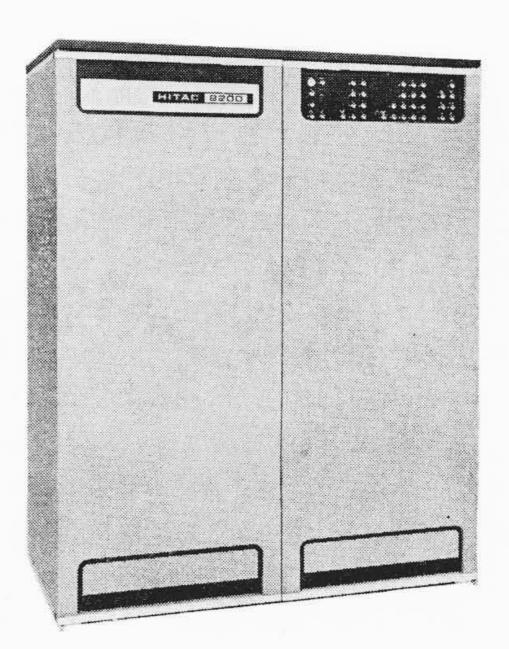

図 2 HITAC 8200 システム

電子計算機の互換性として、HITAC 8100 システムとは、完全なプログラム上の共通性を有し、磁気テープ装置( $H-8422 \leftrightarrow 8421$ )およびテープ読取り機( $H-8221/8222 \leftrightarrow H-8229$ )を介して情報の交換が可能である。

HITAC 8200 システムの特長は次の諸点にある。

日

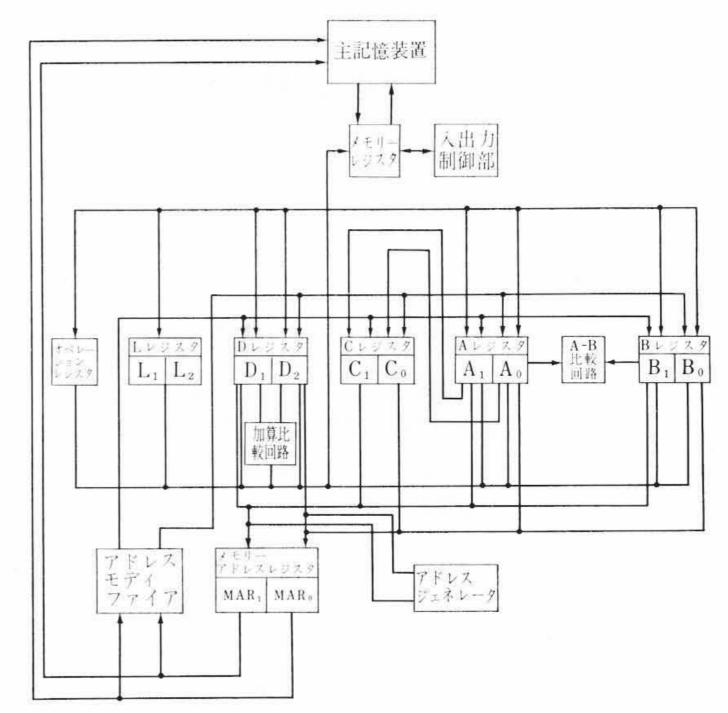

図3 処理装置の内部構造

(4) 1字は8ビット+パリティよりなるバイト表示する結果256種の文字が扱え、EBCDIKコードを使用できるほか、かな文字も英数字と同じレベルで扱える。PACK形式で演算を行なうことによって、数字は1バイトに2けた詰めることができ、コアメモリおよび磁気テープ・ファイルのスペースが節約され処理時間が短縮できる。(5) 処理能力に比べて価格が低廉、すなわち紙テープ・システムで月当り使用料が約100万円、最大構成に近い高性能システムでも約250万円である。(6)8000シリーズ標準入出力接続仕様により、処理装置と入出力装置との接続が標準化され、新しい装置の追加、変更が非常に容易となり、それに要するダウン・タイムもきわめて短く、プログラムの変更の必要もない。(7) プログラミングシステムが完備している。たとえばカードベース、紙テープベース両面において Assembler、COBOL、FORTRAN、RPG、Loader、Sort-Merge、Peripheral Routine、Program-Diagnostic、Library-Maintenance などが完備している。

## 3. 処理装置の構成

本処理装置は大別して主記憶装置,演算部,プログラム制御部, 入出力制御部,操作パネル部および電源部よりなる。

#### 3.1 主記憶装置

データおよびプログラムを記憶する磁気コア記憶装置と記憶装置 制御回路よりなる。

主記憶装置は、30 ミルの磁気コアを 32×32 面 4 マット=4096 ビットの構成に編線した電流一致方式のビットプレーンよりなる。そしてこのプレーン 18 面をスタッキングし、8,192 バイトを構成させケース内に組込んだものである。そしてX、Y駆動線、センス線ならびにインヒビット線を約 15cm のフレキシブルなリード線にて外部へ引出し 3 個のコネクタにより処理装置本体へ接続を可能にし、保守にも容易な構造としてある。このスタックのX、Y駆動線のアドレス選択用ダイオードマトリクス 8 枚は、演算部に用いているプラグイン寸法に合わせてあり、コネクタにより容易に取はずしできる構造である。スタックは、コネクタへ引出されるが、配線の違いによってA形、B形の 2 種類があり、温度補正のためのサーボ制御用の単一コアが装着されている。

HITAC 8200 では、1 バイトがアドレス可能な最も小さい単位である。メモリサイクルタイムは $2\mu$ sで、1 バイトの情報が、記憶装置からレジスタへ移され、さらに記憶装置に再書込みが行なわれる。主記憶装置内のおのおののバイトは2 進で指定される。アドレス指定には14 ビットを使用し最大16, 384 バイトのアドレス指定が可能である。Memory-Wrap-Aroundは主記憶装置の記憶容量により

図4 H-8200 処理装置ブロック図

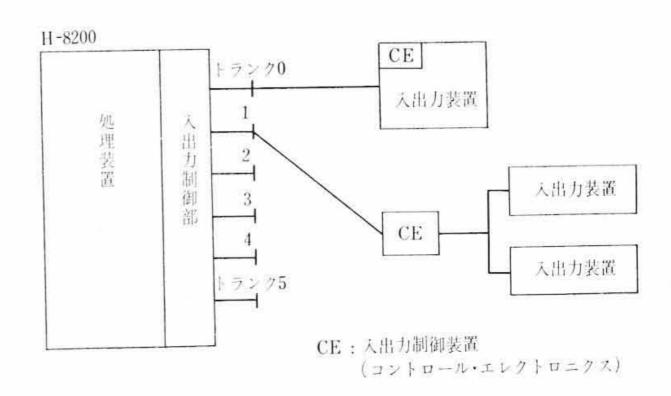

図 5 標準入出力接続方式

4,096, 8,192 あるいは 16,384 バイトで起こる。

HITAC 8200 では 2 進数によるアドレス指定を行なうが、 2 進数によるアドレスの表示はめんどうなので処理装置内での文字アドレスの表示は 16 進法で行なわれる。

主記憶装置の最初の50バイトに規定番地と称して処理装置それ自身のために使用される。この部分は、レジスタ、入出力動作の取扱中の一時記憶や割込み動作に使用される。

## 3.2 演算部, プログラム制御部

演算部は2進および10進の1バイト演算機能をもちすべて固定小数点演算で行なわれる。Dレジスタ,加算比較回路を中心に実行される。

プログラム制御部は主記憶装置に記憶された命令の解読と実行を行なう。プログラム制御部はオペレーションの順序を監視するための、インディケータとレジスタを持ち、自動的なチェックや標準入出力接続方式のトランクを介して情報のやり取りを行ない入出力機器の制御を行なう。プログラム制御部はおのおのの命令を実行するのみならず、主記憶装置から命令を取り出し、それを適当なレジスタにおく。この動作をスタティサイズ(Staticizing)と呼ぶ。命令のスタティサイズの時間は次のとおりである。

4 バイト長命令--16 μs 6 バイト長命令--20 μs

### 3.3 入出力制御部

HITAC 8200 システムには次の入出力装置を接続できる。カード 読取り機,カードせん孔機,テープ読取りせん孔機,ラインプリンタ, 磁気テープ装置,光学文字読取り機,問合せタイプライタ,インタフェース・スイッチ,データ交換制御装置,単チャネル通信制御装置以上の各装置を任意に組合せ接続することができる。入出力制御部は,入出力制御装置を介し入出力装置の制御を行なう。HITAC 8200の入出力装置にはすべて標準入出力接続方式を採用している。

装

| -1- 1 |      | ^   | -    | · · · · | In. |

|-------|------|-----|------|---------|-----|

| 表 1   | 俞    | 会   | 0    | 形       | 7/  |

| 21    | rela | 1.2 | 2007 | 11      | 1   |

| ハーフワード |          | ハーフワード         |      | ハーフワード |      |

|--------|----------|----------------|------|--------|------|

| バイト1   | バイト2     | バイト3           | バイト4 | バイト5   | バイト6 |

| OP     | L        | $D_1$          |      | $D_2$  |      |

| OP     | $L_1L_2$ | $\mathrm{D}_1$ |      | $D_2$  |      |

| OP     | TU       | $D_1$          |      | $D_2$  |      |

| OP     | M        | $D_2$          |      |        |      |

| OP     | TU       | $D_2$          |      |        |      |

入出力制制部には6本のトランクがあり、1トランクに最大16台の入出力装置を接続することができる。そして一時に一つのトランクを制御し、バッファ装置を除き、すべての入出力操作はシリアルに行なわれる。しかしながら Read Auxiliary または Write Auxiliary 命令を用いることにより同時処理ができる。

### 3.4 操作パネル部

H-8200操作パネルは、制御スイッチおよび表示ランプより構成され計算機の操作と保守に使用される。処理装置の右上に位置し操作パネルと保守パネルの二つに分かれている。

操作パネルは、必要な押ボタンと表示器で、プログラムコード、 プログラムの開始と修飾、読み取りあるいは書き込みレジスタの内 容の表示を行なう。保守パネルは、処理装置の論理と制御機能の解 析を容易にするために、必要な押ボタンと表示器からなる。このパネルは保守員によって使用される。

#### 3.5 電 源 部

処理装置の入力電源は  $AC 200V \pm 10\%$ , 3 相 3 線式である。電源部は処理装置操作パネル裏面上段に実装されていて、三相トランス,パワートランジスタ、円筒形放熱器、プラグインよりなっている。安定化直流出力は、

+30V, -30V, +5V (処理装置の論理回路に供給される) そして, -20V, -14V (主記憶装置に供給される) である。

## 4. 処理装置の性能

#### 4.1 命令の形式

HITAC 8200 には 26 の命令があり、これらは演算、論理、データ 処理、判定、制御および入出力の各動作に用いられる。

命令の基本形式は4または6バイト長である。すべての命令はハーフワードの端 (偶数番地) から始まる必要がある。21 個の命令は、2アドレス形式で6バイトの長さを持ち、残り5個が1アドレス形式で4バイトの長さの命令である。 HITAC 8200 では最大16、383番地まで、アドレス指定を行なうことができる。 これら命令の形式は表1のとおりである。

- (1) OP 部.....オペレーションコードで1バイトで構成される。

- (2) L 部……処理するデータ長をバイト単位で指定する。 1 バイトで構成されるので、最大 256 バイトのデータを取扱うことができる。 $L_1$ ,  $L_2$  は第 1 演算数と第 2 演算数が異なるときで、それぞれバイト数より 1 減じた数を指定する。

- (3) T, U部……入出力命令の場合に用いる。 Tは4ビットから構成され,入出力装置を接続する処理装置の6本のトランクに対応する。Uは4ビットから構成され,Tで指定したトランクに接続している入出力装置の番号を指定する。TとUを指定することによりシステム接続された入出力装置が選択される。

- (4) M 部.....1バイトから構成され、プログラムの順序を 変更する条件を指定する。

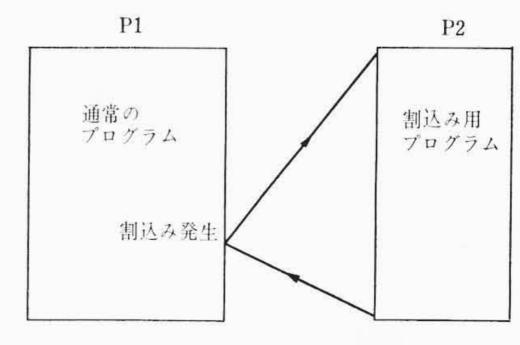

図 6 HITAC 8200 の割込み方式

(5) D 部……HSM の番地を指定する。加工すべきデータの記憶されている番地あるいは条件によってプログラムの順序を変更しようとする際,その命令の記憶してある左端の番地を指定する。D部は $D_1$ と $D_2$ に区分される。 $D_1$ は2バイト(16ビット)で構成され,第1演算数を記憶してある左端番地を指定する。 $D_2$ は $D_1$ の第1演算が第2演算数に変わる以外同様である。なお $D_1$ , $D_2$ ともに16ビットで構成されるが,HITAC 8200 の最大記憶容量は16,384バイトでありビット数は14ビットとなる。上位2ビットは常に00である。

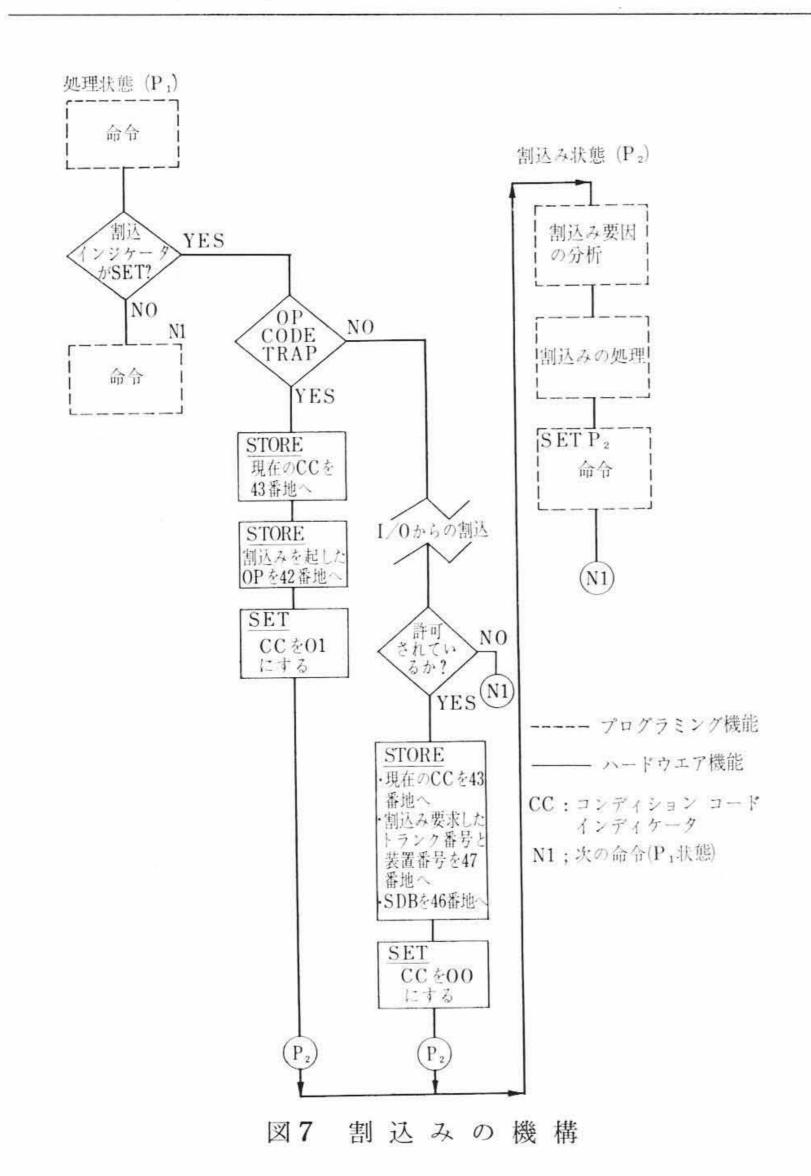

#### 4.2 割込み機構

#### 4.2.1 HITAC 8200 の割込み

HITAC 8200 は、プログラム・カウンタを 2 個持っている。 1 個は処理状態(P1)、1 個は割込み状態(P2)でおのおの記憶装置の 40、41 番地と 44、45 番地を占有する。

処理状態(P1).....この状態では通常のプログラムが実行され、 プログラムは P1 カウンタの制御下で実行される。この状態にあ るときにのみ割込みが可態である。割込みがかかると自動的に割 込み状態に移る。

割込み状態 (P2)……この状態では割込みの原因解析と処理のプログラムが実行され、プログラムは P2 カウンタで制御される。この状態にあるときは、割込みを行なうことはできない。Set P2 Register 命令を実行することによって、処理状態に戻る。

## 4.2.2 割込みの要因

HITAC 8200 で割込みを起こす要因には次の(1)と(2)がある。 (1) 入出力装置からの外部割込み要求

ここでいう入出力装置とは、問合せタイプライタ、単一チャネルに通信制御装置、データ交換制御装置である。これらの割込み要求は問合せやデータの伝送を処理するものである。

(2) オペレーション・コード・トラップによる割込み要求

HITAC 8200 で定義されている 26 種以外の命令がくると,割込みが生ずる。この割込みを使って 26 種以外の命令をシュミレートすることができる。処理装置に割込みがかかると,割込みインディケータがセットされる。割込みは命令が終了するごとに,割込みインディケータがセットされているか否か調べる。セットされている場合には,その時点で割込みが起こり制御はP1からP2の状態に移る。

(3) 入出力装置からの割込み要求の受け入れ禁止

2種類の割込み要因のうち、入出力装置からの外部割込み要求を禁止することができる。これは記憶装置の49番地を使い、その49番地の下位6ビットをマスクすることにより、対応するトランクからの割込みを禁止することができる。

割込み受付け.....対応ビットが1のとき

割込み禁止……対応ビットが0のとき

たとえばマスクが 00100011 のとき,割込み要求はトランクが 0, 1,5 のものについてのみ受付けられ,それ以外のトランクからの 日

主2 加 理 挂 器 灶 能 丰

|          | 表 2        | L 埋 | 表 直 性 能 表                                     |  |  |

|----------|------------|-----|-----------------------------------------------|--|--|

| 項        | 且          |     | 性能                                            |  |  |

| 主記憶装置    | 容 量 (KI    | 3)  | 4, 8, 16                                      |  |  |

|          | サイクルタイ     | ٨   | 2 μs                                          |  |  |

|          | バイト/アクセ    | ス   | 1                                             |  |  |

|          |            | 路   | トランジスタ――ダイオード                                 |  |  |

| プログ      | ラム ステー     | ŀ   | 2                                             |  |  |

| 命 令 数    |            |     | 26                                            |  |  |

| セレクタチャネル |            |     | 1                                             |  |  |

| マルチン     | プレクサチャネ    | ル   | 0                                             |  |  |

| 1 - 1 ×4 | セレクタチャネ    | ル   | 6                                             |  |  |

| トランク数一マ  | マルチプレクサチャネ | ネル  | 0                                             |  |  |

| -        | 1 1 1      | ŀ   | 8 ビットナパリテイ                                    |  |  |

| データの表現   |            | 字   | 2 け た/バ イト                                    |  |  |

| 演 算 -    | 2          | 進   | ग्र                                           |  |  |

|          | 10         | 進   | пſ                                            |  |  |

| 同 時      | 処 理 能      | カ   | RDA/WRA — 演 算<br>RDA/WRA — RDF/WR + バッファ付 I/o |  |  |

| 五.       | 換          | 性   | 8200 -> 8300 / 8400 / 8500                    |  |  |

| マル       | チシステ       | 7   | П                                             |  |  |

| 割 込      | み 要        | 因   | 2                                             |  |  |

|          |            |     |                                               |  |  |

割込みは禁止されている。もしあるトランクから割込み要求が出されたが、マスクによって禁止されている場合、割込みはできない(割込み待要求)。このトランクをプログラムで使用するには、マスクをはずし割込みを受付けてから使用するか、またはPost Status 命令を実行してから使用する。

次に HITAC 8200 の割込みの論理を図7に示す。これにより割込みが行なわれたときの必要な情報は、指定された場所に退避され、CCに割込みの要因の区別を表示する。

(a) 高速形 NANDゲート回路

(b) 低速形 NANDゲート回路

図8 HITAC 8200 基本回路

#### 4.3 性 能

H-8200 処理装置の性能を表2に示す。

#### 4.4 基 本 回 路

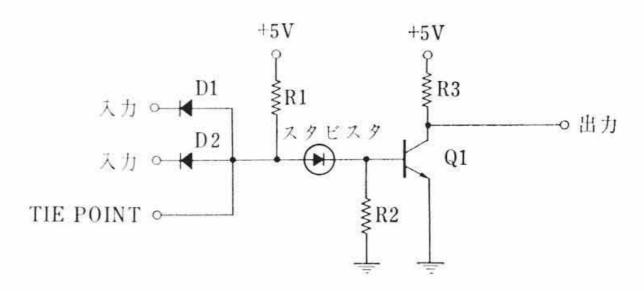

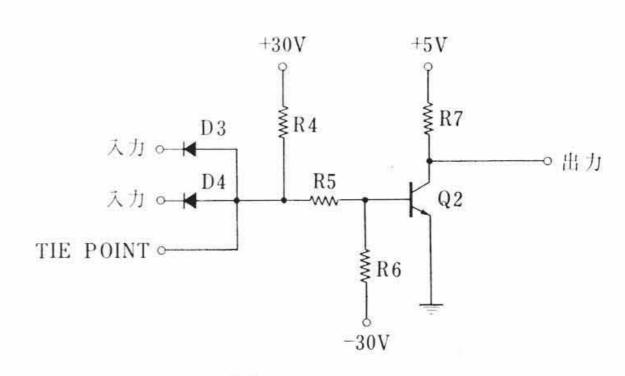

HITAC 8200 の基本回路は,入出力装置と同一の 32 P 形プラグインパッケージ回路を使用している。各機器共通な基本回路は,図8に示すとおり,NAND ゲート回路である。

基本回路は、(1) ダイオード・ゲート (2) レベルシフタ (3) トランジスタ・インバータの三つの論理ブロックからなっている。 ダイオード・ゲートは入力信号の極性により、OR または AND ゲートとして動作し、ゲート数の追加端子として、 $TIE \cdot POINT$  が設けられている。

入力のレベルシフトは、スタビスタまたは抵抗分割により行なわれ、トランジスタベースに結合してインバータにより反極性の出力信号を得ている。スタビスタはシリコンダイオードであり、順方向電圧降下が0.6V あり、温度特性が良くレベルシフタとして有効に動作する。フリップフロップは、2個のNANDゲートをクロスカップルしたものであり、シフトレジスタ、カウンタなどもこれらの組合せによって構成されている。

論理レベルは、ハイレベルが +5V, ローレベルが +0.2V であり、最悪状態ではそれぞれ、+4V, +0.4V である。また電源や、布線誘導によって信号にのるノイズに対するマージンは、ポジティブノイズでは、次段への影響は少なく、ネガティブノイズに対してはより十分広くとる設計としてある。そして基本回路の周囲条件は、温度  $15\sim55$ °C において回路定数、電源値の偏差が最悪状態にても動作するよう設計されている。

プラグイン回路には、論理用途によって高速形と低速形があり使い分けられている。両者の違いは、図8に示すとおりトランジスタ、回路定数、バイアス値およびレベルシフタの違いであり基本的回路構成は同じである。したがって立上り、立下り時間、波形の遅延時間、スイッチングの応答が異なってくる。

本基本回路の特長は、従来機種の基本回路に比べて、回路素子が 少ない、回路電源が1種類でも使用できる、応答が速い、そして広 い温度範囲にわたり安定に動作するなどがあげられる。

図9は基本回路を実装したプラグインの裏布線の模様を示したものである。処理装置内部布線は、ラッピング方式(無はんだ接続)を 採用しており、配線接続不良による事故は皆無に近い。また布線は 処

図9 内部布線方式

最短距離になるよう配線されており、信号の遅れ、減衰など十分考 慮された方式である。

#### 5. 結 言

置

HITAC 8200 は、演算の高速化、信頼性の向上、装置の小形化、コストの低減を図るため装置には信頼性の高い電子部品を各所に採用している。特に論理回路を構成するプラグインには、コンポーネントモジュール (CR の複合部分品)を大幅に採用し、メモリ周辺回路には特性向上のため集積回路を用いている。また本体 row の布線を従来機種には見られない印刷回路板方式にした。この結果組立作業、検査作業が少なく、保守が容易になっている。一方ソフトウェア面では、わかりやすく能率的な各種プログラミング・パッケージが豊富な実績と経験の上に立って用意されている。

このように本装置は,ハード・ソフトともに最近の技術を駆使して開発されたもので,信頼性のある小形電子計算機として,公共団体,一般中堅企業から期待されている。

#### 参 考 文 献

(1) 日本電子工業振興協会編: 1966日本の電子計算機(昭 41-6)

# 画 ※ 園 新 案 の 紹 介 園 ※ 園 ※ 園

登録実用新案第778195号

宇多村幸彦

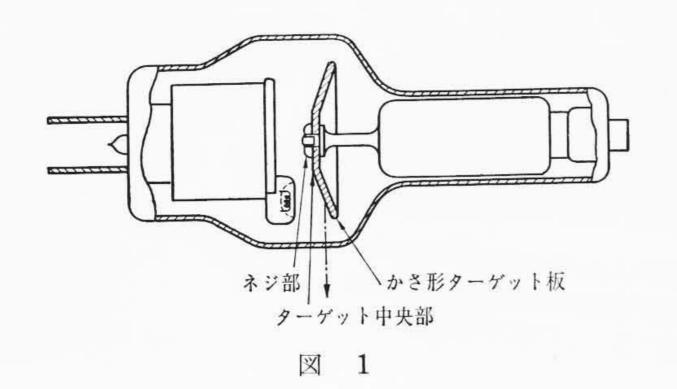

#### 回転陽極形X線管

従来の回転陽極形 X線管は図1に示すように、かさ形ターゲット板の中央部のかさ形上面が平らで、これを保持固定する止めネジ部はその上面にさらに突出した構造であるため、このターゲット板の中央部およびネジ部からの二次散乱 X線が主 X線放射方向にも放射されることになり、けい光板あるいはフィルム上に X線像を得る場合カブリあるいはボケなどを生じて鮮鋭度がはなはだしくそこなわれるという欠点があった。

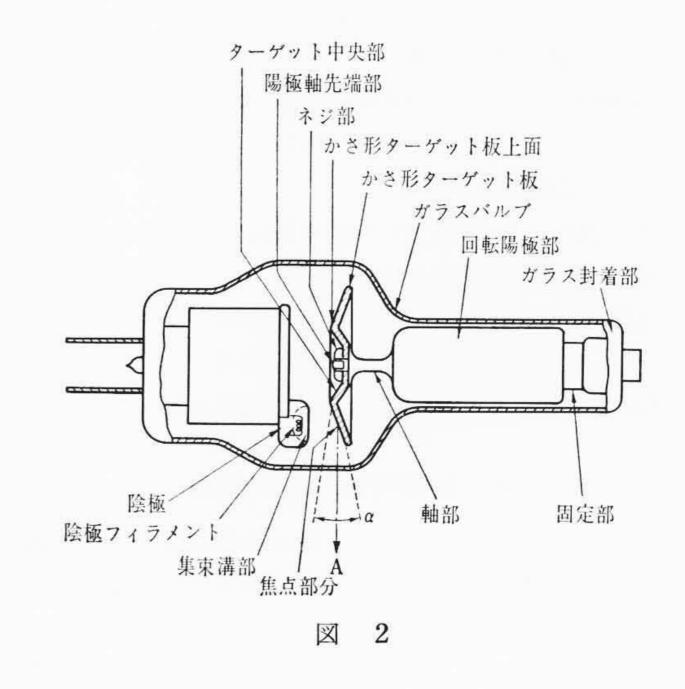

この考案は上述のような欠点を取り除くために,図2に示すように回転されるかさ形ターゲット板の焦点部をはずれるターゲット中央部およびターゲット板を保持固定する軸先端部と止めネジ部とを,かさ形ターゲット板の上面部よりくぼむようにし,この中央部

軸先端部および止めネジ部などの表面から放射される焦点外二次散乱 X線の大部分が,主 X線放射方向に放射されないようにしたものである。 (福田)