# サイリスタ応用特集

| 超高耐圧サイリスタ49              |

|--------------------------|

| 大容量サイリスタとその応用53          |

| 交流電動機のサイリスタ制御59          |

| 高速度サイリスタとチョッパ制御67        |

| 最近の汎用サイリスタ, ダイオードとその応用71 |

| 家庭電気品へのサイリスタの応用77        |

# 超高耐圧サイリスタ

Ultrahigh Voltage Thyristors

鲁 井 達 弥\* 小 川 卓 三\*\*

Tatsuya Kamei Takuzô Ogawa

守田啓一\*\*\* 和島幸一\*\*\*

Keiichi Morita Kôichi Wajima

# 要

応用分野の拡大に呼応してサイリスタの高耐圧大容量化への動きが最近とみに活発になっている。本文では超高耐圧大電流サイリスタの設計方法および定格の設定方法について検討し、高耐圧化に伴う諸問題点およびその解決策について論ずるとともに、新たに開発した $4\,kV$ ないし $10\,kV$ の超高耐圧サイリスタの諸特性を紹介する。

# 1. 緒 言

現在,高耐圧大電流のサイリスタは電気車両の直流電動機制御, 圧延機用電動機の制御用電源あるいは化学工業用直流電源など重化 学工業に広く用いられている。さらに最近では直流送電系統の変換 装置あるいは静止スイッチ,しゃ断器など超高圧大電流の分野にも サイリスタを応用しようとする試みが盛んになっている。

このような大容量変換装置では多数のサイリスタ素子を直並列に接続して使用しなければならないが、個々の素子の変換容量を大きくし、使用する素子数を少なくしたほうが、装置全体の信頼性および経済性の両面から見て有利であると考えられる。現在、これらの応用分野で主として使われている素子は2.5 kV、400A 定格であるが、上述の理由からさらにサイリスタ素子を高耐圧大容量化することが望まれている<sup>(1)</sup>。

われわれはこのような背景のもとにサイリスタの高耐圧大容量化について検討を続けてきた結果,4kVないし10kVの超高耐圧サイリスタを相ついで開発することに成功した。本文では超高耐圧サイリスタの設計概念,素子の製作方法および主要な電気的特性について述べる。

# 2. 記 5

*A*: 定 数

C: 定 数

D: 両極性拡散係数

DE: エミッタ層の小数キャリアの拡散係数

J: 電 流 密 度

$J_B: qDN_E \tanh (W/2L)/L$

$J_E: q D_E N_E/L_E$

K: 定 数

k: ボルツマン定数

L: 両極性拡散長

L<sub>E</sub>: エミッタ層の小数キャリアの拡散長

$L_p$ : nベース層のホールの拡散長

M<sub>p</sub>: ホールのなだれ増倍係数

NE: エミッタ層の不純物濃度

n: 定

n<sub>i</sub>: 真性半導体でのキャリア濃度

P: 許容順損失密度 (平均值)

図1 超高耐圧サイリスタ

q:素 電 荷

$T_J$ :接合温度

$t_d$ : ターンオン時の遅れ時間

ton: ターンオン時間

toff: ターンオフ時間

$V_B$ : pn接合のなだれ降伏電圧

$V_{BO}$ : サイリスタのブレークオーバ電圧

V: 逆 電 圧

$V_F$ : 順電圧降下

W: 等価ベース幅

$W_n$ : n < - ス幅

$x_n$ : nベース側の空間電荷層幅

$\rho_n$ : nベース層の抵抗率

# 3. 超高耐圧サイリスタ設計の理論

サイリスタの電気的特性は阻止電圧、電流容量およびスイッチング特性の三者で代表されるが、これらはいずれも素子の接合部の構造と密接に関連しており、ためにほかの特性を変えずに一つだけを改善するということは困難である。したがって高耐圧化しようとする場合にもある程度ほかの特性が犠牲になることを覚悟しておく必要がある。すなわち、サイリスタの阻止電圧を高くするにはそのnベース層を厚くする必要があるが、これは接合内部のキャリアの輸送過程に影響し、ターンオン時間および順電圧降下の増加をもたちす。この影響を少なくするにはnベース層の小数キャリアの寿命を長くすることが有効であるが、そうすると今度はターンオフ時間が増加する。

サイリスタを高耐圧化する場合にはこれらの事情を考慮して,用 途に応じた電圧定格を設定する必要がある。ここでは,まず高耐圧 サイリスタの性能を表わす指数が変換容量,すなわち阻止電圧と電 流容量の積で与えられるとして議論を進め,スイッチング特性につ いては後で述べることにする。

<sup>\*</sup> 日立製作所日立研究所

<sup>\*\*</sup> 日立製作所日立研究所 理学博士

<sup>\*\*\*</sup> 日立製作所日立工場

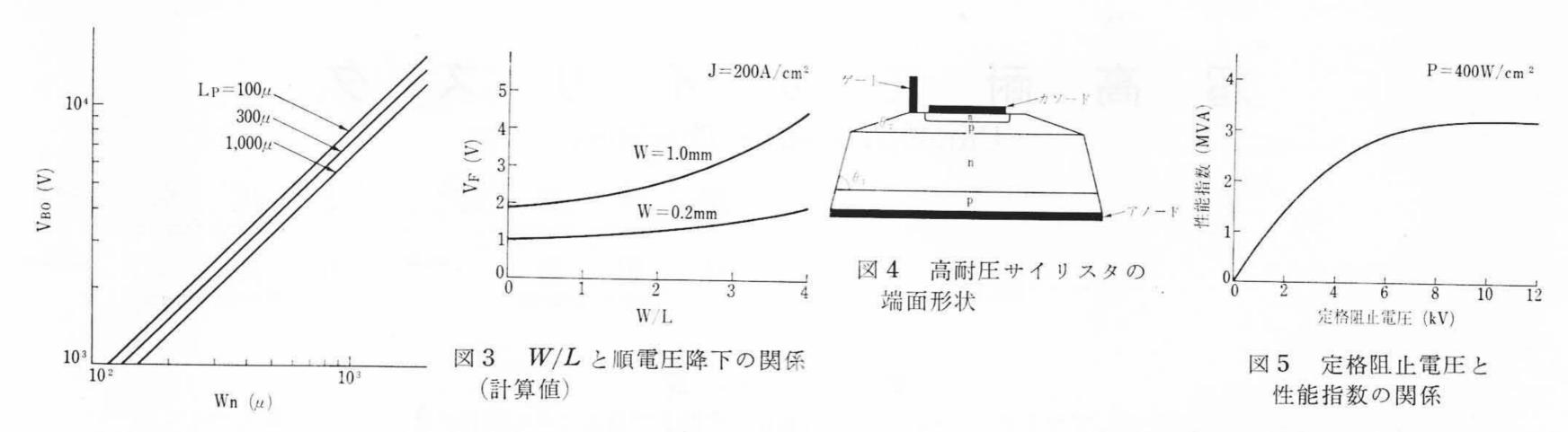

図2 サイリスタのブレーク オーバ電圧の計算値

### 3.1 阻 止 電 圧

サイリスタの阻止電圧は逆バイアスされた中央接合の空間電荷層におけるなだれ増倍過程と、nベース層における小数キャリアの輸送過程によって決定される。すなわちブレークオーバ条件は次式で与えられる(2)。

$$M_p \operatorname{sech}\left(\frac{W_n - x_n}{L_p}\right) = 1 \dots (1)$$

$M_p$ ,  $x_n$  はいずれも n ベース層の抵抗率  $\rho_n$  および印加電圧 V の関数であり次式で近似できる。

$$x_n = K(\rho_n V)^{\frac{1}{2}} \dots (2)$$

$$M_p = \left(1 - \left(\frac{V}{V_B}\right)^n\right)^{-1} \dots (3)$$

$$V_B = C\rho_n^{\frac{3}{4}} \dots (4)$$

(1)式に(2), (3), (4)式を代入し、さらに高耐圧サイリスタではブレークオーバ電圧付近では有効ベース幅はかなり小さくなるから、 $W_n-x_n\ll L_p$ と仮定すると、次の(5)式が得られる。

(5) 式を  $\rho_n$  で微分することにより  $\rho_n$  に対する V の最大値  $V_{BO}$  を求めると

が得られる。 したがって  $\rho_n$  を最適となるように選べばブレークオーバ電圧は  $L_n$  の  $-\frac{8}{7n}$  乗および  $W_n$  の  $\frac{6n+8}{7n}$  乗に比例する。 K, C, n にそれぞれ計算値を用いて(6)式をプロットすると図 2 が得られる。

### 3.2 電 流 容 量

電流容量は順方向損失による接合温度上昇が規定の値以下でなければならないという要請から決められる。しかし接合温度上昇は外部の冷却条件にも左右され問題が複雑になる。ここでは簡単にカソードの単位面積あたりの順方向損失が許容順損失密度Pとなる電流密度から電流容量を求めることにする。素子の電流定格や外部の冷却条件に応じてPを適当に定めることにすれば一般性は失なわれない。

サイリスタの順電圧降下については小川 $^{(3)}$ ,大塚 $^{(4)}$ ,Kokosa $^{(5)}$ 氏らが論じているが、ここではサイリスタを実効ベース幅W,実効拡散長Lの対称形 pin ダイオードと等価であると仮定する。 高導通状態における順電圧降下は次式のように表わすことができる。

$$V_{F} = \frac{2 kT}{q} \left( \ln \left( \frac{\lambda N_{E}}{n_{i}} \right) + \left( 1 + \frac{\lambda J_{E}}{J_{B}} \right) \sinh \left( \frac{W}{2L} \right) \tan^{-1} \sinh \left( \frac{W}{2L} \right) + \frac{W_{E}J}{D_{E}N_{E}} \right)$$

$$\dots (7 a)$$

$$\lambda = \left( \frac{J_{B}}{J} + \sqrt{1 + \frac{2J_{E}}{J} + \left( \frac{J_{B}}{J} \right)^{2}} \right)^{-1} \dots (7 b)$$

$$J_{E} = \frac{q D_{E} N_{E}}{L_{E}} \coth \left( \frac{W_{E}}{L_{E}} \right) \dots (7 c)$$

$$J_{B} = \frac{q DN_{E}}{L} \tanh \left( \frac{W}{2L} \right) \dots (7 d)$$

(7a)式の右辺の括弧内の各項はそれぞれ接合部、ベース層およびエミッタ層の電圧降下に対応する。(7)式を計算する場合にD, L はそれぞれ注入レベルおよび温度に依存する量であり、見掛けよりも複雑であることを注意しておく。図3は300°K、200 A/cm² における W/L と $V_F$  の関係を示したものである。電流密度は方程式

$$V_F J = P$$

......(8)

を数値的に解いてWおよびLの関数として定めることができる。

### 3.3 変 換 容 量

(6)と(8)式から接合の単位面積あたりの変換容量をWとLの関数として求めることができる。さらにこの値が最大になるようにLを定めれば最終的にはWだけ(あるいは、Wと $V_{BO}$ は(6)式により一対一に対応するから $V_{BO}$ だけ)の関数となる。このようにして得られた値に接合面積を掛ければ求める阻止電圧と性能指数である変換容量の関係が得られる。ただし、この際阻止電圧が高いサイリスタほど有効接合面積が小さくなることに注意しなければならない。

半導体素子では接合内部よりも接合が表面に露出した部分でブレークダウンすることが多い。したがって高耐圧化するためには内部の耐圧よりも沿面での耐圧を高くしておかなければならない。このため通常図4に示すような表面成形(surface contouring)を行ない沿面距離を延ばし、沿面電界を下げている。シリコン板が厚くなるほどこの成形に要する面積が大きくなり、有効面積が小さくなるのである。サイリスタの高耐圧化にあたってはこの点にじゅうぶん注意して沿面形状を選ばなければならない(6)。

図 5 は直径 40 mm のシリコン板に対し、 $P=400~W/cm^2~として$ 計算した性能指数 (変換容量)を示したものである。この条件では阻止電圧 10~cいし 11~kV で性能指数が最大となり、大容量変換装置にはこの程度の阻止電圧のサイリスタ素子を用いるのが有利であるといえそうである。しかし、性能指数最大となる阻止電圧はPの値によって変化することに注意しなければならない。

電力回路では短絡などの事故時には定常時の数十倍に及ぶ過電流が発生する。保護装置との協調上、サイリスタには定格平均順電流の約20倍の1サイクル過負荷耐量が要求されるのが普通である。サージ耐量を考慮するとPは図5の算出に用いた値よりずっと大きくなる。図5のピーク位置もこれに応じて低電圧側に移動する。

#### 3.4 スイッチング速度

サイリスタは小数キャリアの輸送過程に支配される素子であるから、ベース幅が厚くなるほど過渡応答時間が長くなる。ターンオン時間はキャリアの走行時間に関係するゆえ、ベース幅の2乗に比例すると考えられる。一方ターンオフ時間は導通状態の間にベース層内に蓄積されていたキャリアが外部へ流出する時間と、逆阻止機能が恢復し内部のキャリアが減衰する時間に分けられるが、通常後者がずっと長い。結局、キャリアの寿命に依存することになる。

図3に見られるように W/L をあまり大きくすると順電圧降下が急増するから、いま W/L を一定にするものと仮定する。 $(6\ a)$  式で  $L_p \propto W_n$  とすると  $L_p$  は  $V_{BO}$  の  $7_6$  乗に比例するという結果になる。したがってターンオフ時間は阻止電圧の  $7_3$  乗に比例するという結果になる。スイッチング時間は回路条件や接合温度などで大幅に変わるが、いずれにせよ耐圧の高い素子ほどスイッチングは遅くなるから、用途によってはスイッチング時間によって阻止電圧の上限が決ってしまうことがある。したがって素子の最適な阻止電圧は用途に応じて決定されるべき性格の値であると言える。しかし、後述するようにサイリスタのスイッチング特性はベース層の厚さだけでなく、半径方向の構造によっても大幅に改善することができるから、 $4\ kV$  以上の超高耐圧サイリスタでもじゅうぶん広範囲の分野で応用することが可能である。

# 4. 製作方法

pnpn 接合を製作するには拡散合金法,全拡散法などが考えられ,それぞれ一長一短がある。新しい素子を開発するにあたっては与えられた仕様を満たすのにもっとも適した製法を選ばなければならない。超高耐圧サイリスタの製作方法に課せられる条件は三つある。まず,前節で述べたように小数キャリアの寿命をじゅうぶん長く,かつ精密に制御できることである。第 2 にpnpn 各層の厚さおよび不純物濃度を正確に,かつ均一に制御できることである。第 3 には半径方向の構造を自由に製作できることである。高耐圧サイリスタではdv/dt 耐量およびdi/dt 耐量なども耐圧に見合って大きくしておかなければならない。このような動特性を改善するにはカソード,ゲートなどの構造をくふうするのが有効である。たとえば,

図9 10 kV サイリスタの 阻止電圧の温度依存性

図 10 4 kV サイリスタの 順導通特性

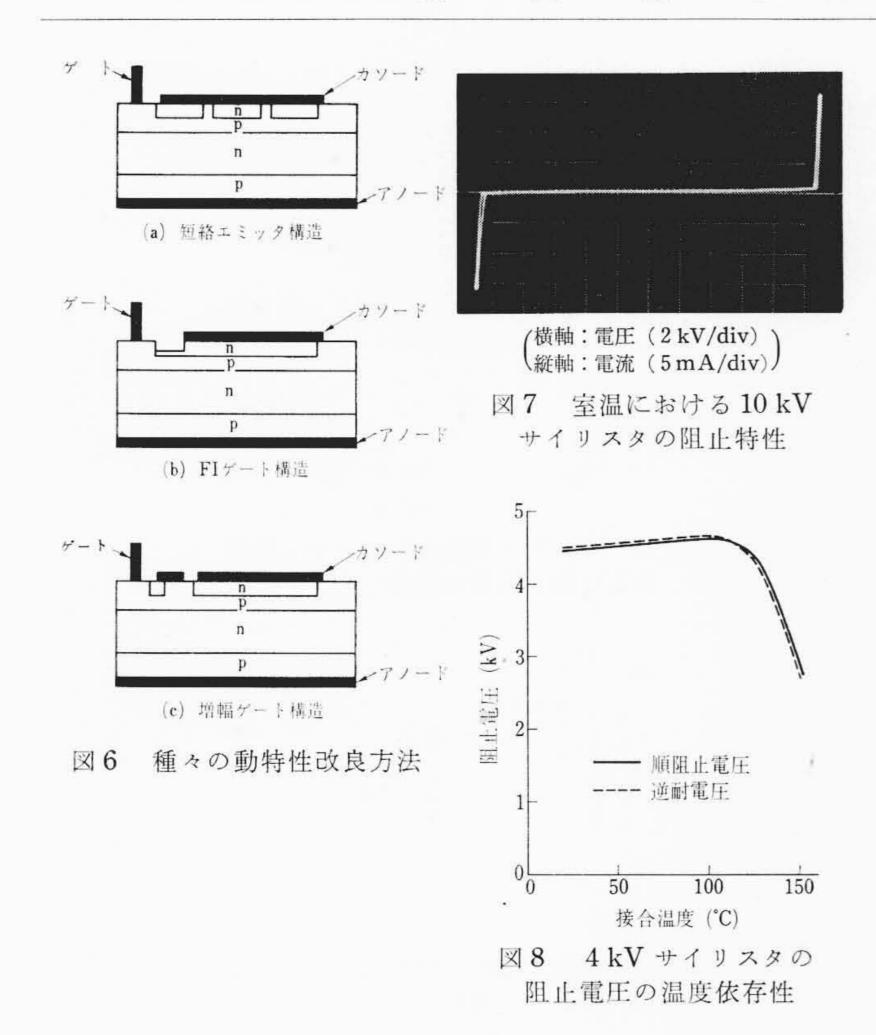

dv/dt 耐量は図 $\mathbf{6}$ ( $\mathbf{a}$ )に示した短絡エミッタ構造<sup>(7)</sup>により自由に変えることができる。 また di/dt 耐量を増すには図 $\mathbf{6}$ ( $\mathbf{b}$ )に示した FI ゲート構造<sup>(8)</sup>あるいは図 $\mathbf{6}$ ( $\mathbf{c}$ )に示した増幅ゲート構造<sup>(9)</sup>などが知られている。これらの構造につきじゅうぶんな検討を行ない高 耐圧化に伴う動特性の低下をカバーするよう考慮する必要がある。

こういった観点からわれわれは全拡散法を採用した。全拡散法では大きな面積のウェハーでも均一な拡散層を作ることができ、かつ、拡散の温度時間を制御することにより、各層の厚さ、不純物分布なども自由に変えることができる。また、拡散とゲッタリングのプロセスを適当に組合せることによりキャリアの寿命を長くすることができる。熱処理前のシリコン板や治具類の処理を注意深く行なって汚染を避け、特殊なゲッタリング処理を施すことにより、素材における寿命をほとんど損なわずに pnpn 接合を形成することが可能となる。

先に述べたように高耐圧化のためには接合の沿面形状に注意する必要がある。検討の結果図 4 に示したような沿面形状では 4 kV 以上の素子に適用した場合に,順阻止電圧が逆耐電圧に比べてずっと低くなること,沿面成形によるシリコン板の面積損が大きいこと,などの欠点が見いだされた。このため形状および表面処理法などを検討した結果,新たに SBC(symmetrical blocking contour)法を開発した。この方式の採用により,電流容量をあまり減らさないでも,10 kV あるいはそれ以上の電圧まで,順逆両方向とも図 2 の理論値どおりの阻止電圧を得ることができるようになった(10)。

図7は10kV サイリスタの阻止特性を示したものである。

このようにして製作した接合部をユニットセル形パッケージに収納し、素子の上下両面から熱放散を行なわせるようにした。図1は完成した超高耐圧サイリスタの外観写真である。 左側は4kV,右側は10kVのサイリスタである。 10kV サイリスタには二重ひだ構造のパッケージを採用し、沿面絶縁にはじゅうぶん注意してある。

# 5. 素子の電気的特性

### 5.1 阻 止 電 圧

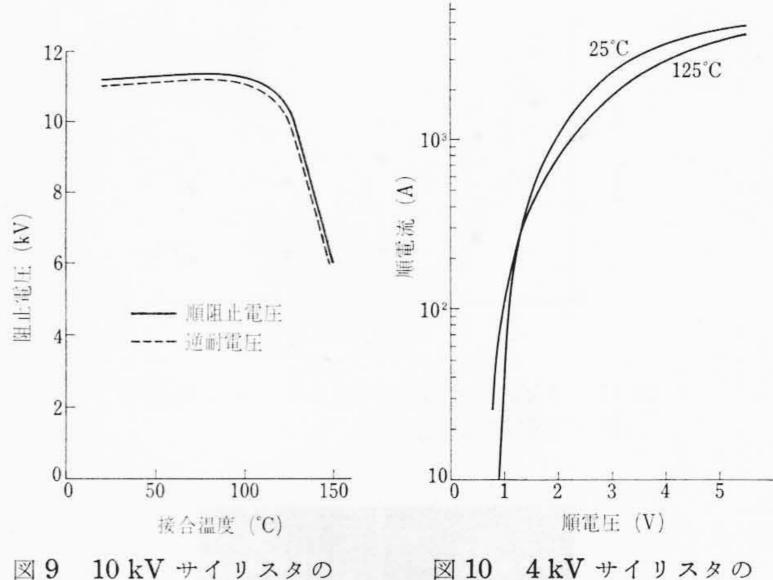

図8は4kV サイリスタの阻止電圧の温度依存性を示したものである。 また図9は10kV サイリスタの阻止電圧の温度依存性を示したものである。

### 5.2 導 通 特 性

図 10 は 4 kV サイリスタの順導通状態における電流一電圧特性を室温および 125℃ について示したものである。10 kV サイリスタでは順電圧降下は 4 kV サイリスタに比べるとやや大きくなる。

### 5.3 ターンオン特性

サイリスタを直列接続して使用する場合, 直列素子の間でターン

図 11 4 kV サイリスタのターンオン時間の ゲート電流依存性

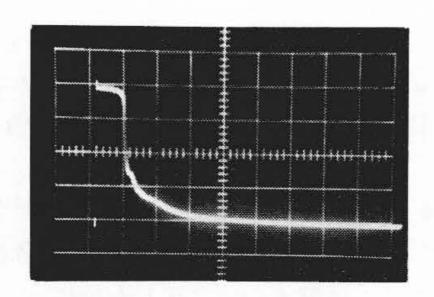

横軸:時間 1 μs/div )図 12 4 kV サイリスタの ゲートターンオン特性

(縦軸: 電圧 500 V/div)

オンの遅れ時間 $t_a$ のばらつきが大きいと、ターンオン時の電圧分担が不平衡になりターンオンの遅れた素子に大きな電圧がかかることになり、好ましくない。したがって遅れ時間は短いことが望ましい。また、ゲート電流への依存性、ターンオン前のアノード電圧への依存性が弱いことが要求される。

図 11 は 4 kV サイリスタのゲート電流とターンオン時間および遅れ時間の関係を示したものである。ターンオン前のアノード電圧は 2,000 V, またゲート電流の立上り時間は 0.5  $\mu$ s, パルス幅は 100  $\mu$ s である。ゲート電流 0.5 A 以上では遅れ時間はほぼ飽和し,かつ素子間のばらつきも少ない。 図 12 はターンオン時の電圧波形を示したものである。 10 kV サイリスタにおいても遅れ時間は 4 kV サイリスタとほぼ同等であり,0.5 A 以上のゲート電流では飽和することがわかった。

また、図 13 は 4 kV サイリスタについてゲート電流を 2 A 一定 としてアノード電圧とターンオン時間および遅れ時間の関係を示したものである。 $t_a$  はアノード電圧にほとんど依存しないことが見られる。

ターンオン時の導通領域の広がりが遅い素子では回路電流の立ち上がり (di/dt) が速い場合にはゲート近傍に電流が集中し, hot spot を生じる。このような現象を避けるため特殊なゲート,カソード構造を採用しスイッチングパワー耐量の増加を図り,1,000 kW 以上の耐量を有することが確認された。

## 5.4 dv/dt 耐 量

阻止状態にあるサイリスタに急激に順電圧を印加すると、中央接合の空間電荷層の充電電流が流れサイリスタはターンオンしてしまうことがある。このような現象を避けるため図7(a)に示すような短絡エミッタ構造を採用した。4kV素子について室温ないし150

試験を行なった結果, $800V/\mu s$  の dv/dt で 2,000V まで印加してもスイッチしないことが確認された。 この dv/dt 耐量は広範囲の応用面からの要求に対してじゅうぶん余裕のある値である。

# 5.5 ターンオフ特性

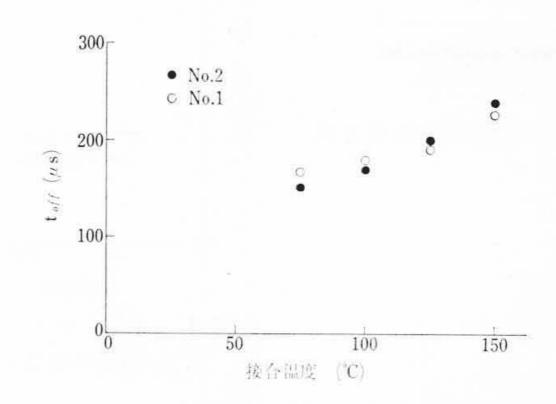

図 14 は 4 kV サイリスタの接合温度とターンオフ時間の関係である。順電流は幅数 100 µs 波高値 2,000 Aのパルス電流である。ま

図 13 アノード電圧とターンオン時間 および遅れ時間の関係

図 14 4 kV サイリスタのターンオフ時間の 温度依存性

た、接合温度は通電前の値である。125<sup>°</sup>C以上ではターンオフ時間が急増するが、それでも 150<sup>°</sup>Cで  $250~\mu s$  以下であり直流送電など速いスイッチングが必要な用途にも適していることがわかる。パルス電流値を 500A ないし 2,000A まで変えて電流値への依存性を調べたが、依存性は認められなかった。

一方 10 kV サイリスタではターンオフ時間はかなり長くなるので今後ともこの点の改善が必要とされる。回路適用にあたってはこの点検討が必要である。

# 6. 結 言

4 kV ないし 10 kV の超高耐圧サイリスタについて、その設計方法,製作方法および特性について述べた。電流容量、スイッチング速度などから生ずる制限を考えると、逆阻止形サイリスタの阻止電圧の上限は 10 kV 程度であると考えられる。 この限界を打破するにはさらに技術の進展が必要である。

終わりに,超高耐圧サイリスタの開発にあたり終始ご指導ご激励をいただいた,日立製作所高木機電事業本部長,桑山日立研究所長,浅野日立工場整流器部長,川島日立研究所第7部長およびご協力いただいた社内の関係各位に厚く御礼申し上げる。

### 参 考 文 献

- (1) Calverly, T. E., Direct Current, 1, 1, (1969)

- (2) Herlet, A., Solid-State Electron., 8, 655, (1965)

- (3) 小川, 電学誌, 87, 207, (1967)

- (4) Otsuka, M., Proc. IEEE, 55, 1400, (1967)

- (5) Kokosa, R. A., ibid., 1389, (1967)

- (6) Kamei, T., et al., IEE Conference Publication, 53-1, 39, (1969)

- (7) Gentry, F. E., et al., Semiconductor Controlled Rectifiers, Prentice Hall Inc., 138, (1965)

- (8) Somos, I., Piccone, D. E., Proc. IEEE, 55, 1306, (1967)

- (9) Gray, D. I., Electronics, 96, (1968)

- (10) 亀井, ほか, 電気学会東京支部大会予稿集, 483, (1969)