# 小形制御用計算機の積分形アナログ入力装置

Integrating-type Analog Input Device for Small Control Computers

加藤和男 Kazuo Katô

二 橋 義 行\* Yoshiyuki Nihashi

小西務\*\* Tsutomu Konishi

#### 要旨

小形制御用計算機のプロセス入出力装置 (PI/O) 用として小形,高性能で,経済的な積分形アナログ入力装置を開発した。装置はマイクロリードリレー形マルチプレクサと,高速,高ノイズ除去率に設計した2回積分形 A-D 変換器を主体として構成されており、装置の高信頼化を図るため、可及的に回路のIC 化を押し進めている。本文は装置を構成する主要アナログ回路の新しいハードウェア技術と、その実験結果について述べる。

#### 1. 緒 言

近年,電力,鉄鋼,化学などの各種工業応用分野において,計算機制御が急速に進められつつあることは周知のとおりである。日立製作所においてはHITAC 7250, HIDIC 500, HIDIC 100 という制御用計算機ファミリイが開発されている。

制御用計算システムでは、制御対象であるプロセスと、計算機の中央処理装置との間に介在して、情報の授受および変換などの処理を行なうプロセス入出力装置(PI/Oと略称する)が使用される。このうちで、特にアナログ入力信号の走査、増幅、A-D変換などを行なうアナログ入力装置(AIと略称する)は、計算制御システム上コストに占める割合が相当大きい。したがって、小形制御用計算機のPI/Oとしては、大形制御用計算機に用いるものに対し、精度を落とさずにいかに安価な AI を開発するかが問題となる。

ここに、AI は主として、入力切換のためのマルチプレクサ、フィルタ、低レベル増幅器、A-D 変換器、電源から構成されているが、これらは上述の要求を満たすように構成されていなければならない。

そこで、A-D変換器に一種の計数方式の積分形を採用し、リードリレーによるマルチプレクサの簡略化、標準発振器の自動周波数制御によるフィルタの簡単化、低レベル増幅器のIC化、DC-DC変換方式により電源の小形、内蔵化などを行ない目的を達成している。

本報は、これらの技術的な問題の検討、試作装置による実験結果を取りまとめ報告するものである。

#### 2. 制御用計算機とプロセス入出力装置

#### 2.1 PI/O の構成と機能

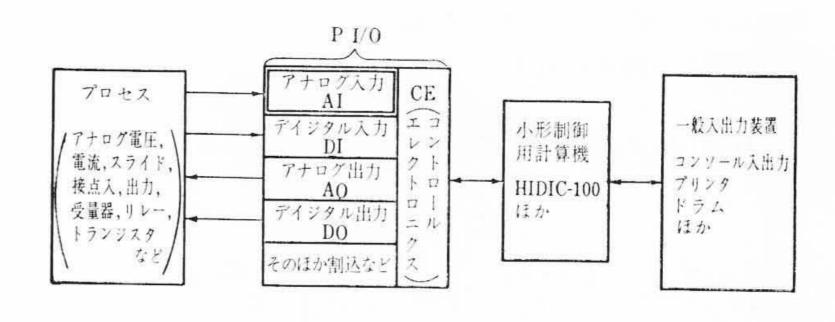

図1は本装置(AI)が使用される計算制御システムの概略構成図である。制御用計算機にはタイプライタ、テープリーダなどの一般入出力装置のほかに、プロセス入出力装置(PI/O)と呼ばれる制御用計算機独得の入出力装置が計算機と制御対象プロセスの間に介在し、各種信号の授受を行なっている。PI/Oにはアナログ(A)、ディジタル(D)、入力(I)、出力(O)、の別に従って、AI、AO、DI、DOの機能と、その他割込みなどの機能、コントロールエレクトロニクス(CE)と称する計算機との標準インターフェースをつくる機能部分に分けられる。以下、比較的回路構成上むずかしく特徴のあるAIについて述べる。

- \* 日立製作所日立研究所

- \*\* 日立製作所大みか工場

- \*\*\* 日立製作所日立研究所 工学博士

図1 計算機制御システムの概略構成図

#### 2.2 AI に対する要求

通常、AIの入力としては熱電対、サーチコイル、スライド、発信器そのほかの信号が多数混在するので、これら信号源を走査しA-D変換を行なう AIとしては次に示すような機能を備えている必要がある。

- (1) mV オーダから V オーダまでの広範囲な信号を扱えること。

- (2) 必要に応じた速い走査速度,変換速度を有すること。

- (3) コモンモード電圧のある非接地信号を扱えること。

- (4) 入力ノイズの影響を受けにくい方式であること。

- (5) 入力点数の増減に応じられること。

- (6) 小形で信頼性の高いこと。

#### などである。

#### 2.3 AI 開発の問題点に対する解決法

前述 2.2 の要求に対して生じた問題点を解決するため、下記の方法を用いた。

- (i) ノイズ除去特性が高く,直流的に絶縁された高速積分形 A-D変換器の開発(主として(2),(3),(4)に対して)

- (ii) 集積回路(ICと略称する)化した直結形ゲイン可変プリアンプの開発((1),(5),(6))

- (iii) 高実装密度のマイクロリードリレー形マルチプレクサの採用((3),(5),(6))

- (iv) 直流絶縁形の小形電源の採用((3), (6))

### 3. 積分形 A-D 変換器とそのノイズ除去法

#### 3.1 各種積分形 A-D 変換方式の比較

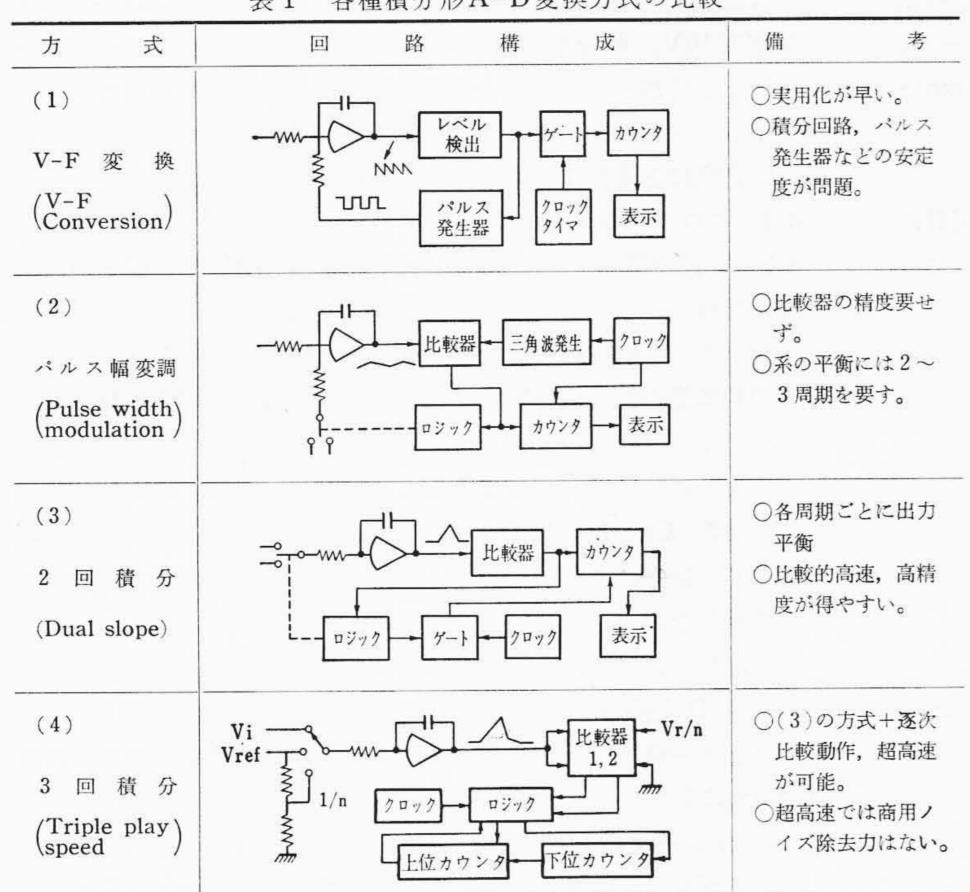

積分形 A-D 変換器は、入力信号の積分期間が入力信号に混入する交流ノイズ周波数の基本波の整数倍に等しくなるように選定されている。このような積分(器)フィルタの作用によって周期性ノイズが平均化される。この種変換には表1に示すような各種の方式が実用化されている。筆者らは、このうち比較的高速、高精度が得や

表 1 各種積分形 A-D変換方式の比較

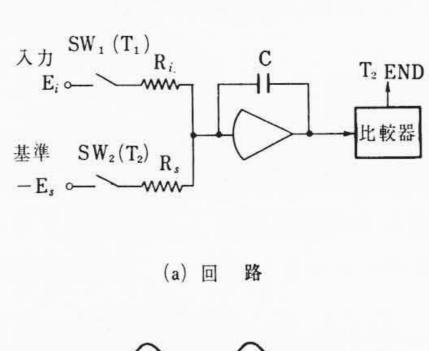

図2 2回積分方式A-D変換の原理説明図

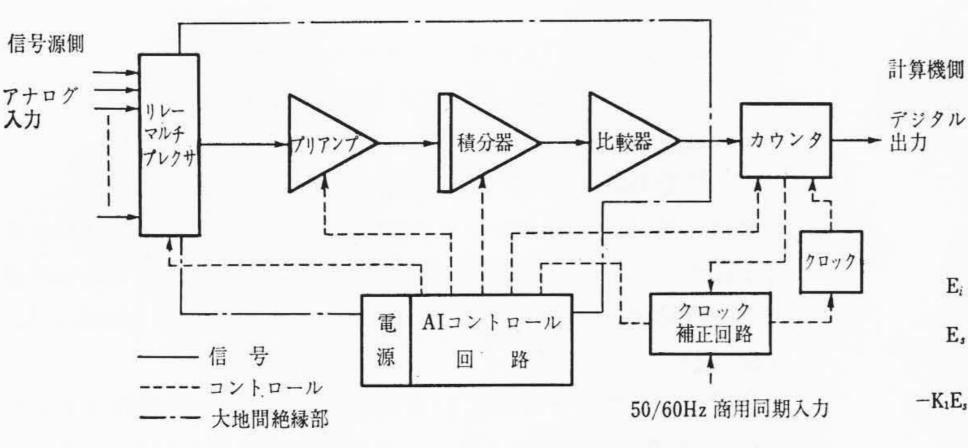

図3 積分形アナログ入力装置のブロック図

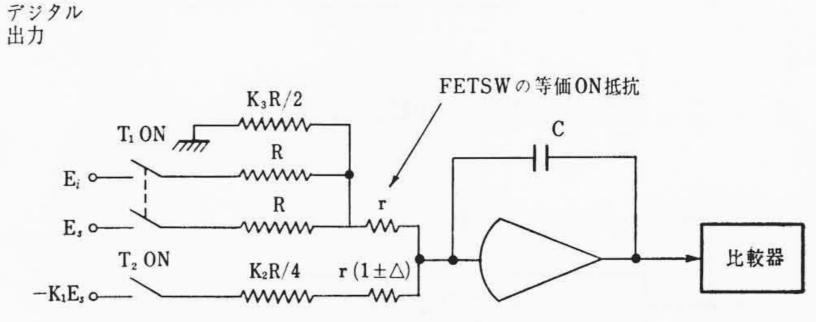

図4 高速,高精度積分回路の構成

すく,かつ早期より実積<sup>(3)</sup>のある2回積分形方式をAI用として採用し、検討した。

#### 3.2 2回積分形 A-D 変換器の原理とノイズ除去率の向上

図 2 は 2 回積分形 A-D 変換器の動作原理図である。 この回路の動作は、まず  $SW_1$  を閉じて  $T_1$  の期間入力  $E_i$  を積分し、次いで  $SW_1$  を開いて  $SW_2$  を閉じ、積分器出力が初めの値に戻るまで基準電圧  $-E_S$  を積分して、その期間  $T_2$  を計数して読み出す。すなわち次のようになる。

$$E_{0} = -\frac{1}{C} \left( \int_{0}^{T_{1}} \frac{E_{i}}{R_{i}} dt - \int_{T_{1}}^{T_{1}+T_{2}} \frac{E_{S}}{R_{S}} dt \right) = 0 \quad .....(1)$$

$$\therefore \quad \frac{T_{2}}{T_{1}} = \frac{R_{S}}{R_{i}} \cdot \frac{E_{i}}{E_{S}} \quad .....(2)$$

通常、プロセスのフィールドノイズとしては商用周波数およびその高調波成分が主であるから、(2)式の  $T_1$  の値としては 50 Hz, あるいは 60 Hz の整数倍に選べば原理的には効果的なノイズ除去が行なえる。 しかし商用周波数は常に厳密に一定ではなく、短時間的には  $0.1\sim0.2$  Hz 程度は変化するため、これがノイズ除去率の低下をきたし、AI 用としての高速、高精度の要求を満足できない。

そこで,種々検討した結果,周波数変動が生じても  $T_2/T_1$  の比が 実質的に変わらないように補正するため,標準発振器の周波数を商用周波数の変化に応じて変えるような自動周波数制御 $^{(4)}$  (AFC)回

路を採用した。 その場合には積分期間  $T_1$ ,  $T_2$ , 出力データNの関係は次のようになる。

ただし, f<sub>L</sub>: 商用電源周波数

K: クロックの fL に対する倍数比 (一定)

(2), (3)式から出力データNは,

$$N = \frac{R_i}{R_S} \cdot \frac{E_i}{E_S} \quad \dots \quad (4)$$

となって、入力に混入する商用周波ノイズの影響を受けない。 商用周波ノイズ除去率の小さい、高速、高精度な A-D 変換が可能になる。

#### 4. 装置の構成およびその動作

#### 4.1 積分形アナログ入力装置の構成

図3は積分形アナログ入力装置全体のブロック図である。マルチプレクサほかプリアンプ, A-D変換器などのアナログ信号回路は電源部分で2線入力一大地間を直流的に絶縁して動作させている。 構成素子はマルチブレクサにマイクロリードリレーを使用したほか は、アナログ、ディジタル両回路とも可及的に IC 化して高信頼化されている。本装置の概要は入力  $\pm 10\,\mathrm{mV} \sim \pm 10\,\mathrm{V}$  フルスケール、出力  $14\,\mathrm{Eu}$  ト、走査速度  $33\,\mathrm{m}$  回/s ( $50\,\mathrm{Hz}$ )、 $40\,\mathrm{m}$  ( $60\,\mathrm{Hz}$ ) ( $\mathrm{max}$ ) である。

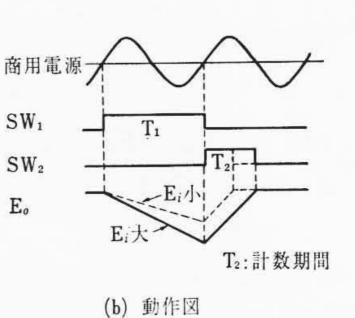

#### 4.2 積 分 回 路

図4は積分回路の構成を示したものである(ただし,回路定数は一般化してある)。増幅器および入力スイッチには IC を使用した。この回路では入力の積分期間  $T_1$  を商用の 1 サイクル,  $T_2$  をフルスケールで 0.5 サイクルとしており,入出力の関係は次のようになる。

$$T_{2} = \frac{T_{1}}{4} \left( 1 + \frac{E_{i}}{E_{S}} \right) \left\{ \frac{K_{2}R + 4 r(1 \pm \Delta)}{K_{1}(R + 2 r) + \frac{2 r}{K_{3}}} \right\} \dots \dots (5)$$

ただし、 r: 2個1組の FET スイッチの等価 ON 抵抗

**△**: 一組の FET スイッチの 等価 ON 抵抗のばら

つき

$K_1, K_2, K_3$ : 周辺回路によって定まる比率 (定数)

(5)式で第3項が1になるよう各定数を設定すると FET の ON 抵抗その他の影響が僅少となって高速,高精度な積分ができる。

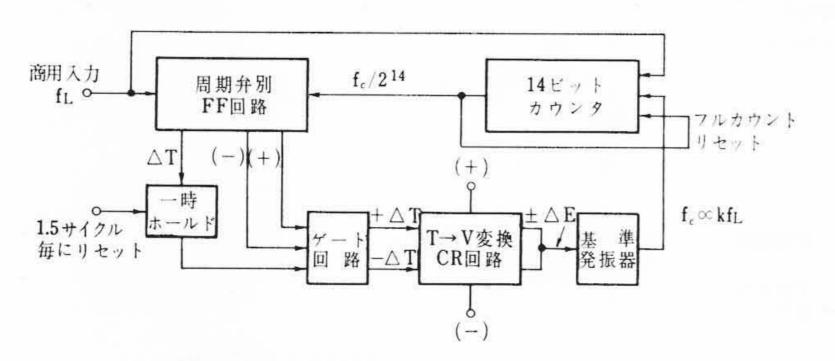

図5 クロック AFC 回路のブロック図

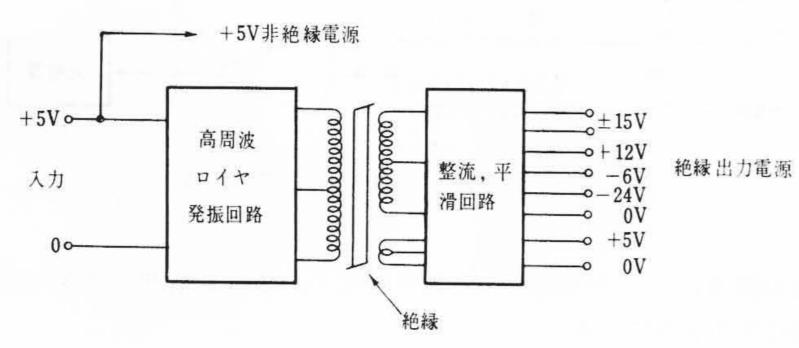

図6 電源部の構成

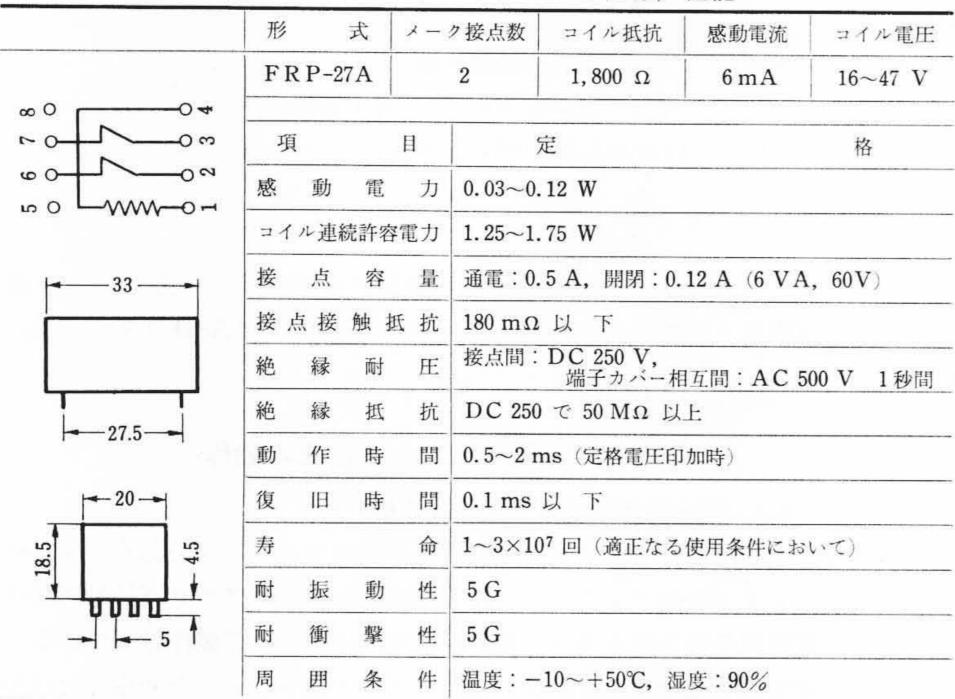

表2 マイクロリードリレーの仕様, 性能

具体的な使用条件は、プリアンプからの入力電圧  $E_i=0\sim\pm10\,\mathrm{V}$  基準電圧  $10\,\mathrm{V}$  、積分器出力  $0\sim-10\,\mathrm{V}$  で、基準電圧を入力に常時バイアスとして加えることにより基準電圧の正負切換を不用にしている。 積分コンデンサにはエチコンを使用しているので積分器の直線性、安定度はともに  $1\,\mathrm{Fi}$  がっト(0.006%)以内である。

#### 4.3 クロックの AFC

3.2(3)式の関係を満たすためのクロックの AFC は、図5の回路で行なわれている。この動作は、商用周波数周期とクロック周波数をカウンタ(データ計数と共同)で分周した周期との差をとり、その偏差で基準発振器の周波数を変化させて商用周波に同期したクロックをつくる。回路はサンプリング制御で各回ごとに偏差の修正が完了するように開回路利得を1に選んであるが、ループ内に積分要素(T-V変換、CR回路)がはいっているため定常的には利得が無限大となり、動作は原理的に高速、高精度で、かつ制御系が不安定になる恐れがない。

偏差の修正は常時商用周波の1.5 サイクルごとに行なわれるが、入力のA-D 変換中でも $T_1$  の期間で検出した偏差パルス幅を $T_2$  の終わりまで一時ホールドすることにより、同様に1.5 サイクルの修正を可能にしている。

#### 4.4 リレーマルチプレクサ

マルチプレクサには次の条件を考慮して、マイクロリードリレーを採用し、特に低レベル用として接点に Au, Ag 拡散したものを使用した。

- (1) 耐圧, 絶縁が大きく, フロート入力が容易。

- (2) スイッチの OFF/ON 比が大きく高精度が可能。

- (3) 安価で駆動が容易。

- (4) 積分形に見合った動作速度で、寿命も実際上問題ない。

表 2 にマイクロリードリレーの性能, 仕様を示す。マルチプレクサは 1 枚のプラグインに 16 点実装したビルディング・ブロック方式で 16 点単位で最大 512 点まで増加することができるものとした。

#### 4.5 雷 源

本装置では主要アナログ部を直流絶縁し非接地で動作させるため、フロート電源が必要になる。この電源部も極力小形化し、経済的なものとするため、図6に示すよう計算機などの主電源の+5VからDC/DCコンバータにより必要な種類の電圧をつくり、装置に一括給電する方式を採用している。絶縁部には高周波励振を行なっているため比較的小形である。

なお,このほかに本マルチプレクサシステムには,入力点の断線 検出,過電圧の検出,保護,そのほかの機構が付加して あり,バランスのとれたシステムを構成しているが,詳 細は割愛する。

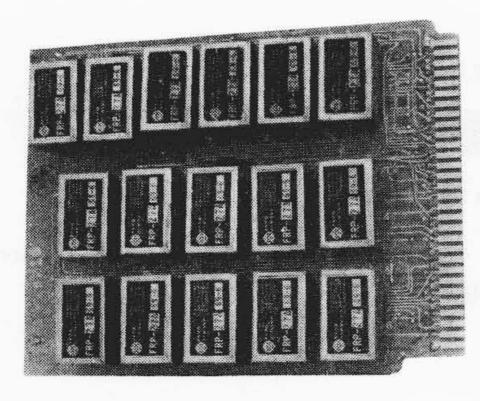

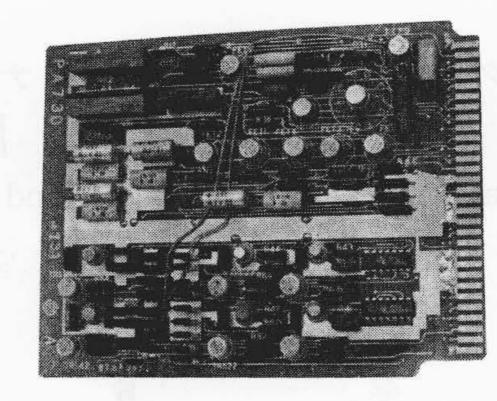

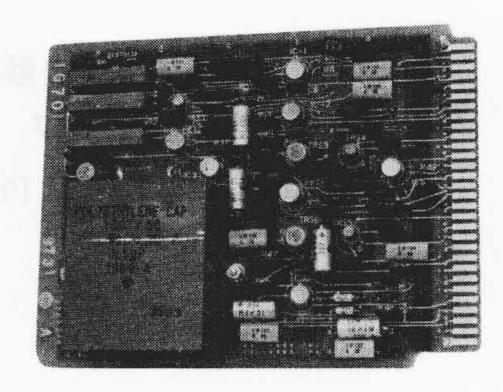

図7は本装置の主要部のプラグインを示したものである。

## 5. 実験結果とその検討

#### 5.1 ノイズ除去特性

おもな結果についてのみ示す。

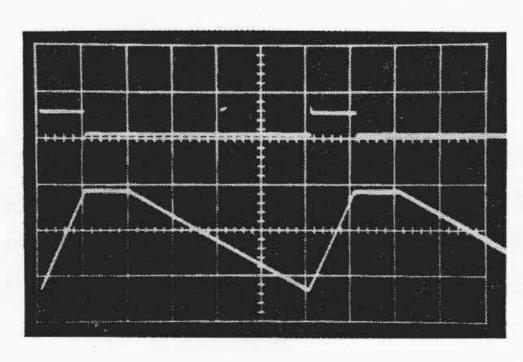

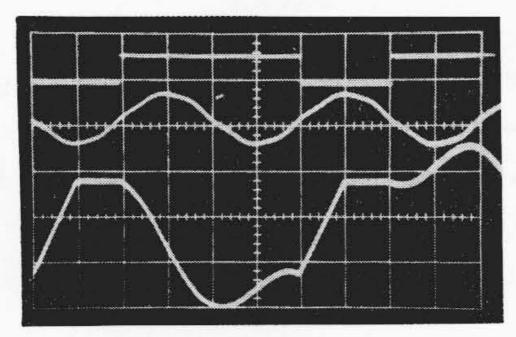

図8(a),(b)は積分形 A-D変換器の入力に商用周波ノイズ(50 Hz)を印加した場合としない場合の積分器出力波形の比較を示したものである。 A-D変換器自体はクロックの AFC による高ノイズ除去率 (1/4,000 $\approx$ 72 dB)を持つため,(b)図の積分波形程度になってもなお設差は 0.1% 以下である。しかし AI としてのクロスモードノイズの許容値はプリアンプが飽和しない最大許容入力に等しい。

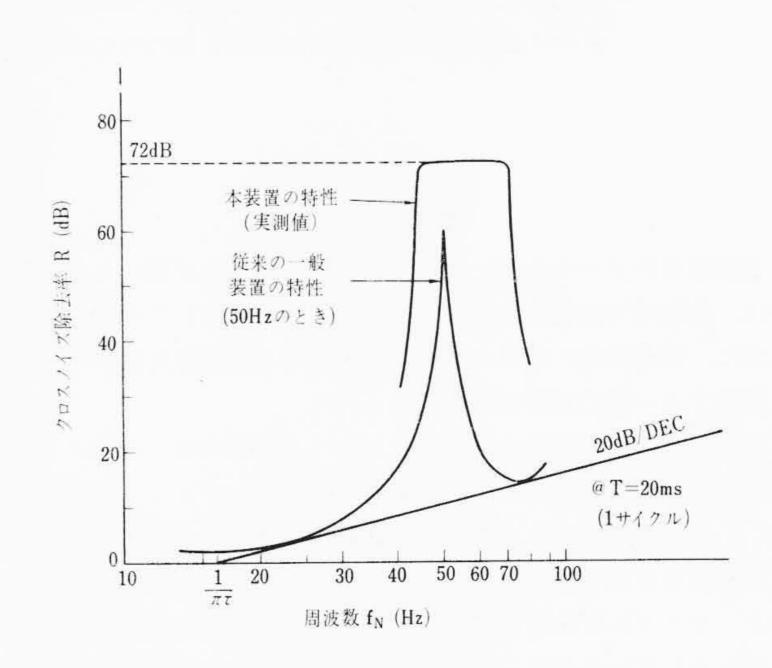

図10はノイズ周波数が変化した場合のノイズ除去特

(a) マルチプレクサ

(b) プリアンプ

(c) 積 分 器

図7 主 要 部 プ ラ グ イ ン

出力データ(時間幅) 10 V/D, 5 ms/D

積分器出力波形 2 V/D, 5 ms/D

(a) 入力にノイズのない場合

積分器入力SW動作 50 V/D, 5 ms/D 商用周波ノイズ入力 50 V/D, 5 ms/D 積分器出力波形 2 V/D, 5 ms/D

(b) 入力に商用周波ノイズのある場合

図8 積分器の動作波形

#### 5.2 入出力特性

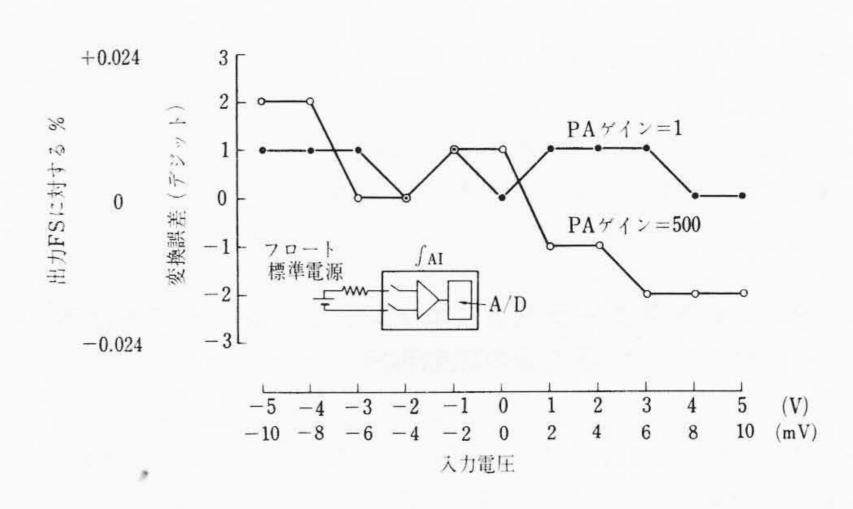

図10は装置全体の入出力特性例を示したものである。 プリアンプゲインが低い場合にはきわめて良好であるが、ゲインの高い場合には直線性、そのほかが若干悪く、またアンプの低周波ノイズのため数デジットのばらつきがある。しかし実用上は全く問題がない程度である。

## 6. 結 言

計算制御プロセスの多様化の進展に伴って、使用されるプロセス入出力装置も小形、高性能で経済性の高いものが望まれている。今回これにこたえて高性能積分形 A-D 変換器を主体とした小規模で経済的な新しい積分形アナログ入力装置を開発した。これの特徴をまとめると、

(1) 多種多様の互いに絶縁された入力信号を高精度に扱える。

図9 商用周波ノイズ除去特性

図 10 積分形アナログ入力装置の入出力特性例

- (2) ノイズリジェクションが大きく、特別な場合を除いて入力 フィルタが不用であり使いやすい。

- (3) 積分形としては走査速度が速い。

- (4) 経済的なビルディングブロック実装方式になっている。

- (5) 小形で信頼性が高い。

などである。今後多様化にマッチしてじゅうぶんその性能を発揮するものと信ずる。

#### 参 考 文 献

- (1) 森田ほか: 日立評論 51, 153 (昭 44-2)

- (2) 特公昭 42-25090

- (3) 平井, 大沢: OHM 51, 58 (昭 39-6)

- (4) 加藤, 二橋: 電学東京支部大会 44 (昭 44-10)