# 16ビットDMAC(ダイレクトメモリアクセスコントローラ)"HD68450"

# 16 Bit DMAC (Direct Memory Access Controller) "HD68450"

マイクロコンピュータに対する高機能化・高性能化に対するユーザー要求は増大する一方であり、16ビット更には32ビットマイクロプロセッサも使われ始めてきた。ここで、日立製作所ではその周辺のキーデバイスであるDMAC "HD68450"を製品化し、8MHzクロック時2M語/秒という高速転送を実現した。16Mバイトという広いアドレス空間で効率の良いデータ処理を可能とするため、連続ブロック転送、メモリーメモリ間転送など多様な転送モードをもつとともに、例外処理などシステム信頼性向上のための配慮も十分行なっている。また、アーキテクチャ上は階層論理構造を採用し、設計効率向上を図った。

御法川和夫 \* Kazuo Minorikawa 上野達彰 \* Tatsuaki Ueno 三村芳人 \* Yoshito Mimura 中島 裕 \*\* Yutaka Nakajima

## □ 緒 言

マイクロコンピュータの応用範囲が広がるにつれ、16ビット/32ビットデータ処理、高級言語サポートなど、今まで以上に高い性能・機能が要求されてきた。日立製作所では、この動きに対応して16ビットマイクロコンピュータHMCS68000ファミリデバイスを開発している。図1にシステム構成を示す。HMCS68000は、HD68000MPU (Micro Processing Unit)を中心に、HD68450DMAC (Direct Memory Access Controller)、その他の周辺LSIから構成され、オフィスオートメーション、通信システム、インテリジェント端末、産業用制御装置など、多量なデータの高速処理を必要とする分野に最適である。ここでデータブロックの高速転送機能は必須のものと考えられるが、このたび日立製作所では、HD68450DMACを開発したので紹介する。

#### HD68000 MPU $A_1 \sim A_{23}$ 論理アドレス $D_0 \sim D_{15}$ データ メモリ管理 ユニット メモリ 理 HMCS68000 P 周辺コントローラ HMCS6800 周辺LSI HD68450 DMAC マルチプロセッサ 注:略語説明 インタフェース MPU(Micro Processing Unit) DMAC(Direct Memory Access Controller) 他のHD68000

図 I HMCS68000システム構成 HD68000 MPUを中心にして、8ビット周辺、16ビット周辺、HD68450 DMACなどにより高性能システムを構成できる。

# 2 HD68000の機能<sup>1)</sup>

まず、HD68450DMACの機能と密接に関係するHD68000 MPUの特長と仕様概要を表 1 に示す。レジスタは32ビットから成り、ビット、BCD(Binary Coded Decimal)、バイト、ワード、ロングワードのデータを扱える。また、そのデータ転送は非同期確認方式のほか、Enable信号による同期方式も可能で、8 ビットHMCS6800周辺LSIと直接インタフェースできる。

アドレスバスは23ビットから成り、16Mバイトのメモリ空間をリニアアドレシングできる。ここで周辺デバイスは、メモリと同一アドレス空間に配置される。

更に、強力な割込機能をもっているほか、ファンクションコードを使ったメモリ空間分離によるプログラム保護や、リトライ、アドレスエラー、バスエラー処理機能などによって

表 I HD68000 MPUの特長と仕様概要 16ビットMPUというより、 32ビットMPUのアーキテクチャと機能をもっている。

| 項目        | 仕様                                                                      |  |  |  |

|-----------|-------------------------------------------------------------------------|--|--|--|

| クロック周波数   | HD68000-10(10MHz), HD68000-8(8MHz),<br>HD68000-6(6MHz), HD68000-4(4MHz) |  |  |  |

| 基本命令数     | 56                                                                      |  |  |  |

|           | データレジスタ 32ビット×8                                                         |  |  |  |

| 内部レジスタ    | アドレスレジスタ 32ビット×7                                                        |  |  |  |

|           | スタックポインタ 32ビット×2                                                        |  |  |  |

|           | プログラムカウンタ 32ビット×I                                                       |  |  |  |

|           | ステータスレジスタ I6ビット×I                                                       |  |  |  |

| アドレシングモード | 14種                                                                     |  |  |  |

| アドレススペース  | 16Mバイト                                                                  |  |  |  |

| 処理データ単位   | 1, 4, 8, 16, 32ビット                                                      |  |  |  |

| 処 理 速 度   | レジスタ間加算 0.5μs<br>メモリーレジスタ間乗算 9.75μs                                     |  |  |  |

|           | 7レベルの割込み                                                                |  |  |  |

|           | トラップ                                                                    |  |  |  |

| エクセプション処理 | トレース                                                                    |  |  |  |

| •         | バスエラー、アドレスエラー                                                           |  |  |  |

|           | 不当命令 ほか                                                                 |  |  |  |

| 動作状態      | スーパバイザ状態/ユーザー状態                                                         |  |  |  |

|           | マルチプロセッサ機能                                                              |  |  |  |

| そ の 他     | HMCS6800周辺LSIインタフェース機能                                                  |  |  |  |

|           | 64ピンデュアルインラインセラミックパッケージ                                                 |  |  |  |

<sup>\*</sup> 日立製作所武蔵工場 \*\* 日立製作所半導体事業部

信頼性の高いシステムを構成できるように考えられている。

HMCS68000システムのキーデバイスであるHD68450DMACは、これらの基本思想に合わせて仕様決定、設計がなされている。以下、その詳細について述べる。

#### B HD68450 DMACの機能2)

#### 3.1 LSI概要

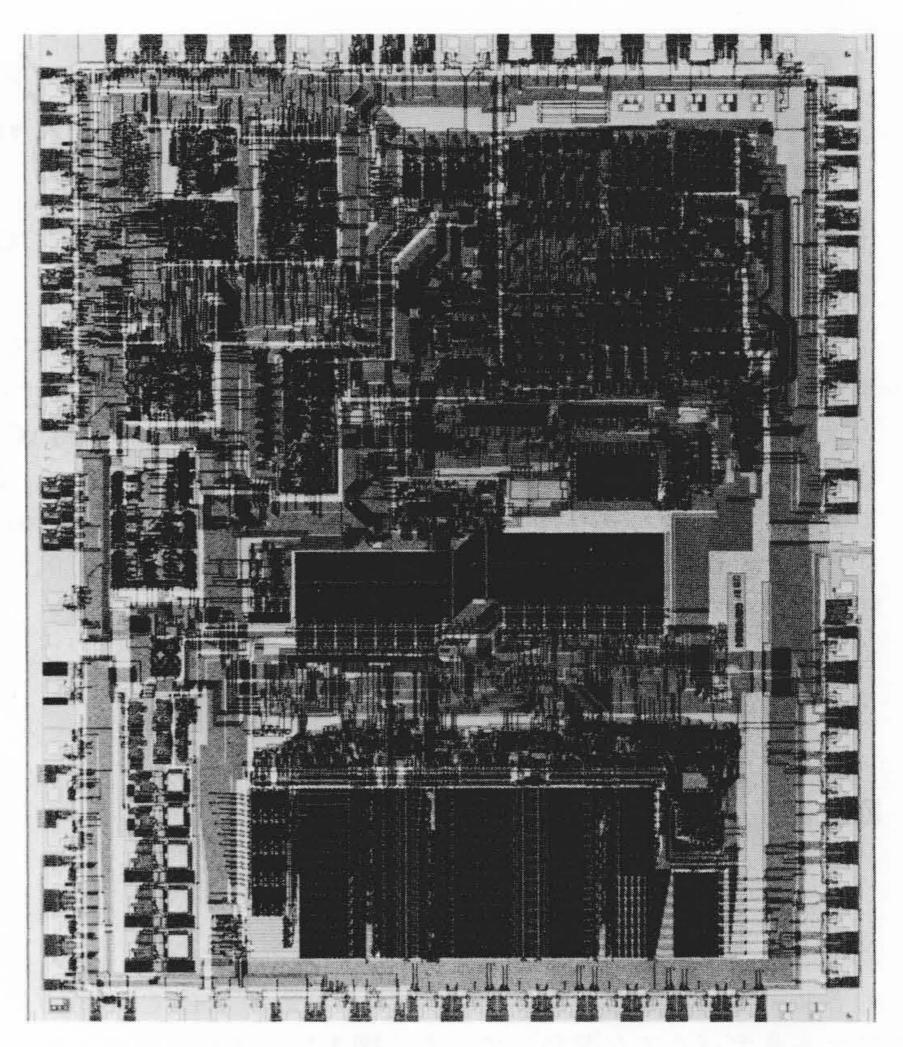

図2にチップ写真を示す。  $3 \mu m$  NMOS(NチャネルMetal Oxide Semiconductor)プロセスを使い, $7.5 mm \times 9 mm$ のチップ上に約4万トランジスタを集積し,高機能・高性能DMACを実現した。外部クロック8MHz時の最大転送速度は2 mm (4 mm/ト)/秒である。 $64 \ell mm$ 0DIL(Dual In Line)パッケージに収められ,その消費電力は1.3 mm1、2 mm2 である。

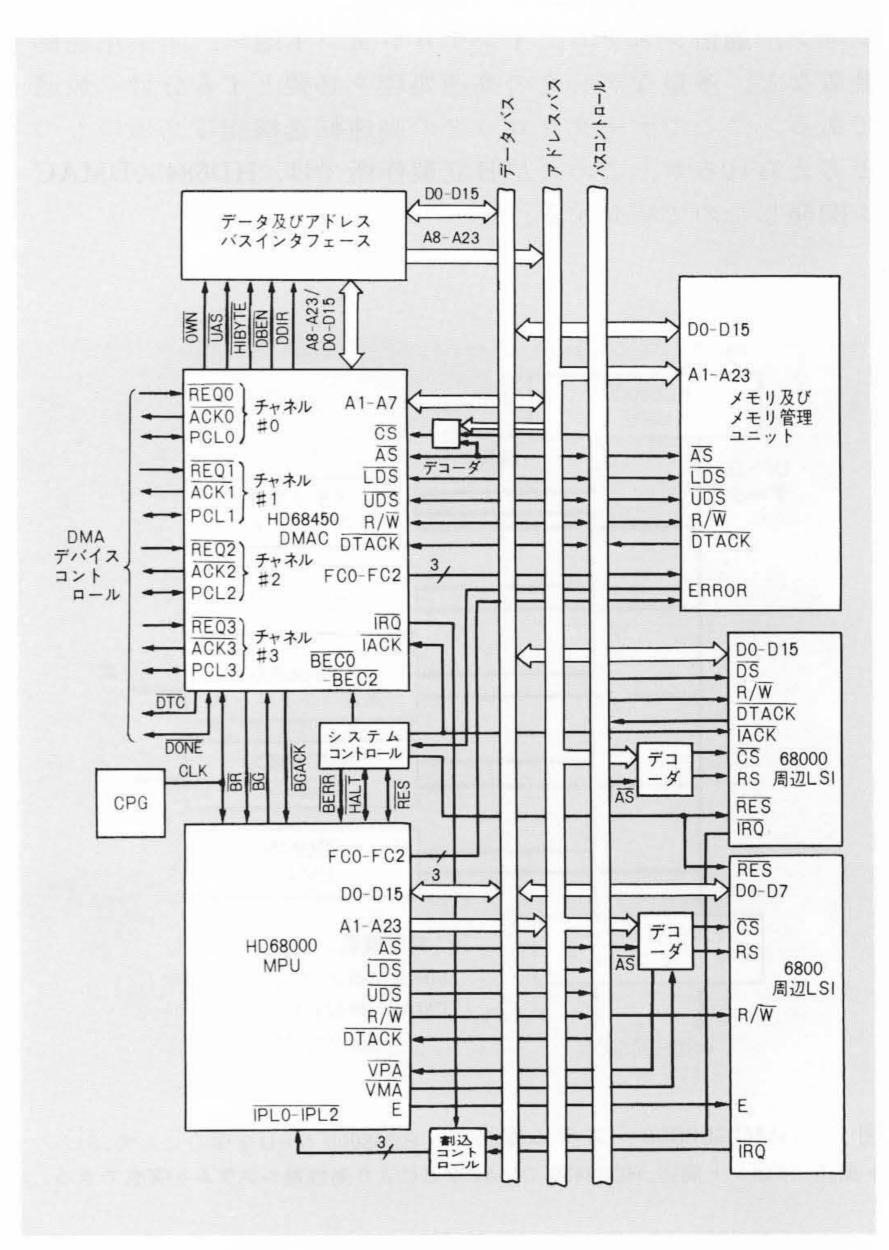

表2にHD68450の特長と仕様概要を、また図3にシステム 構成図を示す。四つの独立したチャネルをもち、その間の優 先レベルはプログラマブルである。オペランドとしてはバイト(8ビット)、ワード(16ビット)、ロングワード(32ビット) を扱える。更に16Mバイトのメモリ空間を直接アドレシングできること、68000の非同期バスによるDMAはもちろんのこと8ビットHMCS6800周辺LSIとのEnable同期方式のDMA (Direct Memory Access)も扱うことができること、メモリ管理を行なうためのファンクション情報を与えることなど、HMCS68000システムの考え方をそのまま採り入れている。また、バスエラーやホルト処理の機能、リトライ機能など信頼性の高いシステムを作り上げられるように考慮している。以下、その詳細機能について説明する。

#### 3.2 信号の機能

HD68450の内部状態としては、「MPUモード」(MPUがHD 68450をチップ選択し、アクセスしている状態)、「DMAモード」(このHD68450がバスの所有権を維持している状態)、「IDLE モード」(そのどちらでもない状態)の3種類がある。本DMACでは、これらのモードにより信号線の機能を使い分けて、ピンネックを解消し、64ピンDILパッケージに収めている。

表3に信号の種類と機能についてまとめる。

表 2 HD68450 DMACの特長と仕様概要 16Mバイトという大きなアドレス空間上で、効率の良いブロック転送を行なえるように多様な転送モードをもっている。

| 項目       | <b>社</b>                                                                                                                            |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| クロック周波数  | HD68450-8(8MHz), HD68450-6(6MHz),<br>HD68450-4(4MHz)                                                                                |  |  |  |  |

| チャネル数    | 4 チャネル                                                                                                                              |  |  |  |  |

| アドレススペース | 16Mバイト                                                                                                                              |  |  |  |  |

| 転送データ    | バイト(8ビット), ワード(16ビット),<br>ロングワード(32ビット)                                                                                             |  |  |  |  |

| 最大転送速度   | 2 M語/秒(クロック周波数 8 MHz時)                                                                                                              |  |  |  |  |

| 転 送 機 能  | メモリ〜I/Oデバイス間転送, メモリ〜メモリ間転送<br>ノーコンティニュー/コンティニューモード<br>アレイチェイン/リンクチェインモード<br>外部リクエスト/オートリクエストモード<br>サイクルスチール/バーストモード,<br>カウントアップ/ダウン |  |  |  |  |

| そ の 他    | ホールト機能 バスエラーなど各種エラー処理機能 リトライ機能,プログラマブル優先順位 HMCS6800周辺LSIインタフェース機能 64ピンデュアルインラインセラミックパッケージ                                           |  |  |  |  |

図 2 HD68450 DMACチップ 7.5mm×9mmのチップ上に約4万トランジスタを集積し、高機能・高性能を達成している。

図3 HD68450 DMACの外部結線 MPUと同一のバスインタフェースをもち、最大 2 M語/秒のオペランド転送を実現している。

表 3 信号の種類と機能 モードによって信号を使い分け、多機能を実 現している。

| 信号                                                               | 入出力                        | 機能                                                                                                                      |  |  |  |  |  |

|------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CS (Chip Select)                                                 | In                         | 他のバスマスタ(MPU, 他のDMACなど)がこの入力をフサートして、DMACの内部レジスタをプログラムする。<br>自分自身が選択した場合は、アドレスエラーとして内部レジスタを保護する。                          |  |  |  |  |  |

| A8/D0-A23/D15<br>(Address/Data)                                  | In/Out                     | 時分割でアドレス出力、データ入出力に使う。このデマルチプレックスはDDIR、DBEN, UAS, OWN信号を使って外部回路で行なう。                                                     |  |  |  |  |  |

| AI-A7 (Address)                                                  | In/Out                     | MPUモードでは、この端子は入力となってDMACの内部<br>レジスタ選択に使われる。DMAモードのバスサイクルでは、メモリ又は周辺デバイスをアクセスするためのア<br>レスを出力する。                           |  |  |  |  |  |

| FC0-FC2<br>(Function Code)                                       | Out                        | DMAバスサイクル時に、ファンクションコードレジスタの内容を出力する。                                                                                     |  |  |  |  |  |

| AS (Address Strobe)                                              | In/Out                     | MPUモード、IDLEモードでは入力になっており、DM 要求中でBGがアサートされているとき、絶えずAS信意をデートをモニタしてバスマスタになる時期を待つ。方、DMAモードでは出力となり、アドレス出力が確定たことを示す。          |  |  |  |  |  |

| UAS<br>(Upper Address Strobe)                                    | Out                        | マルチプレクスされているA8/D0-A23/D15上のアドレス情報をラッチするための信号                                                                            |  |  |  |  |  |

| OWN (Own)                                                        | Out                        | 本DMACがDMAモードであることを示す出力。双方向性バッファの制御を行なう。                                                                                 |  |  |  |  |  |

| DDIR<br>(Data Direction)                                         | Out                        | データバスの双方向性バッファの入出力切換を行なう                                                                                                |  |  |  |  |  |

| DBEN<br>(Data Bus Enable)                                        | Out                        | マルチプレクスされたA8/D0-A23/D15上にデータがっていることを示す。                                                                                 |  |  |  |  |  |

| HIBYTE<br>(High Byte)                                            | Out                        | バイトサイズのデータが上位 8 ビットデータバス上に<br>ることを示す。                                                                                   |  |  |  |  |  |

| UDS (Upper Data Strobe) LDS (Lower Data Strobe) R/W (Read Write) | In/Out<br>In/Out<br>In/Out | 68000MPUと同種の信号<br>MPUモードでは入力, DMAモードでは出力                                                                                |  |  |  |  |  |

| DTACK (Data Transfer<br>Acknowledge)                             | In/Out                     | 68000MPUと同種の信号<br>MPUモードでは出力, DMAモードでは入力                                                                                |  |  |  |  |  |

| BEC0 - BEC2<br>(Bus Exception Control)                           | In                         | 例外処理要求入力                                                                                                                |  |  |  |  |  |

| BR (Bus Request) BG (Bus Grant) BGACK (Bus Grant Acknowledge)    | Out<br>In<br>In/Out        | 68000MPUと同種の信号<br>バスマスタ権の受け渡しに使う。                                                                                       |  |  |  |  |  |

| IACK<br>(Interrupt Acknowledge)                                  | In                         | 現在のバスサイクルがインタラプトアクノレッジサイクルであることを示すMPUからの出力信号<br>DMACはこの信号を受けて、割込要求した最優先チャネルのノーマルインタラプトベクタ又はエクセプションインタラプトベクタをデータバスへ出力する。 |  |  |  |  |  |

| REQ0-REQ3<br>(Channel Request)                                   | In                         | 外部デバイスからのDMA要求入力                                                                                                        |  |  |  |  |  |

| ACK0 — ACK3<br>(Channel Acknowledge)                             | Out                        | DMA要求を出した外部デバイスにDMAサイクルを始める<br>ことを知らせる。                                                                                 |  |  |  |  |  |

| PCL0-PCL3<br>(Peripheral Control)                                | In/Out                     | 割込要求入力、アポート入力、%クロック出力など多目的に使えるプログマバブル端子                                                                                 |  |  |  |  |  |

| DONE (Done)                                                      | In/Out                     | 一つのDMA要求に対するチャネル動作の終了を示す。                                                                                               |  |  |  |  |  |

| DTC (Device Transfer<br>Complete)                                | Out                        | データ転送するたびに、その終了を外部デバイスへ知ら<br>せる。                                                                                        |  |  |  |  |  |

#### 3.3 レジスタ

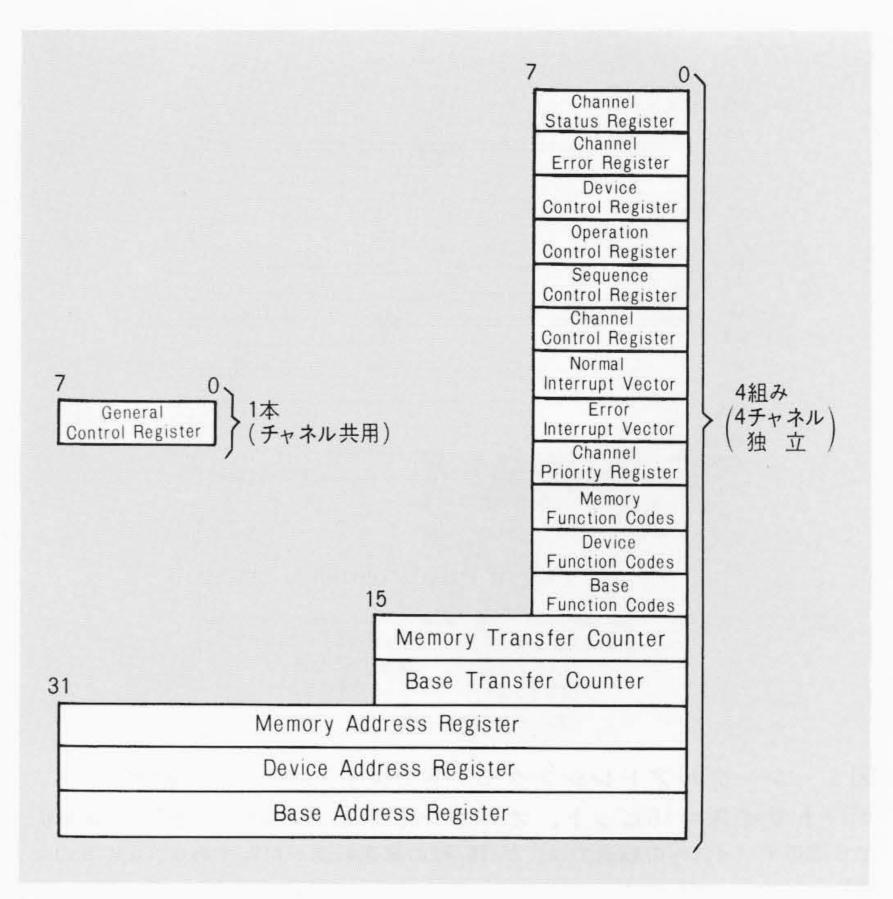

HD68450は図4に示す69本のレジスタを内蔵している。各 種機能をプログラムするためのコントロールレジスタ, チャ ネル情報やエラー情報を示すステータスレジスタ, ファンク ションコードを記憶しておくファンクションコードレジスタ, アドレスレジスタ, 転送語数レジスタなどから構成されてい る。転送語数レジスタ(トランスファカウンタ)は16ビットか ら成り、1データブロックの大きさとして最大64k語とれる。 また、アドレスレジスタは32ビットとして、将来への拡張性

HD68450 DMAC内部レジスタ アドレスレジスタは既に32ビッ トで構成されていて、将来拡張できるようになっている。

表 4 転送モードの組合せ 意味のある組合せは、すべて可能である。

| アドレシング<br>モ – ド | デバイス<br>タ イ プ       | デバイス<br>ポ ー ト<br>サ イ ズ | オペランドサイズ |     |            |                       |

|-----------------|---------------------|------------------------|----------|-----|------------|-----------------------|

|                 |                     |                        | バイト      | ワード | ロング<br>ワード | DMA要求                 |

| デュアル            |                     | 8ビット                   | 0        | 0   | 0          | 外部要求,<br>ソフトウェア<br>要求 |

|                 | 68000<br>又は<br>6800 | 16ビット                  | 0        | 0   | 0          | ソフトウェア<br>要求          |

|                 |                     | 16ビット                  | ×        | 0   | 0          | 外部要求                  |

| シングル            | ACK<br>又は           | 8ビット                   | 0        | ×   | ×          | 外部要求,<br>ソフトウェフ<br>要求 |

|                 | ACK and Ready       | 16ビット                  | ×        | 0   | ×          |                       |

をもたせてある。現在はこのうちの24ビットだけ使用して いる。

#### 3.4 転送モード

HD68450は16Mバイトという大きなアドレス空間をもち, 8ビット周辺、16ビット周辺の混在する複雑なシステム上で も効率良くデータ転送が行なえるように、種々の転送モード をもっている。表4に転送モードを示す。メモリサイズは常 に16ビットであると仮定している。一方、オペランドサイズ (一つの転送要求に対して転送するデータの大きさ)としては バイト(8ビット), ワード(16ビット), ロングワード(32ビッ ト)が可能であり、また、ポートサイズ(1バスサイクルで転 送可能なデータ幅)も8ビット、16ビットの二とおりある。転 送シーケンスとしてはメモリだけをアドレスし、周辺デバイ スは固定して考えるシングルアドレシングモードとメモリと 周辺デバイス両方共アドレスするデュアルアドレシングモー ドがある。

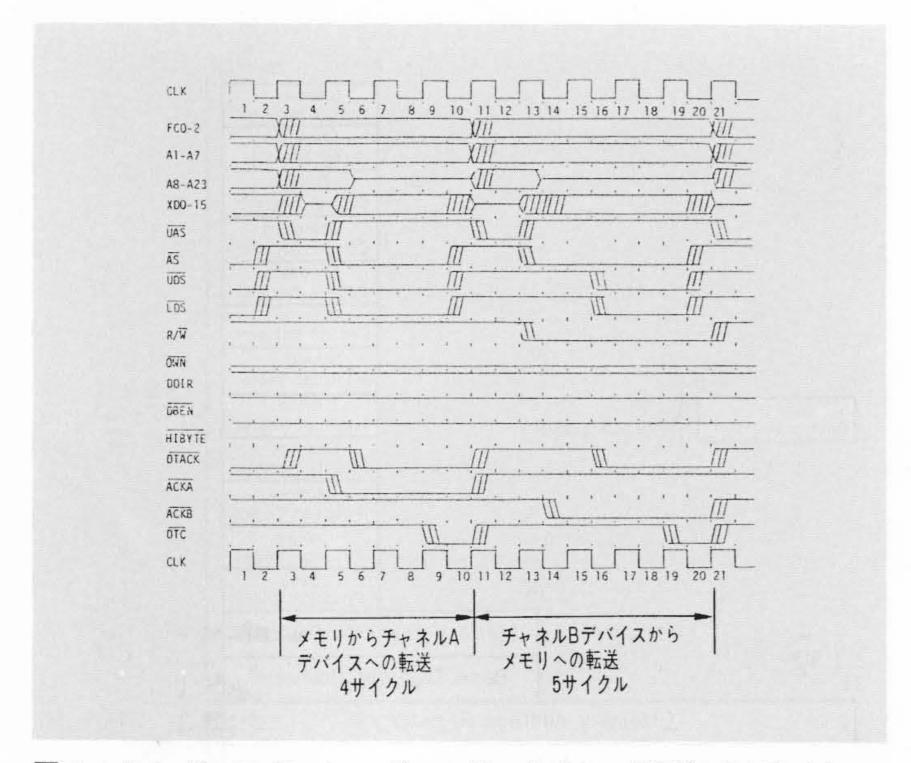

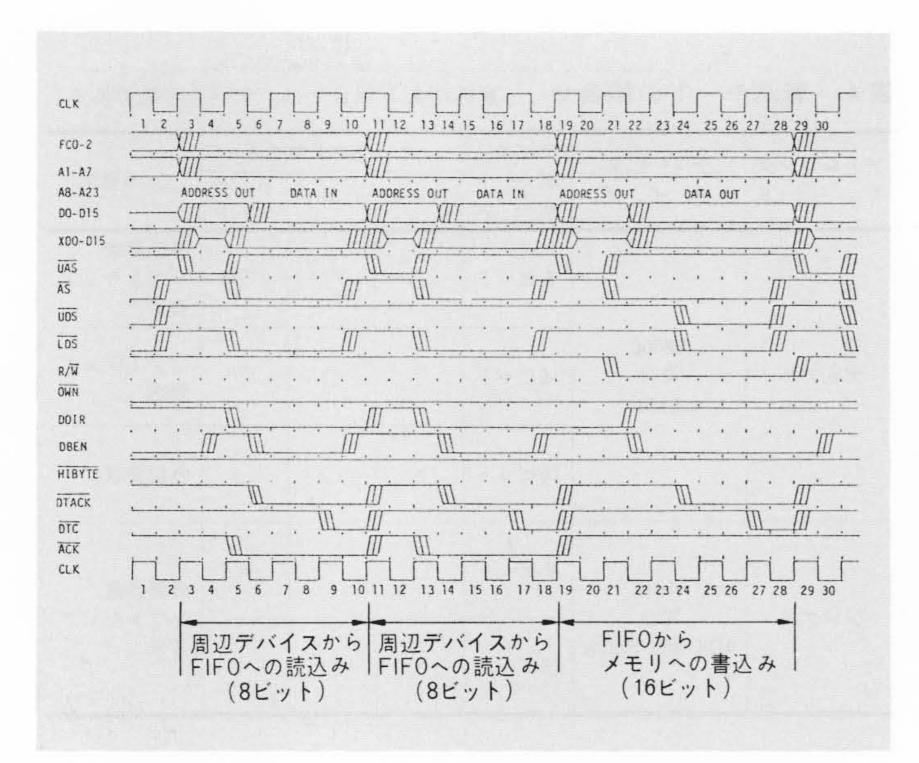

図 5 シングルアドレシングモードのタイミング例(ACKデバイス,ポートサイズ=16ビット,オペランドサイズ=16ビット) メモリから周辺デバイスへの転送では、2M語/秒の高速転送が可能である(CLK 8MHz時)。

図 6 デュアルアドレシングモードタイミング例(ソース:8ビット 周辺, デスティネーション:メモリ) DMACに内蔵されたFIFOレジ スタを使って, データのパック, アンパックも行なえる。

# (1) シングルアドレシングモード

このモードはDMACのFIFO(First In First Out)の介在なしに、メモリと周辺デバイス間で直接データ転送を行なう。ポートサイズとオペランドサイズの等しい場合に使え、1 バスサイクルで1 オペランドの転送を行なう。図5 にタイミング図を示す。最大転送速度はメモリから周辺デバイスへ転送するとき、2 M語/秒(クロック周波数8 MHz時)である。このモードには $\overline{ACK}$ 信号を使う方式と $\overline{ACK}$ と $\overline{READY}$ [PCL(Peripheral Control Lines)入力を使用]信号を使う方式の2 種ある。スピードの遅い周辺デバイスを使う場合には、 $\overline{READY}$ 信号を使うことによって、 $\overline{DMAC}$ を待たせることができる。

## (2) デュアルアドレシングモード

メモリとアドレシングを必要とする他のデバイスとのデータ転送を行なう。この転送はDMAC内蔵のFIFOレジスタを介して行なわれる。すなわち、1本のアドレスバスを使ってメモリ及び他のデバイス両者をアドレスする必要があるので、データ転送をメモリーDMAC、DMAC一他のデバイスというように2回に分けて行なう。この方式ではメモリーメモリ間転送のほか、ポートサイズの異なるデバイス間のデータ転送もFIFOを使ってのデータフォーマット変換により可能にしている。図6にそのタイミング例を示す。

#### (3) 複数ブロックの転送

複数ブロックの連続転送を行なわせる方法として、コンティニュー、アレイチェイン、リンクドチェインの三つがある。コンティニューモードでは、次のブロック転送情報をベースアドレスレジスタ、ベーストランスファカウンタ、ベースファンクションコードレジスタにあらかじめセットしておき、一つのブロック転送が終わると、それらがメモリアドレスレジスタ、メモリトランスファカウンタ、メモリファンクションコードレジスタへ移されて、次のブロック転送を続けて行なう。

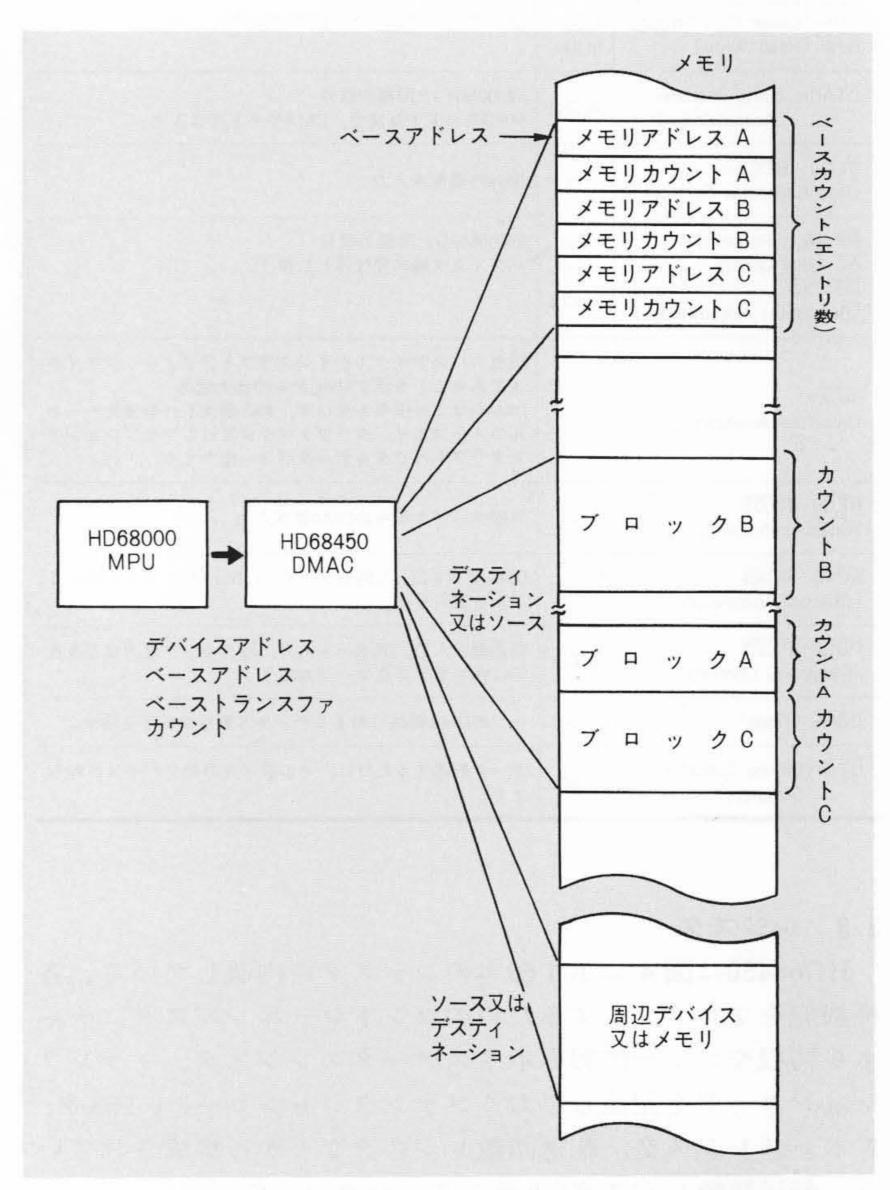

アレイチェインモードでは、**図7**に示すようにメモリアドレスとトランスファカウント情報をメモリ内にアレイとして格納しておき、このアレイの先頭アドレスをベースアドレスレジスタ、エントリ数をベーストランスファカウンタへ入れておく。DMACは一つのブロック転送前にまずこのアレイ情

図7 アレイチェイン転送 アレイ状に並べられた転送情報に基づいて、 分散しているオペランドブロックの連続転送を行なう。アレイの先頭アドレス とエントリ数はあらかじめMPUから与えられる。

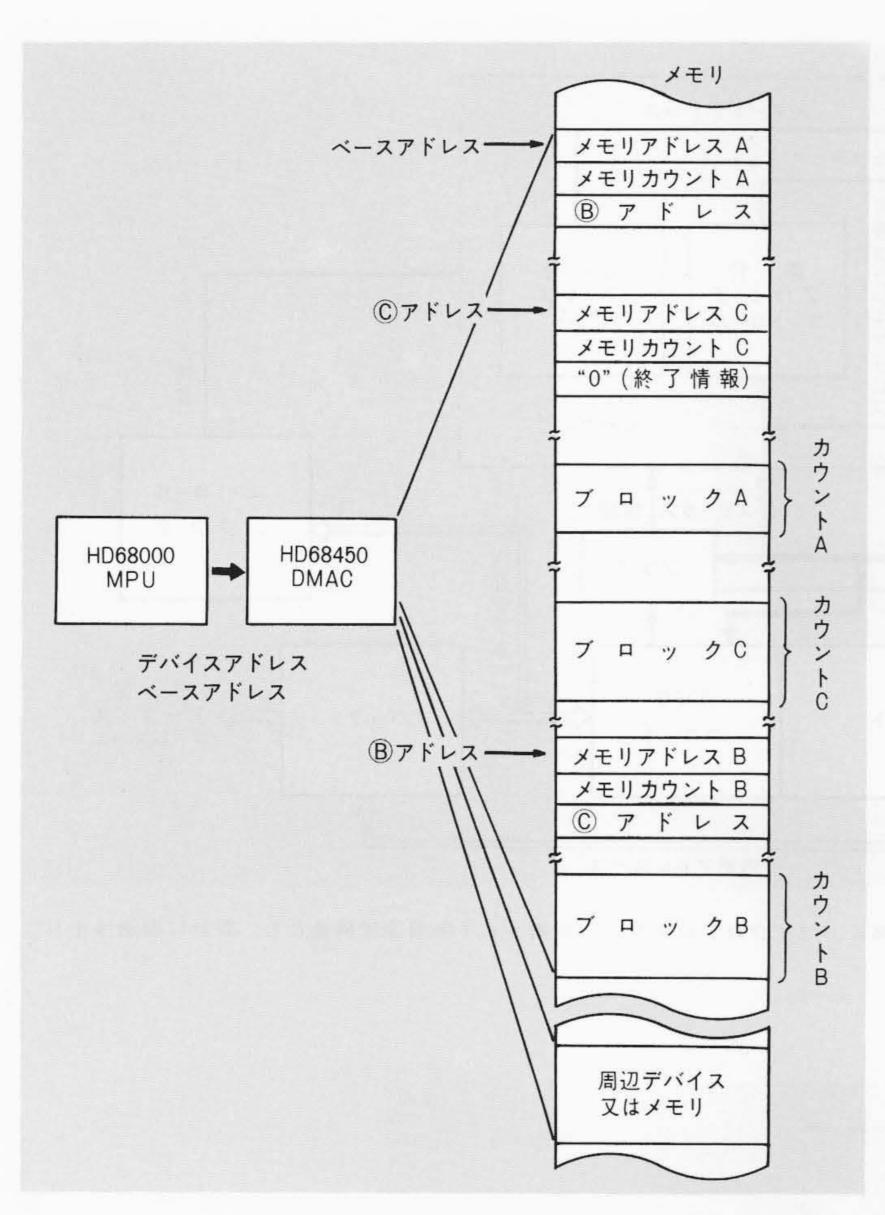

リンクドチェイン転送 リンクアドレスもメモリ内に与えられる ので, ブロックの挿入, 削除を容易に行なえる。

報をフェッチし、その後転送を開始する。ここでベーストラ ンスファカウンタが0になったらアレイチェインは終了する。 リンクドチェインモードでは、図8に示すようにメモリ内 にリンクアドレス情報ももつ。このリンクアドレスで毎回べ ースアドレスレジスタを書き変えるので、オペランドブロッ クの削除, 挿入が, アレイ情報の再構成をすることなく可能 である。このチェイニングはリンクアドレスが0になると終 了する。

#### (4) その他

DMA転送要求の方法としては、REQ信号による外部要求 のほか、メモリーメモリ間転送のように外部に起動をかける デバイスがない場合に、ソフトウェアでスタートをかける方 法がある。更に,一つの転送要求に対してオペランドのブロ ック転送を連続して一気に行なうバーストモード, 一つの転 送要求が入るごとに1個のオペランド転送を行なうサイクル スチールモードがある。その他、MPUサイクルとDMAサイ クルのバス占有比率についてもプログラムできるなど, 多様 な転送モードの組合せが可能で、各応用システムに最適の転 送方式が選択できる。

#### 3.5 例外処理

HD68450は例外処理要求用の端子 BEC0~BEC2 をもつ。 外部でパリティエラーなどを検出した場合は、 リトライやバ スエラー処理を行なわせることができる。また、バスをいっ たん解放させてからリトライさせることもできる。更に、ホ ルト機能をもち、システムデバッグを容易に行なえる。この ようにHD68000MPUと合わせて、信頼性の高いシステムが構 成できるよう考慮した。

#### 3.6 その他の機能

エラー情報はチャネルエラーレジスタにアドレスエラー, バスエラー, カウントエラー, アボートのほか, コンフィギ ュレーションエラー、オペレーションタイミングエラーも表 示され、プログラムミスなどのエラー要因解析も容易である。 各チャネルはチャネルプライオリティレジスタをもち、レベ ル 0 (最優先)からレベル 3 までプログラムできる。同一プラ イオリティの場合は、ラウンドロビン方式で優先順位が決め られる。

#### 4 HD68450 DMACの設計

HD68450では既に述べたように、高機能16ビットマイクロ コンピュータ応用システムに対応するため、従来の8ビット DMACと比べて極めて高機能な仕様を実現した。その集積度 は8ビットDMAC HD6844の約8倍である。この複雑な機能 をもつDMACの設計に当たり、その設計を容易にし融通性を 確保するため、内部制御方式としてマイクロプログラム制御 方式を採用し、更に、各機能ブロックの独立性を高くし制御 機能を分割して、階層論理構造とした。また、マイクロプロ グラム設計に際しては、マイクロプログラムアセンブラを開 発して設計効率向上を図った。以下, その設計概要について 述べる。

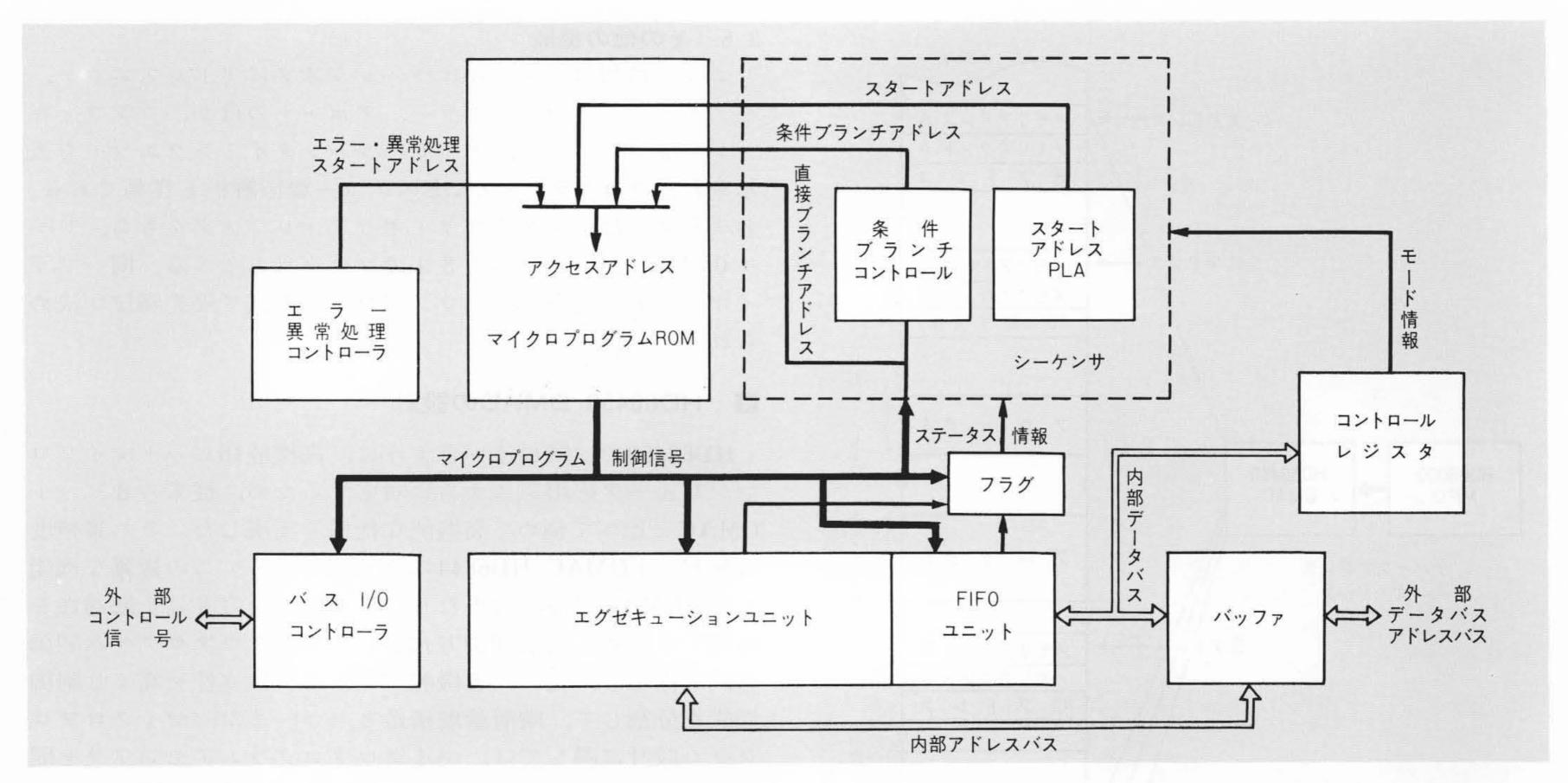

#### 4.1 DMACの内部動作

HD68450は、基本方式設計の段階で内部機能を図9に示す 機能ブロックに分割し、各々のブロックをマイクロプログラ ムで制御するようにした。これにより論理構造は簡素化され、 論理設計をブロックごとに並行して進めることができた。ま た, 仕様変更に対してはプログラム変更で対処でき, 融通性 を極めて高くできた。

ここでその基本動作について説明する。シーケンサがこれ から実行すべきルーチンの先頭アドレスを出力する。そのア ドレスで指定されたマイクロプログラムROM (Read Only Memory)の出力信号が被制御部へ伝えられ、命令が実行され る。出力の一部はシーケンサへフィードバックされ、次のマ イクロプログラムステップのアドレス情報となる。このよう にしてシーケンス終了信号が読み出されるまで, マイクロプ ログラム実行が繰り返えされる。各ブロックの機能は次に述 べるとおりである。

#### (1) エグゼキューションユニット

アドレスレジスタ, ファンクションコードレジスタ, トラ ンスファカウンタ、インタラプトベクタレジスタ及びALU(演 算ユニット)から成り、転送先アドレスや転送オペランド数の 計算を行なう。

#### (2) FIFOユニット

オペランド転送時に使われる一時記憶バッファである。転 送オペランド単位には8ビット、16ビット及び32ビットの3 種類あるが、メモリ16ビット、データ8ビットのようにポー トサイズが異なる場合のオペランドの統合, 分割はこのユニ ットで行なう。

#### (3) バスI/O(入出力)制御

バス制御信号の発生と制御

#### 4.2 マイクロプログラム

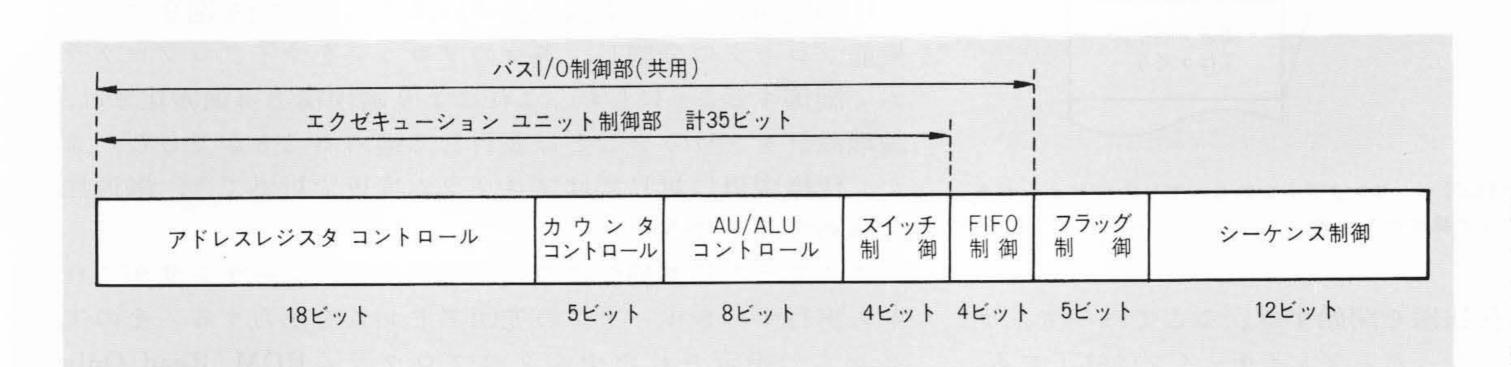

マイクロ命令のフォーマットを図10に示す。HD68450では 横形のマイクロ命令制御とし、エグゼキューションユニット 制御に35ビットを割り当てた。これは1バスサイクル(1デー タの転送サイクル)の最小時間500nsの中では2ステップのマ イクロ命令実行しか許されないので、1マシンサイクル250ns

図 9 HD68450 DMACの機能ブロック図 各機能ブロックは独立度が高く、マイクロプログラムで制御される階層論理構造とし、設計に融通性をもたせた。

図10 マイクロ命令フォーマット 横形のマイクロ命令として同時に複数動作をさせることによって、高速化を図った。

中に複数の処理を可能にして効率を上げるためである。一方、FIFOユニットは高速の判断機能を必要とするため、専用のシーケンス制御回路をもたせ、マイクロ命令としては4ビットのシーケンス起動命令だけを与えて、後の動作はFIFOユニットに任せる方式とし、バスI/O制御ユニットも同様の方式とした。

マイクロプログラムの読出しと実行はパイプライン制御を行ない、実行効率を向上させた。すなわち、連続DMA転送の際は前のオペランド転送実行中に次のオペランド転送制御用のマイクロ命令読み出しを行ない、前のオペランド転送が終了したところで次のオペランド転送要求の有無を確認して、既に読み出されているマイクロ命令実行の可否を決定するようにした。

以上、マイクロプログラムと各プロックの制御分担の最適化を行なうと同時に、各種動作シーケンスの共通化をも進め、結局マイクロプログラムは178ステップに収めることができた。

# 4.3 マイクロプログラムアセンブラ

LSI設計と並行して、設計サポートツールとしてのマイクロプログラムアセンブラを開発した。このアセンブラ出力としては、LSIレイアウトデータのほかに計算機論理シミュレータ用データ及びブレッドボード用EPROMの紙テープ出力が得られる。これにより、プログラムミスの大幅低減とデバッグ効率向上ができた。

# 5 結 言

16 Mバイトの広い連続したメモリ空間を直接アドレシングでき、4 Mバイト/秒という高速データ転送を可能とする16 ビットマイクロコンピュータ68000用 DMAコントローラ HD 68450を製品化した。例外処理など信頼性に対する考慮も払っており、ユーザーの要求に十分こたえられるものであると確信している。

設計技術的には、マイクロプログラム制御方式、機能ブロック分割による階層論理構造を取り入れ、ソフトウェア、ハードウェアの併行設計を行なって設計効率化を図った。高集積化技術もますます進み、LSI設計技術も複雑化する一方であるが、この成果を今後の大規模論理LSI設計に生かしていきたい。更に今後は、RAM(Random Access Memory)、ROM、PLA(Programmable Logic Array)などのメモリ構造をもつ規則論理の多用やCAD/DA (Computer Aided Design/Design Automation)による設計効率向上、消費電力増大による熱発生の問題解消のためのCMOS化を強力に進める必要があると考えている。

# 参考文献

- 1) Semiconductor Data Book: 8/16 Bit Microcomputer (Mar. 1982 日立製作所)

- 2) Target Specification of HD68450 Direct Memory Access Controller (Sep. 1981 日立製作所)