# 日立鹽特許

## ポリSi負荷CMOSスタティックRAM

メモリの良し悪しを評価する大事なポイントは、何と言ってもアクセスタイム、消費電力、そして集積密度の3大要素であろう。これらの要素は相反作用が強く、あちらを立てればこちらが立たず困惑させられるものである。この発明では、3大要素をすべて満足させようと考えた。

### 1. 特長•効果

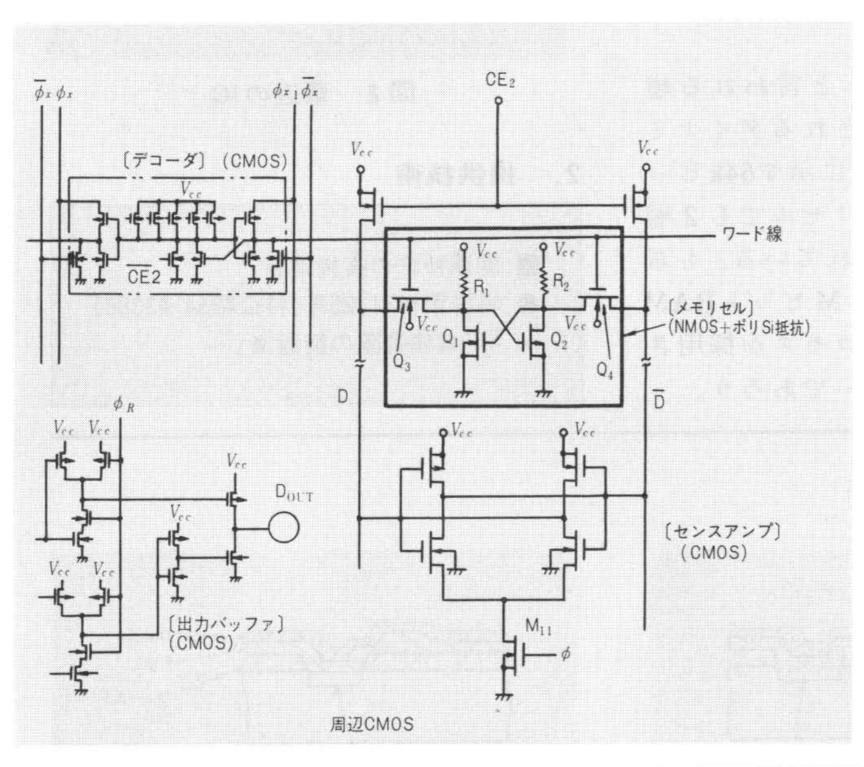

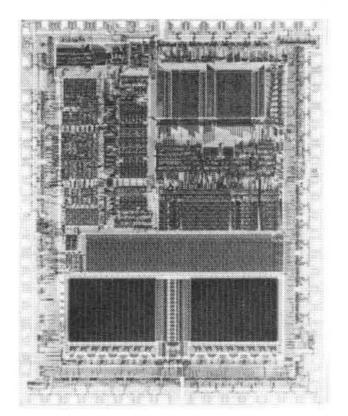

全体の回路は、メモリセルを多結晶Si(ポリ-Si)抵抗とNチャネルMOSF ETで構成し、センスアンプなどの周辺回路をCMOSFETでまとめた( $\mathbf{図1}$ )。

この回路では、CMOSのもつ高速性 (低SP積:遅延時間×消費電力)を十 分生かし、アクセスタイムに大きく影響する周辺回路の応答を速めている。 CMOSはICの中で比較的広い面積を必要とするが、大容量のメモリチップでは周辺回路の全体に占める場所が小さいため、メモリチップ全体の集積度にほとんど影響しない。一方、メモリマトリックスは大きな場所をとるので、数万個もあるメモリセルの1個1個は単チャネル MOSと電源ライン・抵抗部一体化ポリSiにより小形化し、大 容量化及びビット当たりのコストダウンを可能にした。また、CMOS及び高抵抗負荷は共に消費電力が少なく、両タイプの回路は3部門で見事に調和している。

比較的簡単に見えるこの発明には, 「CMOSチップはPMOSとNMOSを対 にした回路でこそ, その意味がある。」 という従来の既成概念を打破した生い 立ちがあり、CMOSプロセスでありな がら、単チャネル MOSと高抵抗の回路 がチップの大部分を占めることになる この発明は、ユニークであろう。日立 製作所では、このような技術に「Hi-C-MOS」と愛称を付け、4kビットから世 界に先駆けて採用, Electronics Apr. 26, 1979 P. 126, 同 Oct. 23, 1980 P. 115 では、"impressive part"、"extremely innovative processing and design", "a real challenge to n-MOS technology との第三者評価を受け、1979年にはI.R. 100を受賞した。64kビット以上のスタ ティック RAM 市場では主流技術となっ た。

### 2. 提供技術

■ 関連特許の実施許諾 特開昭54-14690 特開昭53-14586 特公昭57-23423

特公昭58-4459 ほか

図 I 本発明による CMOSスタティック RAM

## 折り返しビット線D-RAM

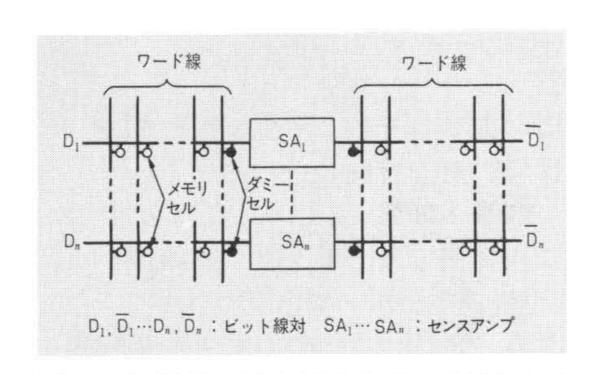

従来の $1\,\mathrm{MOS}$  ダイナミックRAMでは、 $\mathbf{Z}1$  に示すように、一対のビット線を差動形のセンスアンプを狭んでその両側にそれぞれ1 本ずつ配置していた。ちょうど、センスアンプを胴体に例えれば、左右の手(ビット線 $D_1$ , $\overline{D}_1$ )を一直線に広げた格好である。

このようなメモリセル配置では、ワード線を介してビット線に雑音がのると、その雑音がセンスアンプでそのまま増幅されるので、高集積化になるにつれてS/N比が大きな問題となってきた。1.特長・効果

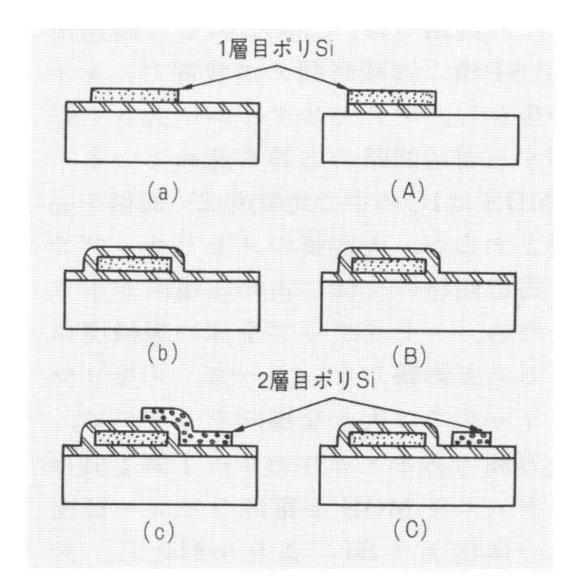

この発明では、図2に示すように、 差動形のセンスアンプの一方の側に一 対のビット線を平行に配置し、ビット 線 $D_1$ と $\overline{D}_1$ がセンスアンプのところで 折り返すようにした。ちょうど、両手 を前のほうに平行に伸ばした格好であ る。このような配置にすると、一つの

図 I 従来のIMOS ダイナミック RAMの 要部回路例

ワード線が、両方のビット線  $D_1$  と  $\overline{D}_1$  と 交差するレイアウトになるので、ワード線を介しての雑音は両方のビット線にほぼ等しくなるので、このような雑音は差動形のセンスアンプで相殺される。

D-RAM の高集積化に伴い、メモリセルから取り出される信号量はしだいに小さくなっており、日立製作所では64kビットからこのレイアウト方式を採

図2 本発明を実施したIMOSダイナミックRAMの要部回路

用,256kビットの市場ではこの方式が 主流となり,S/N比を向上させる上で 欠かせない技術となった。

### 2. 提供技術

- 関連特許の実施許諾

- 特許第1146400号(特公昭55-39073号,米国特許第4044340号)「半導体メモリ」

# 日立顯特許

## 2層ポリシリコン電極の形成法

### 1. 特徵•効果

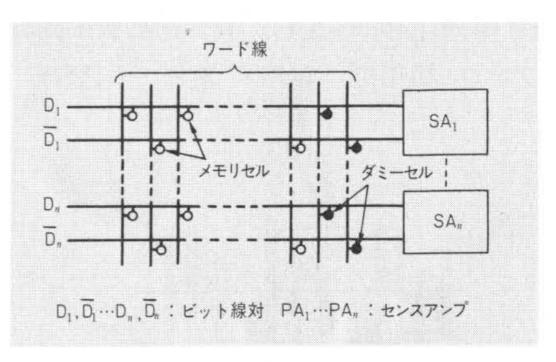

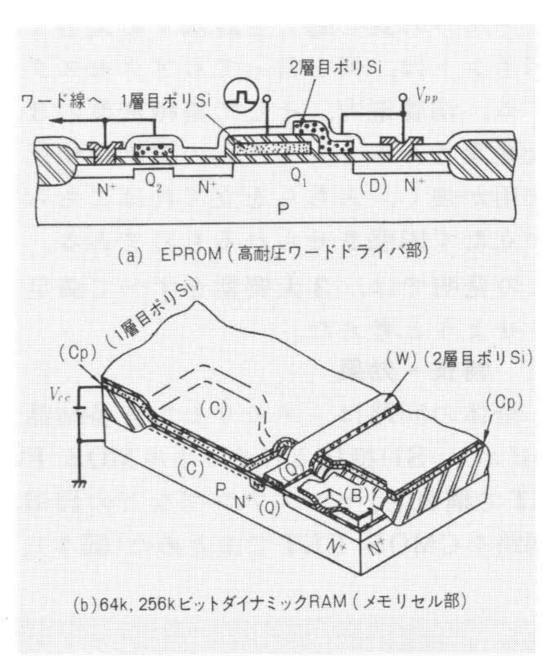

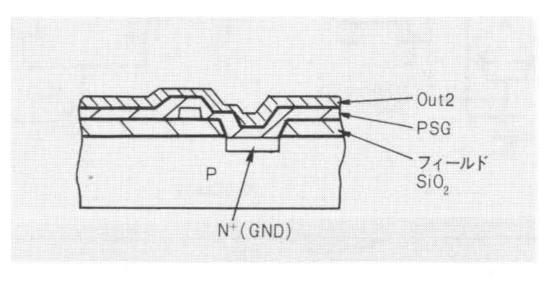

この2層ポリ(多結晶)Si電極は、図 1(a)~(c)に示すように, 1層目のポリ Siを酸化した後に2層目のポリSiをそ の上にまたがって形成するか, 又は同 図(A) $\sim$ (C)に示すように、1層目のポリ Siとその下のゲート酸化膜をパターニ ングしてから全面酸化 (第2ゲート酸 化)し、その後2層目のポリSiをデポ ジットすることによって作られる。こ の発明によれば、いずれのポリSi層も Si基板の薄い酸化膜上に形成されるた め, 共に基板表面の電界効果制御電極 とすることができる。また、両層を重 ね合わせて形成することによって、制 御電位の異なる制御電極を連続的に形 成することができる。

このような多層制御電極は、高集積化だけでなくバラエティに富んだ新しい素子構造をもたらした。その一つがCCD (Charge Coupled Device) であり、また、EPROMでは図2(a)に示すような高耐圧構造をもたらした。

図 | 本発明による2層ポリSi 電極の形成方法

さて、 $2\mu$ mから $1\mu$ mへと言われる超 LSI、その最先端と評されるダイナミックRAMでは、図2(b)に示す64kビット,256kビットのメモリセルでも2層のポリSi電極が採用されている。もちろん、次世代の超LSI1MビットRAMでもこのような製造プロセスが採用されることに変わりはないであろう。

図2 最近のIC

### 2. 提供技術

- 関連特許の実施許諾

- 特許第1081225号(特公昭54-43356)「半導体装置の製造法」

## シリコンゲート・マスクROM

MOS ICの製造方法はAlゲートプロセスとSiゲートプロセスの二つに大別される。

日立製作所では、CMOS標準ロジックの一部を除きSiゲートプロセスを全面的に採用し、そのプロセス技術開発をいち早く手掛けた。またAlゲートプロセスからの切換えも、電子式卓上計算機用LSIでMOSICが脚光を浴び始めた幼年期には既に業界で先駆け

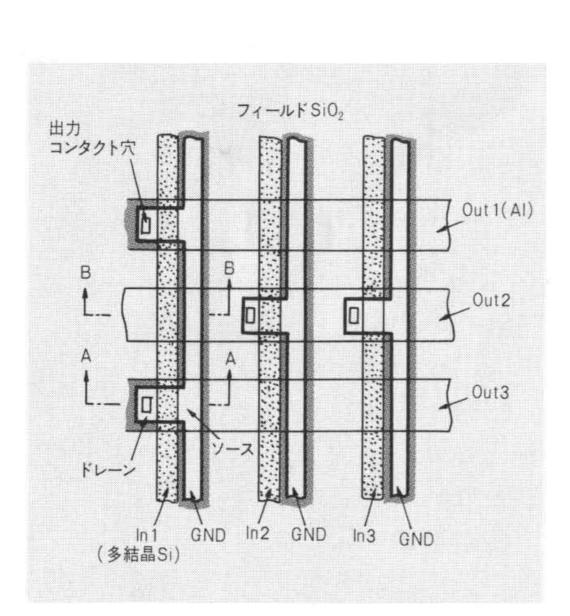

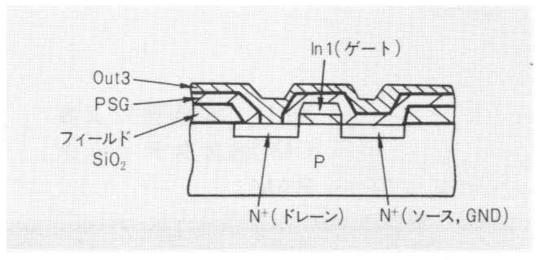

図 | 本発明によるマスク ROM の平面パターン図

(a) MOS Trs (A-A断面図)

(b) MOS Trs 無し (B-B断面図)

図2 図 I の要部断面図

て行なった。

この発明はそのころ生まれたSiゲート関係の有力特許の一つである。

### 1. 特長•効果

この発明では、"1"、"0"の論理パターンは、フィールド酸化膜のパターンで決まる。言い換えればフィールド酸化膜層の写真処理マスクで製造の途中段階で実質的な書き込みが行なわれる。マトリックス交点にトランジスタを作る場合(論理"1")は、図1に示すようにフィールド酸化膜の境界線(太線)が多結晶Si層の下を横切るようにパターンニングする。論理"0"の場合フィールド酸化膜の境界線は多結晶Siと交差しない。したがって、図2に示すように、論理"1"

の場合はドレーン領域が形成されるが、"0"の場合はドレーンが形成されない。

したがって、本発明によればSiゲートの基本プロセスを何ら変更しないでマスクROMを製造することができるので、マスクROMだけでなく、マスクROMの内蔵が必要となるワンチップマイクロコンピュータや電子式卓上計算機などで幅広く採用されている。

### 2. 提供技術

- 関連特許の実施許諾

- 特許第1174707号(特公昭58-4461)

「MIS型半導体装置の製造法」

特許第1182276号(特公昭57-38034)

「MIS型半導体装置の製造法」

日立製作所では、すべての所有特許権を適正な価格で皆さまにご利用いただいております。また、ノウハウについてもご相談に応じておりますので、お気軽にお問い合わせください。 お問い合わせは… 株式會社 日 立 製 作 所 〒100 東京都千代田区丸の内一丁目 5番 1号(新丸ビル) 電話(03)214-3114(直通) 特許部 特許営業グループ

# EPROM内蔵CMOS 8 ビットシングルチップマイクロコンピュータ"HD63701X0C"

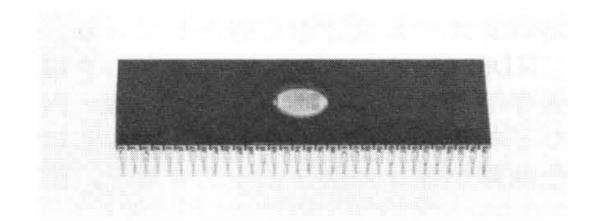

HD63701X0Cは, 世界トップレベル の高性能CMOS (Complementary Metal Oxide Semiconductor) 8 ビットシング ルチップマイクロコンピュータLSI "HD6301"ファミリーの一つで、ユーザ ーが自由にプログラミングできるEPR-OM (Erasable and Programmable Read Only Memory)をチップに内蔵し た新製品である(図1, 2)。 EPROM 内蔵に当たって,読み出し回路の改良や 最小パターン寸法 2 µmの微細加工技術 などの改良により、従来のマスクROM 形マイクロコンピュータLSI"HD6301X" と同等の高速性,低消費電力を維持し, かつチップ面積の拡大を抑えている。 今後は "HD63701X0C" で開発した CMOS EPROM内蔵設計技術を基に

図 I "HD63701XOC"のチップ写真

ファミリー展開を進め、市場のニーズにこたえてゆく予定である。

### 1. 主な特長

- (1) CMOSマイクロコンピュータでは 世界トップレベルの4kバイトEPROM を内蔵している。

- (2) マスクROM形マイクロコンピュー タLSI "HD6301X0P" と機能, ピン配 置など完全に互換性をもっている。

- (3) EPROMのプログラミングは, "2732 A"タイプEPROMと同じ仕様であり, 64ピンから24ピンへの簡単な変換アダプタを用いて, 汎用PROMライタでプログラミングができる。

### 2. 主な用途

マスクROMにする前の応用プログラムのデバッグ用や生産立上げ時点の量産用として用いられるだけでなく、きめ細かな顧客対応を要求される情報産業機器、迅速なプログラム変更が必要な開発期間の短いOA(オフィスオートメーション)機器などを中心に幅広い分

図 2 "HD63701XOC"の外観

野での応用が期待される。

### 3. 主な仕様

主な仕様を表1に示す。

(日立製作所 半導体事業部)

表し主な仕様

|           | 項目          | 内容                                                                                                                              |  |  |  |

|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|           | CPU         | HD630IファミリCPU                                                                                                                   |  |  |  |

| MCU<br>部  | RAM         | 192バイト                                                                                                                          |  |  |  |

|           | 1/0(本)      | 53                                                                                                                              |  |  |  |

|           | タイマ(本)      | 16ビット× 3<br>8 ビット× I                                                                                                            |  |  |  |

|           | シリアルインタフェース | 有(調歩同期式/クロック同期式)                                                                                                                |  |  |  |

|           | 外部メモリ拡張     | 64kバイトまで可                                                                                                                       |  |  |  |

|           | その他         | <ul><li>エラー検出</li><li>低消費電力モード</li><li>(スリープ/スタンバイ)</li><li>メモリレディ,ホールト機能</li></ul>                                             |  |  |  |

| EPROM:    | 容量          | 4kバイト                                                                                                                           |  |  |  |

|           | 書き込み電圧      | 21V ±0.5V                                                                                                                       |  |  |  |

|           | 書き込み時間      | 50ms                                                                                                                            |  |  |  |

|           | 消去特性        | 15W·s/cm <sup>2</sup><br>(253.7nm紫外線)                                                                                           |  |  |  |

| 最小命令実行時間  |             | <ul> <li>1.0µs(1.0MHz動作時)</li> <li>0.67µs(1.5MHz動作時)</li> <li>0.5µs(2.0MHz動作時)</li> </ul>                                       |  |  |  |

| 消費電力(標準値) |             | 動作時 $30\text{mW}(V_{CC}=5\text{V}:1\text{MHz動作時})$ スリープ $/$ スタンバイモード $5\text{mW}/10\mu\text{V}$ EPROM書き込み時 $I_{pp}=30\text{mA}$ |  |  |  |

|           | パッケージ       | 窓付きDILセラミック<br>64ピンシュリンクパッケーシ                                                                                                   |  |  |  |

注:略語説明

CPU(中央処理装置), RAM(Random Access Memory) I/O(入出力装置), MCU(Micro Computer Unit) EPROM(Erasable and Programmable Read Only Memory)

# ハードディスクコントローラ"HD63463"

マイクロコンピュータの応用が本格 化するにつれ、OA(Office Automation) 分野等で小形・高速・大容量ディスク ストーレージに対する需要が急速に伸 びてきている。また、制御回路のLSI 化の要求も強い。これら動向にこたえ るため、ハードディスク装置とマイク ロコンピュータシステムとの接続を行 なう周辺LSI、HDC(ハードディスク コントローラ)HD63463を開発した。

HDCはウインチェスタ形ハードディスク装置で主流になっているST506準拠インタフェースをもつ装置(ディスク径5.25in), とSMD(Storage Module Drive)準拠インタフェースをもつ装置(ディスク径8in)の2種類のタイプを

図 I ハードディスクコントローラ "HD 63463"

同一チップで制御する専用デバイスコ ントローラである。22種の制御コマン ドを備え、ヘッドのシーク動作、デー タのリード・ライト, データの転送, ドライブ状態の監視など,一連のディ スク入出力制御を行なう。また、256バ イトから成る内蔵データバッファ2面 をダイナミックに切り換えて使用する アーキテクチャを採用したことにより、 MPU (Micro Processer Unit) 側のデ ータ入出力転送とディスク装置へのリ ード・ライト動作の並列処理を可能とし た。これによりDMA(Direct Memory Access)によるMPU側の高速データ転 送, プログラム入出力による低速デー 夕転送などの応用が容易となっている。 またHDCはディスクデータの信頼性向 上のため、32ビットECC(Error Correction Code)によるディスクリードデ ータの誤り検出,及び訂正機能を内蔵 している。11ビット以下のバースト誤 りに対しては、内蔵データバッファト で誤りの自動訂正を行なう(256バイト/ セクタのとき)。MPUインタフェース は、16ビットバスのほか8ビットバスも 選択可能であり、8ビットから16ビット

マイクロコンピュータシステムまで広範囲のディスクシステムに応用できる。

表 1 にHD63463の特長と仕様概要を 示す。

(日立製作所 半導体事業部)

表 I HD63463の特長・仕様概要

|              | 項        | į  | 目               |                    |      | 内                                                                                                     | 容                                 |

|--------------|----------|----|-----------------|--------------------|------|-------------------------------------------------------------------------------------------------------|-----------------------------------|

| ホーデデー内部      | ー タ<br>ー | タ  |                 | 波<br>東<br>転<br>ッフ  | 数度送ア | HD63463-4(4MH<br>HD63463-6(6MH<br>HD63463-8(8MH<br>IOMbps<br>PIO/DMA(サイ:はバー<br>512バイト(256/1           | lz),<br>lz)<br>クルスチール又<br>ーストモード) |

| ドライブ<br>接続可能 | セク       | タフ | オ -             | ェ ー<br>- マッ<br>変調方 | ۲    | ST506インタフ:<br>インタフェース<br>ハードセクタ/ソ<br>NRZ/MFM                                                          |                                   |

| フォライブット      | セクデー     | タ数 | / I<br>長 /<br>イ | ドライック ブ            | ク    | 最大 1,024<br>最大 256<br>256, 512, 1,026<br>4,096バイト<br>SMDインタフェ<br>ST506インタフェ<br>SMDインタフェ<br>ST506インタフェ | -ス 最大 8,<br>ェース 最大 4<br>-ス 最大32,  |

| I            | ラ ー      | チ  | I               | 'n                 | þ    | 32ビットECC(多                                                                                            | $16 + x^{12} + x^5 + 1$           |

| ŧ            |          | Ø  |                 |                    | 他    | マルチプルセク:<br>トラック処理<br>ノーマルシーク・<br>自動データエラ・<br>HDC外付け回路                                                | パラレルシーク<br>- 訂正機能,                |

### 製品紹介

# グラフィック描画・表示を行なう 高性能CRTコントローラ

OA(Office Automation)機器/CAD (Computer Aided Design)端末などでは、表示画面の構成に自由度が高く、高精細、多色(多階調)のグラフィックディスプレイを使用する傾向が高まっている。今回、各種画面表示制御用マイクロプロセッサ及び多色を基調とした高度なグラフィック描画機能をもつマイクロプロセッサを、同一チップ上に集積したCRT(Cathode Ray Tube)ディスプレイ制御に最適なLSI、HD 63484(ACRTC)を開発した(図1)。

高解像カラーCRTディスプレイに対応すべく、HD63484はMPU(Micro Processer Unit)から独立した2Mバイトのフレームバッファを管理し、2,048×2,048画素16色同時表示やフルビットマップ画面とキャラクタ画面を重ね合わせて表示するなど、高機能及び高性能

高性能CRTコントローラHD63484

表 I HD63484の特長及び仕様概要

| 項目               | 内                                  | 容                                              | 項 目              | 内                                                                                                                                                                                | 容                                               |

|------------------|------------------------------------|------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| クロック周波数          | HD63484-4(4MHz)                    |                                                |                  | カラー処理                                                                                                                                                                            | 1, 2, 4, 8, 16ビット/画素 選択可能                       |

|                  | HD63484-6(6MHz)<br>HD63484-8(8MHz) |                                                |                  | 描画演算モード                                                                                                                                                                          | Replace, OR, AND, EOR<br>条件付Replace 4種          |

| MPUインタフェース       | 16ビットバス                            | HMCS68000非同期バス対応                               |                  | 描画エリア管理                                                                                                                                                                          | 描画エリア内・外への描画禁止及び<br>描画アクセスの検出が可能                |

|                  | 8 ビットバス                            | HMCS6800同期バス対応                                 | 描画制御機能           |                                                                                                                                                                                  |                                                 |

| フレーム<br>バッファスペース | グラフィックプレーン                         | 2 Mバイト(Max.)                                   |                  | 描画座標系<br>(描画点指定)                                                                                                                                                                 | X・Y座標系でのドット単位による直接又は間接指定(グラフィック描画)              |

|                  | キャラクタブレーン                          | 128kバイト(Max.)                                  |                  |                                                                                                                                                                                  |                                                 |

| 表示制御機能           | 画面分割                               | 3 水平分割+   ウィンドウ                                |                  | グラフィック<br>パターンRAM                                                                                                                                                                | 16ドット×16ドットの容量,任意パターン領域の参照,垂直・水平独立に1~16倍の拡大描画可能 |

|                  | 混在表示                               | グラフィック画面とキャラクタ画面                               |                  |                                                                                                                                                                                  |                                                 |

|                  | 重ね合せ表示                             | 水平分割画面とウィンドウの重ね合せ                              |                  |                                                                                                                                                                                  |                                                 |

|                  | スクロール                              | 垂直方向スムースクロール可能<br>水平方向スムーススクロールサポート            | フレームバッファ<br>アクセス | アクセスモード<br>(サイクルスチール・重ね合せ)                                                                                                                                                       | シングルアクセス、ダブルアクセスO、<br>ダブルアクセス   の3種が選択可能        |

|                  | 拡大表示                               | スクリーン で垂直 ~ 6倍可能<br>水平 ~ 6倍サポート,各々独立設定         |                  | DMA転送制御機能,割込み要求機能(8種),外部同期動作,3<br>スキャンモード対応(ノンインタレース,インタレース,インタレース及びビデオ),ブリンク制御回路内蔵,ライトペン信号用入力サポート,ダイナミックRAM用リフレッシュアドレス出力(8ビット),フレームバッファ外部アクセスサポート可能,+5V単一電源,64ピン デュアルインラインバッケージ |                                                 |

|                  | カーソル                               | キャラクタカーソル2本<br>グラフィックカーソル(クロスヘア・ブロック)          | その他              |                                                                                                                                                                                  |                                                 |

| 描画制御機能           | コマンド                               | レジスタ制御:5種,DMA制御:3種<br>データ転送:7種<br>グラフィック描画:23種 |                  |                                                                                                                                                                                  |                                                 |

注:略語説明 MPU(Micro Processer Unit) RAM(Random Access Memory)

化を実現している。

システム側とのデータ転送は、HMCS 68000システム非同期確認方式とHMCS 6800システム同期方式が選択でき、他の汎用MPUやDMAC(Direct Memory Access Controller)に対する考慮及び制御信号をもっているため、柔軟度の高いシステム設計を可能としている。

HD63484は,内部にグラフィック描画専用のプロセッサを内蔵し,線・円などの描画をはじめMPUの介在なしに色演算を含むグラフィックコピー,塗

りつぶし(タイリング), クリッピング 処理などを高速(モノクローム~65536 色調同一描画速度)に行なう。また, 描 画点の指定をX-Y座標系で行なうなど, MPUに対するソフトウェアのオーバへ ッドを低減している。他に分割画面表 示や, 水平・垂直方向へのスムースス クロール, 縦・横独立して1~16倍の 拡大表示など,表示制御機能も多く幅 広い応用に対応できる。

表1 に特長及び仕様概要を示す。 (日立製作所 半導体事業部)

### 日 立 評 論 Vol. 66 No.8 予定目次

### ■小特集 記憶装置とリレーショナルデータベース

大容量磁気ディスク装置

小形磁気ディスク装置の開発-高性能 8 in 及び5.25in ディスク装置-FDD-441大容量フロッピーディスク駆動装置の開発

小形フロッピーディスクの開発

光ディスク記憶装置

高性能補助記憶装置と導入効果向上手法の開発

ストリーミング磁気テープ装置

VOSO/ES, DPOSリレーショナル形データベースの開発

リレーショナルデータベース管理システム"RDB1"

エンジニアリングデータの文書化・グラフ化支援システムの開発

### ■一般論文

東北電力(株)向け中央給電指令所自動化システム 歩道橋向けエスカレーターと管理システム 154kV送電線用ディジタル形距離リレー装置

### 日 立 Vol. 46 No.7 目 次

グ ラ フ 多摩川の水を守る

ル ポ 住宅地図が変わった

一枚一枚の紙面から動く画面へ コンピューターでシステム化

明日を開く技術〈49〉 ディジタル技術の限界を破る

万能数值表現法

振替口座 東京6-20018

新形着脱リモコン とれ・つく・コンを搭載

新 製 品 紹 介 電子冷却はちまき 掃除機 電話機 空気清浄機

技術史の旅〈93〉満濃池

続・美術館めぐり〈55〉 弥生美術館

企画委員

日 立 評 論 第66巻第7号

発 行 日 昭和59年7月20日印刷 昭和59年7月25日発行

発 行 所 日立評論社 東京都千代田区神田駿河台四丁目6番地 101

電話(03)258-1111(大代)

編集兼発行人 倉木正晴

1984

印 刷 所 日立印刷株式会社

定 価 1部500円(送料別)年間購読料 6,700円(送料含む)

取 次 店 株式会社オーム社 東京都千代田区神田錦町三丁目1番

₩ 101 電話(03)233-0641(代)

AND SERVICES MARKET PROPERTY OF SERVICES OF PROPERTY OF SERVICES AND STREET OF SERVICES OF SERVICES

Hitachi Hyoronsha, Printed in Japan (禁無断転載)