# ハードディスクコントローラ"HD63463"

# Hard Disk Controller "HD63463"

ソフトウェアの大規模化,情報量の増大に伴い,マイクロコンピュータの高速・ 大容量ファイルメモリとして5 in 及び8 in ハードディスクの需要が伸びつつある。 これらウインチェスタ形ハードディスクを制御するマイクロコンピュータ周辺LSI としてハードディスクコントローラHD 63463を開発した。データバッファを内蔵す るとともに高機能コマンドを採用して、ディスク制御に関するMPU処理の負担を 大きく軽減した。規則論理を多用したプロセッサモジュールを階層状に組み合わせ た構造と、自己テスト法に基づいたLSI設計手法を用いて、ハードディスクコント ローラを効率よく設計した。同時に、規則論理設計ツールとして、汎用マイクロプ ログラムアセンブラ及びPLA最小化プログラムを開発した。

吉田重秋\* Shigeaki Yoshida 上野達彰\* Tatsuaki Ueno 萩原吉宗\*\* Yoshimune Hagiwara 船橋恒男\*\* Tsuneo Funabashi 迫田行介\*\*\* Kôsuke Sakoda 妻鹿真幸\*\*\*\* Masaki Mega

#### 緒 言 1

マイクロコンピュータの応用が本格化するにつれて, OA (オフィスオートメーション)分野などでは、ソフトウェアの 大規模化,情報量の増大化が進行しつつある。このため、安 価な高速・大容量ディスクストーレージに対する需要が急速 に伸びてきている。この動向に対応して各種の小形ハードデ ィスク装置が開発され、ホストバスインタフェースやディス クドライブインタフェースの標準化も進んでいる。日立製作 所ではこの動向に応じるため、HD68000システムとハードデ ィスク装置の接続を行なう周辺LSIであるハードディスクコ ントローラHD63463を開発した。ハードディスクコントロー ラは、ウインチェスタ形ハードディスク装置で主流となって いるST506準拠インタフェースをもつ装置(ディスク径5.25in), SMD(Storage Module Drive)準拠インタフェースをもつ装 置(ディスク径8 in)の2種類のタイプを同一チップで制御す る専用デバイスコントローラである。パーソナルコンピュー タ, ワードプロセッサ, CRT(Cathode Ray Tube)端末, 中形, 大形コンピュータなどのOA機器周辺としての小形ディスク 制御装置に広範囲に応用できる。

以下, ハードディスクコントローラの特長と機能, 及び設 計技術について述べる。

#### 長 2 特

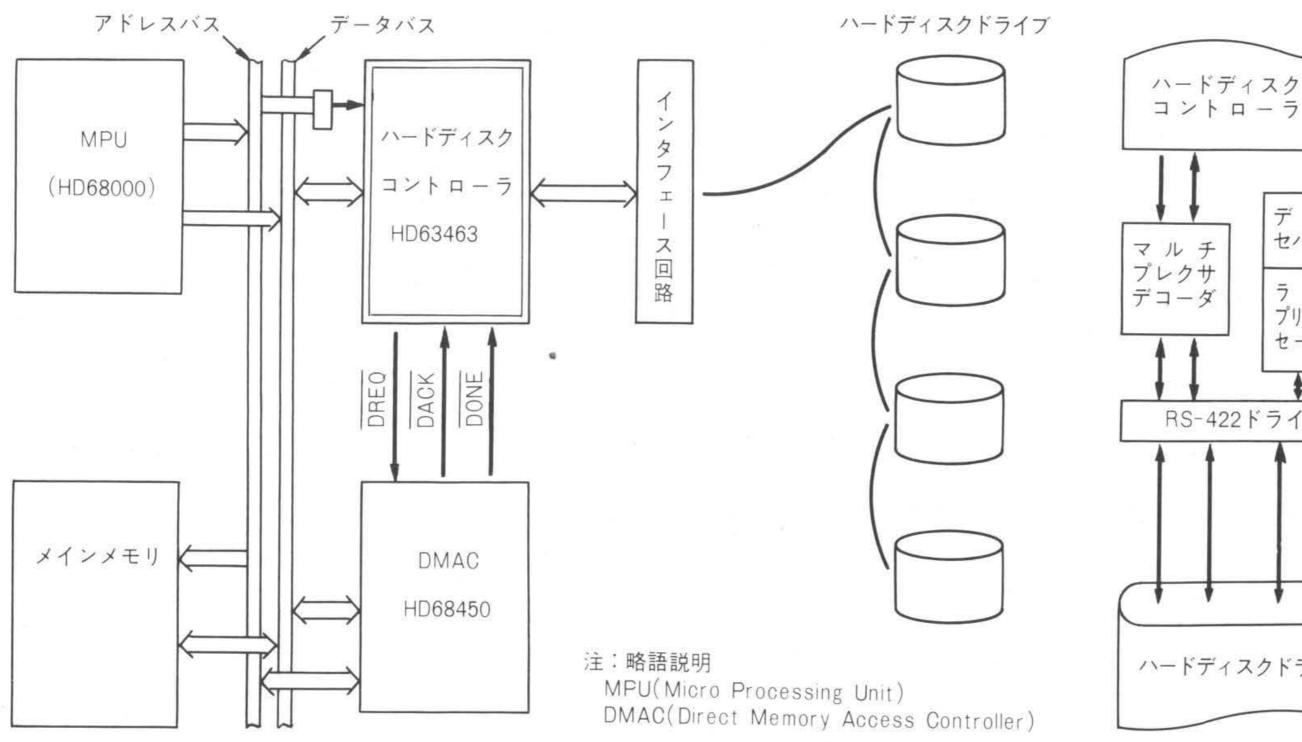

図1にハードディスクコントローラを使ったシステムの構 成例を示す。ハードディスクコントローラはMPU(Micro Processing Unit)から送られる高度に集約された動作指示で ある高機能コマンドに従って、ディスク装置のメカニカル制 御及びデータのリード・ライト制御を行なう。データの転送 は、DMAC(Direct Memory Access Controller)を用いてハ ードディスクコントローラとメインメモリの間で行なうこと を基本とするが、各種アプリケーションに対応するため、 MPUのプログラム入出力によるデータ転送も可能とした。ハ ードディスクコントローラは以下に述べる特長をもっている。 (1) ディスクインタフェース用の入出力端子機能はプログラ マブルでST506/SMD両インタフェースに対応可能である。

(2) 256バイトのデータバッファRAM(Random Access Memory)を2面内蔵し、ディスクドライブ側データ転送とホス

図 | ハードディスクコン トローラシステム構成 ハードディスクコントローラは ST506インタフェースの場合は最 大4台まで、SMDインタフェース の場合は最大8台までのディスク ドライブを制御できる。

<sup>\*\*\*\*</sup> 日立製作所茂原工場 \*\*\* 日立製作所システム開発研究所 \*\* 日立製作所中央研究所 日立製作所武蔵工場

表 I HD63463の仕様概要 ハードディスクコントローラは、仕様の異なるディスクドライブ及びホストバスとの接続を容易にし、またユーザーが使用する各種トラックフォーマットへの対応を容易にするため、内部をプログラマブルな構成にしてある。

|                | 項 目         | 内容                                                                                    |  |

|----------------|-------------|---------------------------------------------------------------------------------------|--|

| ホスト周波数         |             | 4MHz 6MHz 8MHz                                                                        |  |

| デ ー            | - タ 転 送 速 度 | IOM bps                                                                               |  |

| デ              | ー タ 転 送     | PIO・DMA(サイクルスチール又はバーストモード)                                                            |  |

| 内部             | データバッファ     | 512バイト(256バイト×2)                                                                      |  |

| ドライブ           | インタフェース     | ST506インタフェース・SMDインタフェース                                                               |  |

|                | セクタフォーマット   | ソフトセクタ・ハードセクタ                                                                         |  |

|                |             | MFM · NRZ                                                                             |  |

| フォーマット ア ラ イ ブ | シリンダ数/ドライブ  | 最大1,024                                                                               |  |

|                | セクタ数/トラック   | 最大 255                                                                                |  |

|                | データ長/セクタ    | 256, 512, 1,024, 2,048, 4,096バイト                                                      |  |

|                | ド ラ イ ブ 数   | ST506インタフェース 最大4, SMDインタフェース 最大8                                                      |  |

|                | ヘッド数        | ST506インタフェース 最大8, SMDインタフェース最大32                                                      |  |

|                | 4           | I6ビットCRC(多項式:x <sup>16</sup> +1, x <sup>16</sup> +x <sup>12</sup> +x <sup>5</sup> +1) |  |

| エラ             | · - チェック    | 32ビットECC(多項式: $x^{32}+x^{23}+x^{21}+x^{11}+x^2+1$ )                                   |  |

|                | V           | マルチプルセクタ・マルチプルトラック処理                                                                  |  |

| 4              |             | ノーマルシーク・パラレルシーク                                                                       |  |

|                | の他          | データエラー自動訂正機能                                                                          |  |

|                |             | ハードディスクコントローラ外付け回路診断                                                                  |  |

#### 注:略語説明

PIO · DMA(Program Input Output · Direct Memory Access)

SMD(Storage Module Drive)

MFM · NRZ(Modified Frequency Modulation · Non Return to Zero)

CRC(Cyclic Redundary Code)

ECC(Error Correction Code)

|                       | ST506インタフェース    | SMDインタフェース  |

|-----------------------|-----------------|-------------|

| V <sub>c c</sub> 1 48 | READY(入力)       | BUSL/H(出力)  |

| RES 2 47              | SEEK(出力)        | BUSR/W(出力)  |

| DREQ 3 46             | HSEL2(出力)       | TAG5(出力)    |

| IRQ 4 45              | HSEL1(出力)       | UTAG(出力)    |

| DONE 5 44             | HSELO(出力)       | TAG3(出力)    |

| RS 6 43               | USEL1(出力)       | TAG2(出力)    |

| DTACK 7 42            | USELO(出力)       | TAG1(出力)    |

| R/W 8 41              | USELD(入力)       | USELD(入力)   |

| CS 9 40               | SCP(入力)         | SEC(入力)     |

| DACK 10 39            | IDX/TRKO(入力)    | IDX(入力)     |

| DO 11 38              | LCT/DIR(出力)     | BUS4/9(入出力) |

| D1 12 37              | WFLT(入力)        | BUS3/8(入出力) |

| D2 13 36              | LATE/STEP(出力)   | BUS2/7(入出力) |

| CLK 14 35             | EARLY/RGATE(出力) | BUS1/6(入出力) |

| $V_{ss}$ 15 34        | WGATE(出力)       | BUS0/5(入出力) |

| D3 16 33              | $V_{ss}$        |             |

| D4 17 32              | SYNC(出力)        | SKEND(入力)   |

| D5 18 31              | RCLK(入力)        | RCLK(入力)    |

| D6 19 30              | WCLK(入力)        | WCLK(入力)    |

| D7 20 29              | RWDATA(入出力)     | RWDATA(入出力) |

| D8 21 28              | D15             |             |

| D9 22 27              | D14             |             |

| D10 23 26             | D13             |             |

| D11 24 25             | D12             |             |

図 2 ピン配置 電源投入後SPECIFYコマンド発行によりST506, SMD インタフェースの指定を行なう。

ト側データ転送を独立して制御することにより、MPU側システムバス利用効率を向上できる。

- (3) 高機能コマンドの採用によりMPUのソフトウェア負担を軽減できる。

- (4) リードデータのエラー検出,自動訂正によりディスクデータの信頼性を向上できる。

- (5) ディスクドライブ診断コマンドによりディスク装置の保守性を向上できる。

- (6) 16ビット及び8ビットデータバスと直接インタフェースが可能である。

表1にハードディスクコントローラの仕様概要を示す。

#### 8 ハードディスクコントローラの機能

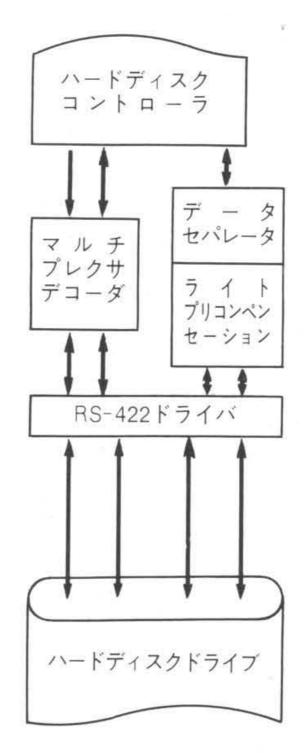

#### 3.1 ディスクインタフェース機能

図2にハードディスクコントローラのピン配置図を示す。ハードディスクコントローラは、ディスク装置側インタフェース信号をマルチプレックスすることにより、仕様の異なる5 in (ST506インタフェース) ディスク装置と8 in (SMDインタフェース) ディスク装置との接続を選択可能にした。ST506インタフェースでは最大4台のドライブまで、SMD インタフェースでは最大8台のドライブまで接続が可能であり、ディスクファイルの大容量化への対応を可能としている。MPUとのインタフェースでデータバスは16ビット構成となっているが、ユーザーは下位8ビットだけを用いる動作モードを指定することも可能とした。HD68000、HD6800との接続のほか、他MPUとの接続も容易に行なえる。

#### 3.2 内部構成

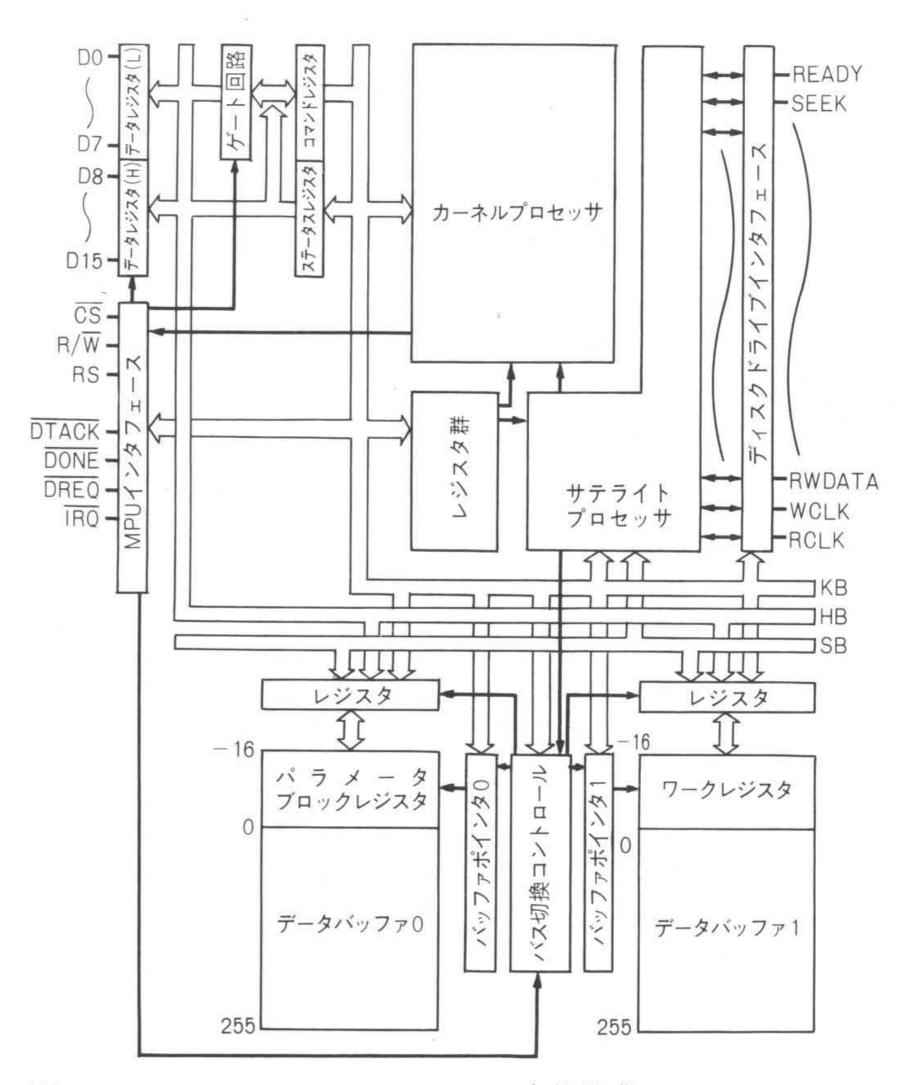

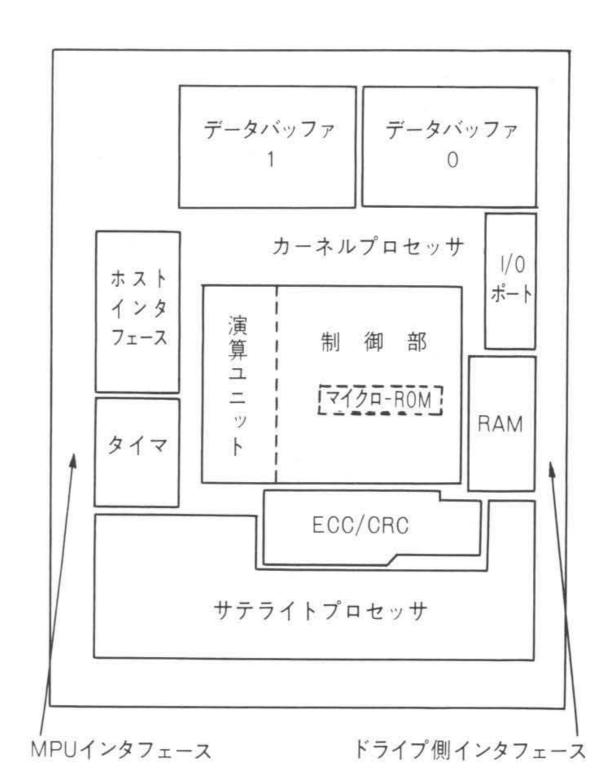

ハードディスクコントローラの内部構成を**図3**に示す。ハードディスクコントローラは二つのプロセッサモジュール(カ

図3 ハードディスクコントローラの内部構成 ハードディスクコントローラは全体の制御を行なうカーネルプロセッサ、シリアルデータの高速 処理を行なうサテライトプロセッサから構成され、ディスクの制御を行なう。

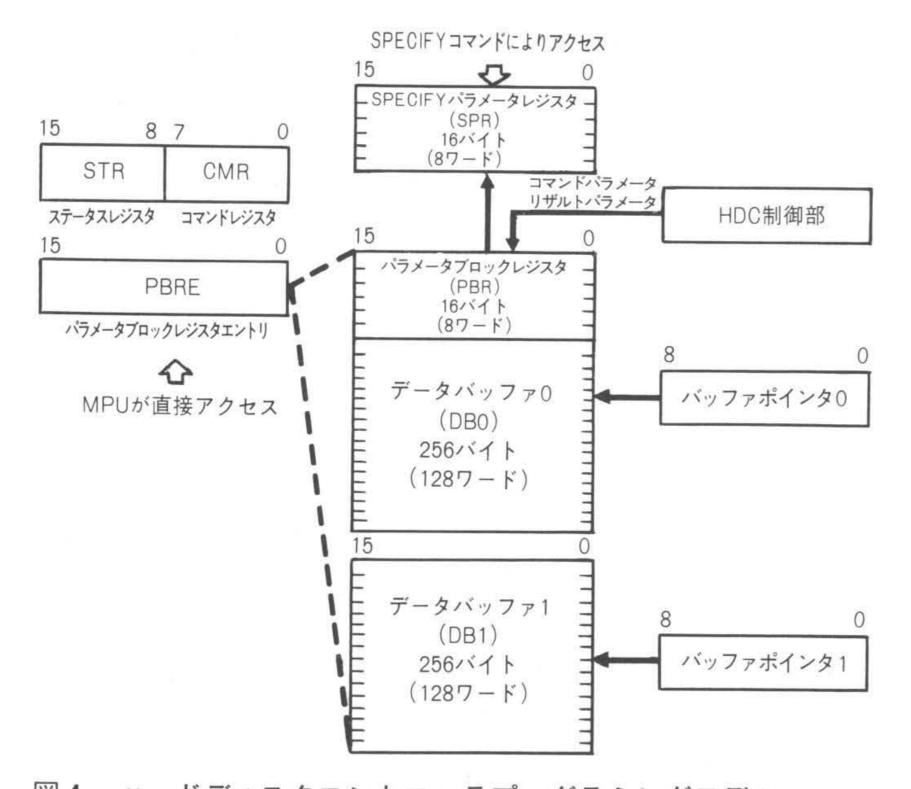

ーネルプロセッサ、サテライトプロセッサ)と256バイトから 成る2面のデータバッファ,及びMPUインタフェース,ドラ イブインタフェースの各モジュールから構成されている。カ ーネルプロセッサは、MPUからのコマンドの解釈とハードデ ィスクコントローラ内部の他のモジュールの動作の制御を行 ない、サテライトプロセッサはハードディスクとの高速デー タ転送を行なう。図4にハードディスクコントローラのプロ グラミングモデルを示す。ハードディスクコントローラのプ ログラマブルな各種の機能の指定は、SPECIFY コマンドを 用いて16バイトからなるSPECIFYパラメータレジスタ(SPR) にパラメータをセットすることにより行なう。これにより、 仕様の異なるディスクドライブへの対応、またユーザーが使 用する各種トラックフォーマットへの対応を可能にした。

#### 3.3 コマンドの機能

ハードディスクコントローラの動作指定はMPUがコマン ドをコマンドレジスタに書き込むことにより行なう。表2に コマンド一覧表を示す。ハードディスクコントローラはコマ ンドを受け付けると, ディスク動作に必要な一連の制御を行 なう。シーク動作、すなわちヘッドの移動制御に対しては、 二つのコマンド(Recalibrate, Seek)を備えている。ST506イ ンタフェースのシークモードとしては,低速動作モード(ノー マルシーク)のほかに、高速動作モード(バッファシーク)が可 能であり、この場合複数ディスクドライブに対して並行して シーク動作を行なわせることができる。リード・ライト系コ マンド(Read Data, Write Dataなど)ディスク装置とデータ バッファの間のデータのやりとり、データバッファとメイン メモリ間のデータのやりとりを並行して行なうモードと、前 者だけを行なうモードの二とおりを選択できる。

データ転送系の4コマンドは、データバッファとメインメ モリの間のデータ転送を制御する専用コマンドである。

# 3.4 データ転送

ハードディスクコントローラを用いたシステムでは, デー 夕転送は前述したように、ディスク装置とデータバッファ、 データバッファとメインメモリの間の2段階で行なわれる。

図 4 ハードディスクコントローラプログラミングモデル ドディスクコントローラのプログラマブルな機能は、SPR(Specify Parameter Register)で指定される。データバッファのアクセスは、バーファポインタによ りハードディスクコントローラが管理する。MPUはバッファ内の任意のロケー ションをOpen buffer Read/Writeコマンドによりバッファポインタを変えてア クセスできる。

表 2 コマンド一覧 ハードディスクコントローラはディスク制御に必 要な22種の高機能コマンドを備えている。

| ٦                 | マンド分類      | コマンド分類(21種)                                                                        |

|-------------------|------------|------------------------------------------------------------------------------------|

| ハードディスクコントローラ仕様指定 |            | Specify                                                                            |

| シーク系コマンド          |            | Recalibrate Seek                                                                   |

| リード               | ・ライト系コマンド  | Read Data Read Erroneous Data Read ID Find ID Compare Data Write Data Write Format |

| デ ー タ             | 転送系コマンド    | Memory to Buffer<br>Buffer to Memory<br>Open Buffer Read<br>Open Buffer Write      |

| ドライブ              | チェック系コマンド  | Polling<br>Check Drive                                                             |

| ÷.                | <i>の</i> 他 | Abort Check Data Check ECC Test Polling Disable Recall                             |

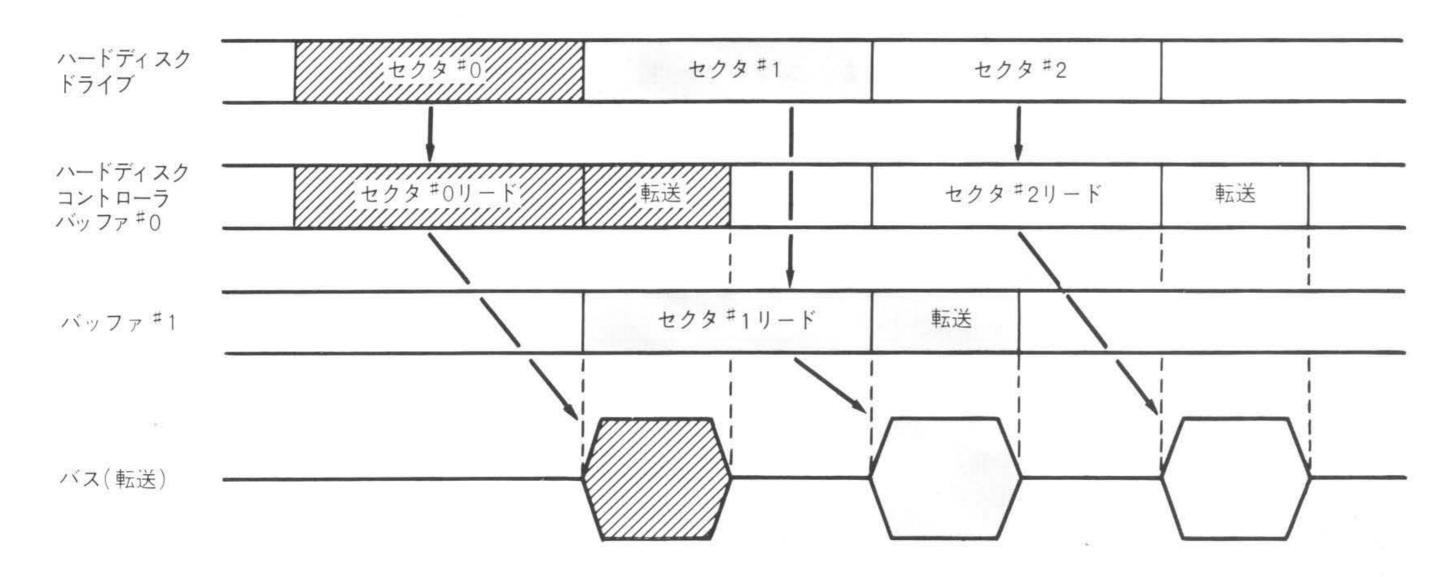

256バイトデータバッファ2面を切り換えて使うことによって、 ディスクアクセスとホスト側データ転送の並列動作を可能と している。図5はディスクからマルチプルセクタ動作でデー タを読み取り、メインメモリにデータを転送する例である。 以下,各ステップの動作を示す。

- (1) セクタ"0"から読み込んだデータをデータバッファ#0へ 格納する。

- (2) ハードディスクコントローラはセクタ"1"を探し、デー タバッファ#1へ格納する。このとき,並行してデータバッフ ア#0の内容をメインメモリに転送する。

- (3) 以降,「ディスク装置とデータバッファ間の転送」と「デ ータバッファとメインメモリ間の転送」をデータバッファ#0と #1を切り換えながら行なう。

このようにデータバッファを介することにより、メインメモ りとの間でバス最大転送速度での転送を行なうことができる。 またハードディスクコントローラは、ディスクから読み込ん だデータバッファの内容がメインメモリへ未転送の場合, そ のデータバッファ内のデータ転送が終了してから次のセクタ をリードする機能をサポートしている。ディスク書き込みの 場合も同様である。この機能により、ハードディスクコント ローラは、サイクルスチールモードDMA(Direct Memory Access)転送などのデータ転送が遅いシステムに対しても, 接続を容易にしている。更に、1セクタのリード・ライト時 には、データバッファを用いたプログラムによる入出力転送 が可能である(256,512バイト/セクタのときのみ)。

図6に内蔵データバッファを利用したデータ編集機能を示 す。ディスク上のデータをデータバッファに読み出し、一部 修正箇所を書き替え,再びディスク上にもどすエディット機能, またディスクデータがデータバッファを経由するだけでホス ト側データ転送を伴わないディスクデータのコピーなどの応 用操作が、2~3のコマンドを組み合わせてMPUが発行す

図 5 データ転送(READ DATA, データ長256バイト) マルチセクタリードの場合は,「バッファ‡0データのメインメモリへの転送」と「セクタ‡1データのバッファ‡1への読み込み」を並行して同時に行なう。

ることにより可能である。

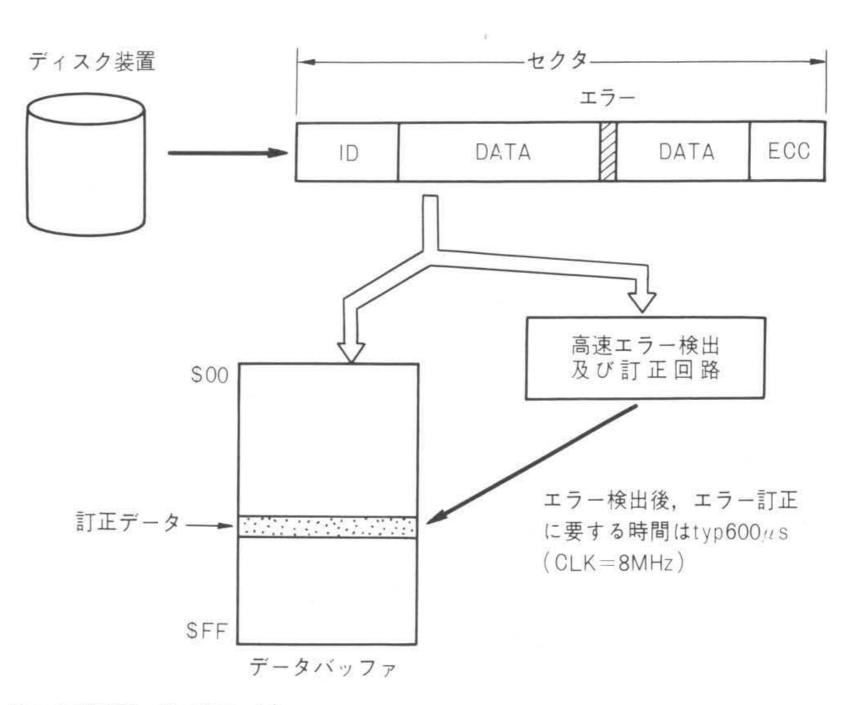

#### 3.5 エラー検出, 訂正機能

ペードディスクコントローラは、ディスクデータの信頼性 確保のため、16ビットCRC(Cyclic Redundary Code)又は32 ビットECC(Error Correction Code)のコードチェック及び 生成を行なって、ディスクデータの誤り検出を行なう。ハードディスクコントローラの誤り検出コードとしてECCを選択 すると、ディスクデータの誤りが1箇所で連続して11ビット 以下ならば、ハードディスクコントローラは、このエラーを 検出後にエラー発生位置とエラー訂正用情報をMPUへ報告 する。更に、1セクタのデータ長が256バイトの場合、ハード ディスクコントローラは内蔵データバッファ上でエラー訂正 を自動的に行なう。これによりエラー訂正に要していたMPU 処理を不要とした(図7)。

#### 3.6 保守,診断機能

ハードディスクコントローラは、ディスク装置に異常が検出された場合でも、可及的にリカバリを行なうコマンドを備えている。すなわち、ディスクの動作状態をチェックするCheck Drive、エラー訂正に必要な情報をMPUに伝えるCheck ECC、ディスク記憶情報に一部誤りがあってもデータの読み出しを行なうRead Erroneous Dataなどのコマンドを備えている。これらは、間欠的に発生するディスクデータのエラーの訂正、ディスク障害時のファイルデータの吸い上げなどに利用される。またハードディスクコントローラの出力を高インピーダ

エディット

バッファポインタ

データバス

MPUによる ディスク装置

データバッファ

A

ディスク装置

データバッファ

B

図 6 内蔵データバッファを利用したデータ編集 内蔵データバッファ上でディスクファイルの一部修正、ディスクデータのコピーなどの応用操作が可能である。

ンスにし、実効的にハードディスクコントローラをシステムから切り離す Test コマンドを備えていて、ハードディスクコントローラ周辺回路の電気的チェックを容易にしている。

#### 3.7 ディスクデータ転送時間の評価

ハードディスクコントローラとメインメモリ間でディスク データをDMA転送する場合,ディスクのデータ転送速度が 高速なため(5 inディスクの場合5 Mビット/秒),データ転送 をDMAコントローラのバーストモードを用いて行なうこと が多い。以下,データバッファ内蔵の効果を,HD68000,HD 68450(8 MHzバースト転送),5 inディスク(5 Mビット/秒)を 用いたシステムでのディスクデータ転送のMPUバス専有時 間で評価する。

#### (1) 内部データバッファありの場合

バス専有時間= $\frac{転送バイト数}{2}$  ×  $125ns \times 5$  サイクル

#### =転送バイト数×300ns

(ディスク上のデータをデータバッファに格納した後,メイ) ンメモリ側へのデータ転送はディスク動作に関係なく,ホ ストバスの最高速度で行なえる。

## (2) データバッファなしの場合

バス専有時間=転送バイト数imes 200 ns/ビットimes 8ビット=転送バイト数 $imes 1.6 \mu s$

注:略語説明 CLK(Clock)

図 7 エラー検出, 訂正機能 ハードディスクコントローラは, Iセクタのデータ長が256バイトの場合, 内蔵データバッファ上で, エラー訂正を自動的に行なう。

ディスクデータ転送速度でMPUバス専有時間が決定され\

ハードディスクコントローラでは上に示したとおり、内部 データバッファ採用により大幅なMPUバス専有時間の削減 を可能とした。これにより、多量のデータ転送を行なう際の MPUのスループット低下を抑えることができた。

#### 設計技術 4

ハードディスクコントローラの開発は論理規模の増大に対 処するため、(1)規則論理を多用した汎用構造に基づくLSI設 計手法の開発と適用,(2)規則論理設計ツールの開発と活用の 二つを基本方針として進めた。以下, ハードディスクコント ローラで用いた設計技術について述べる。

#### 4.1 汎用構造化設計手法

ハードディスクコントローラの内部はカーネルプロセッサ, サテライトプロセッサのプロセッサモジュールを階層的に配 置した汎用構造を適用した。ハードディスクコントローラの 中心となる上位のカーネルプロセッサモジュールは、マイク ロプログラム制御〔24ビット×2,048 語のROM (Read Only Memory)に格納」としたほか、RAM、演算ユニットなど、規則 性の高い論理ブロックで構成した。マイクロプログラムの設 計は,以下に示す汎用マイクロプログラムアセンブラを用い て行なった。カーネルプロセッサの下位に位置するサテライ トプロセッサは、PLA (Programmable Logic Array)主体 (約7,000ビット)で構成し、規則性を向上させた。また、テス ト技術として内部擬似乱数発生器, テスト結果圧縮器を用い た自己テスト法を採用した。これらのテスト用回路は,本来 ハードディスクコントローラとして必要な回路と共用化を図 っており、自己テストによるハードウェア増加を抑制した。 図8にハードディスクコントローラのチップ写真を示す。 2μm CMOS (Complementary Metal Oxide Semiconductor)

プロセスを用い, 7.02mm×8.94mmのチップ上に約12万9,000 トランジスタを集積した。

### 4.2 規則論理設計ツール

ROM, RAM, PLAなどの規則性の高い構造の論理ブロッ クを多く採用して、設計効率を向上させるため、LSI開発と 並行して次に述べる新しい設計ツールを開発した。

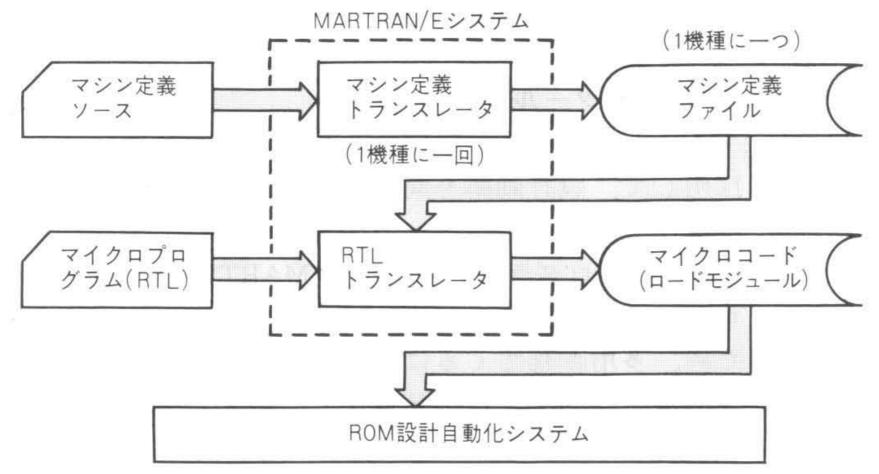

### (1) 汎用マイクロプログラムアセンブラ(MARTRAN/E)

マイクロプログラム方式が周辺LSI中の各種プロセッサを 構成するため、多用されてくるにつれ、(a)マイクロプログラ ムそれ自身の生産性向上及び高品質化と,(b)その開発ツール としてのマイクロプログラムアセンブラの短期効率的開発が 必要となる。このため、RTL(レジスタ転送レベル)の高級言 語でVLSI用のマイクロプログラムを記述し、それからマイ クロコードを生成するマイクロプログラムアセンブラを、マ イクロプロセッサを定義するマシン定義ソースを入れ替える だけで実現することのできる汎用マイクロプログラムアセン ブラMARTRAN (Microprogram in ASM and RTL Translator)/Eを開発した(図9)。これを用いることにより、専用 のマイクロプログラムアセンブラ開発の量以下の工数(1~2 週・人)でマシン定義ソース(400~600行)を開発することが できる。

#### (2) PLA最小化プログラム(PLAMINI)

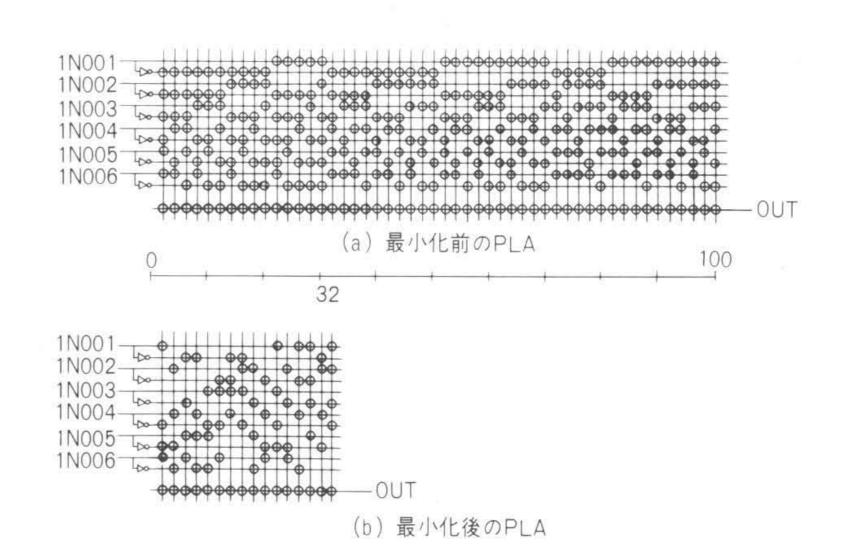

PLAはAND-ORを基本構造とし、組合せ回路なら自由に実 現できるが、特に入力変数の多い論理回路を、アレイサイズ の小さいPLAとなるように設計することは人手では不可能に 近い。特に周辺LSIのような量産LSIでは、PLAの最小化技 術が必要である。PLAのアレイサイズを論理式の簡単化によ り自動的に最小化するツールとしてPLA MINI(PLA Minimizer)を開発した。このツールは図10に示すように、初期PLA パターンを入力すると、最小化アルゴリズムにより論理的に 等価で、理論的に最小のPLAに近いサイズのPLAに圧縮する。

注:略語説明 ROM(Read Only Memory) RAM(Random Access Memory) ECC/CRC(Error Correction Code/ Cyclic Redundancy Code)

ハードディスクコントローラチップ写真 カーネルプロセッ サ、サテライトプロセッサ、データバッファなどの機能モジュールから構成さ れる。CMOS  $2\mu$ mプロセスを使い、7.02mmimes 8.94mmのチップ上に約12万9,000 トランジスタを集積している。

注:略語説明

MARTRAN(Microprogram in ASM and RTL Translator)

RTL(Register Transfer Language)

図 9 MARTRAN/Eシステムの概要 マシン定義とRTLトランスレー タ処理系を分離し、汎用性を実現している。

このツールの適用効果は、入力するPLAのパターンにも依存するが、5~80%サイズを小さくできる。

またこのツールは、マイクロプログラムのROMのパターン 圧縮にも適用できる。今回本PLA最小化プログラムはハード ディスクコントローラ開発には直接活用することはできなか ったが、今後の製品展開には有効な手段を提供するものと期 待している。

### 5 結 言

以上,ハードディスクコントローラHD63463についてその機能概要と設計手法及びツールについて述べた。現在市場にある5 in 及び8 in 形ハードディスクのほとんどは本ハード

図10 PLAMINIの効果 6入力 I 出力のPLAが、初期サイズ(a)に対して32%のサイズ(b)に最小化されている。

ディスクコントローラを用いることにより制御可能である。 しかし、今後ハードディスク装置は大容量化、小形化、高速 化、低価格化など、ユーザーニーズに応じ製品展開が進むも のと見込まれる。今回のハードディスクコントローラの開発 成果と前記設計手法及びツールを活用して、今後のコントロ ールLSI製品展開に対応していきたいと考えている。

### 参考分献

- 1) 岩崎,外:シリアルデータ処理用LSIのアーキテクチャについて,58年度電子通信学会全国大会,No.514

- 2) ハードディスク制御用LSI HD63463(HDC), 株式会社日立 製作所, Hitachi Semiconductor News"GAIN"44号(昭59-5)

# 超高速半導体デバイス

日立製作所 久保征治・他2名 テレビジョン学会誌 38-2,117~124 (昭59-2)

超高速半導体デバイスの動作原理と特徴、 最近の動向と今後の見通しについて解説す る。シリコン超高速デバイスのバイポーラ LSIは、従来のプレーナ技術による限界を 越える新構造を使用し、化合物半導体は、 電子移動度やヘテロ接合などの本質的特長 を活用して高性能化が進められている。

半導体デバイスを高速動作させるために は、次の基本条件が必要である。

- (1) キャリヤ走行距離の短縮

- (2) 寄生効果削減による真性動作促進

- (3) キャリヤ走行速度の向上

これまで上記(1)を主眼としてデバイスが改良され、微細加工技術の向上に伴なってデバイスの高性能化が達成されている。この性能向上を支えてきたプレーナ方式では、シリコンウェーハ上にパターンを重ね合わせて焼き付けるホトリソグラフィーを、基本加工方式としている。これによって平面上に多数並んだデバイスを同時一括加工する、バッチプロセスが可能となり、LSIのコストダウンに大きく貢献してきた。

デバイス寸法を比例縮小するいわゆるスケールダウンは、集積度を向上して一括処理できるデバイス数を増加するだけでなく、キャリヤ走行時間を低減してデバイスを効率的に高性能化する手法として定着化してきた。しかし特にバイポーラデバイスでは、縦方向に流れる少数キャリアを横方向に流し込んだ多数キャリヤで制御しており、真性動作領域(エミッタ直下)に対し寄生部分の面積が20倍以上と大きくなっている。

この原因は、エミッタ、ベース、コレクタの各電極が同一平面上に(1回の工程で)形成されるため、最小加工寸法以下には接近できないことにある。このプレーナ構造に代わって、電極を多層構造としてその間隔を自己整合法で近接して形成する新構造が考案され、実用化されようとしている。

SST(超自己整合), SICOS(側壁ベースコンタクト)やU溝分離技術は,今後比例縮小を基本とするプレーナ技術の限界を越えて寄生効果を大幅に縮小し,高性能化を実現するものとして期待されており,SSTで

は42psのNTL回路の試作例が報告されてい

化合物半導体を用いたデバイスは、電子 移動度などの材料定数の優位性から、前記 (3)の条件を実現しやすく、高速化の可能性 がある。現状では製造技術が未熟で材料定 数が生かし切れない面もあるが、次のデバ イスが動作確認されている。

## (1) MESFET

移動度及び半絶縁基板による寄生容量低減で、20GHz低雑音増幅器が試作されている(ゲート長0.25µm)。

#### (2) HEMT

キャリヤ供給層から分離された高純度走行領域で高速化を図り、300Kで17ps、77Kで13ps/ゲートが試作されている。その他へテロ接合バイポーラやSIT・PBTで100GHz以上の高周波特性も予想されており、ディジタル素子の高速化も含め、プロセス技術の高速化を踏まえて化合物デバイスの高速化が進むと見られている。