# 超高速バイポーラECL RAMシリーズの開発

# Development of High Speed Bipolar ECL RAM Series

バイポーラECL RAMは優れた高速性をもち、情報社会の中枢にあるコンピュータの性能向上に重要な役割を果たしてきたが、近年のOA化の進展につれ各種コンピュータの性能向上を図るために、よりいっそう高速かつ高集積なECL RAMの需要が高まっている。

このような背景を踏まえ、今回、U溝アイソレーション技術や超高速回路、高速高集積回路技術を基盤として、4 kビットで5 nsや、16 kビットで15nsの最大アドレスアクセス時間をもつ高速バイポーラECL RAMシリーズを開発した。

これらのECL RAMは、高速性とともに十分な動作マージンや耐 $\alpha$ 線強度を備え、高い信頼性をもっており、システムの高性能化に大きく寄与することが期待される。

荻上勝己\*Katsumi Ogiue岩渕正人\*Masato Iwabuchi外村健一\*\*Ken'ichi Tonomura

Kunihiko Yamaguchi

山口邦彦\*\*\*

# 1 緒 言

バイポーラECL RAM¹)(Emitter Coupled Logic Random Access Memory)は,情報社会の中枢にあるコンピュータの性能向上に重要な役割を果たしている。これはコンピュータの処理速度を左右するバッファ記憶装置やコントロール記憶装置などに,バイポーラECL RAMの優れた高速性が生かされているからである。このため,コンピュータの大形化,高性能化に伴い,バイポーラECL RAMに対する高速化,高集積化の要求もますます強くなっている。

また、ファクトリー オートメーションやCAD/CAM(Computer Aided Design/Computer Aided Manufacturing)などの事務処理分野に用途が広がり、成長率の目覚ましいスーパミニコンピュータでもシステムの高性能化が進み、論理素子のECL化やバッファ記憶容量の増大が図られ、OA(Office Automation)化の進展とともにより高速で高集積なバイポーラECL RAMの需要が高まっている。

今回、このような需要にこたえるため、 $4 \, \mathrm{k}$  ビットで  $5 \, \mathrm{ns}$ 、 $16 \, \mathrm{k}$  ビットで $15 \, \mathrm{ns}$ の最大アドレスアクセス時間をもつ高速バイポーラECL RAMシリーズを開発した。

本論文では、以上の高速バイポーラECL RAMの特長と開発の基盤となったU溝アイソレーション技術<sup>2)</sup>並びに超高速回路及び高速高集積回路技術などの主要技術について述べるとともに、得られた性能について紹介する。

#### 2 開発製品の特長

表1に、今回開発した製品の概要を示す。

#### 2.1 4kビットECL RAM

$4 \text{ k ECL RAM "HM2144"} は,<math>1 \text{ kP-F} \times 4 \text{ EV-F}$ 構成の入出力信号レベルがECL10kレベルのRAMであり,LCC (Leadless Chip Carrier) パッケージに搭載することで,電源電圧 $-5.2V\pm5$ %,周囲温度 $10\sim50$ ℃で最大アドレスアクセス時間5 ns,最小書込みパルス幅3.5 nsという超高速性をもっている。

また、DIL(Dual In Line)パッケージに搭載したHM10474-8は、パッケージのリードインダクタンスの影響によりスピードが遅れるため、最大アドレスアクセス時間は8 ns、最小書込みパルス幅は4.5nsである。

表 | 超高速バイポーラECL RAMの製品概要 HM2144及びHM10480-15を中心に,多様化するニーズに対応できるようビット構成,入出力信号レベル,パッケージなどの異なる品種の製品化を進めている。

| 区 分          | 単位 | 4 KEY FECL RAM |               |               | 16kビットECL RAM  |                |               |

|--------------|----|----------------|---------------|---------------|----------------|----------------|---------------|

| 品 種 名        |    | HM2144         | HM10474-8     | HM100474-8    | HM10480-15     | HM100480-15    | HM10484-15    |

| ビット構成        | _  | 1,024語× 4 ビット  | 1,024語× 4 ビット | 1,024語× 4 ビット | 16,384語× I ビット | 16,384語× I ビット | 4,096語× 4 ビット |

| 入出カレベル       | _  | ECL-I0k        | ECL-I0k       | ECL-100k      | ECL-I0k        | ECL-100k       | ECL-10k       |

| 最大アドレスアクセス時間 | ns | 5              | 8             | 8             | 15             | 15             | 15            |

| 最小書込みパルス幅    | ns | 3.5            | 4.5           | 4.5           | 13             | 13             | 13            |

| 消 費 電 力      | W  | 1.0            | 1.0           | 1.0           | 0.95           | 0.95           | 1.0           |

| パッケージ        |    | LCC            | DG-24ピン       | DG-24ピン       | DG-20ピン        | DG-20ピン        | DG-28ピン       |

注:略語説明 ECL RAM(Emitter Coupled Logic Random Access Memory)

LCC(リードレスチップキャリアパッケージ)

DG[標準デュアルインパッケージ(Cerdipタイプ)]

<sup>\*</sup> 日立製作所デバイス開発センタ \*\* 日立製作所高崎工場 \*\*\* 日立製作所中央研究所

更に,入出力信号レベルがECL100kレベルのHM100474-8 の製品化も進めている。

以上のECL RAMは、高速性と合わせて保証使用条件の中で、電気的な動作マージンや $\alpha$ 線などに起因するソフトエラー $^{3}$ に対し十分配慮した設計がなされており、各種高性能コンピュータのバッファ記憶装置やコントロール記憶装置に使われ、その性能向上に大きく寄与するものと期待される。

#### 2.2 16k ECL RAM

16kビットECL RAM "HM10480-15" は,16kワード×1 ビット構成で入出力信号レベルがECL10kレベルのRAMであり,DIL20ピンのパッケージに搭載し電源電圧-5.2V $\pm 5$ %,周囲温度 $10\sim50$ °Cで最大アドレスアクセス時間15ns,最小書込みパルス幅13nsの高速性をもっている。

またユーザーの多様化ニーズに対応できるように入出力信号レベルがECL100kレベルのHM100480-15,ビット構成が 4kワード $\times$ 4ビットで入出力信号レベルがECL10k及び100kレベルのHM10484-15,HM100484-15の製品化も進めている。

これらも、4kビットECL RAMと同じく高速性能と十分な電気的動作マージンや耐ソフトエラー強度を兼ね備えており、各種コンピュータやディジタル画像処理装置、高性能テスト

表 2 主要技術 U溝アイソレーション技術を中心とした最先端半導体加工技術や、超高速回路、高速高集積回路技術により、超高速バイポーラECL RAMを製品化した。

| 主要技術           | 内容                       |  |  |  |

|----------------|--------------------------|--|--|--|

| 微細加工技術         | ● 最小パターン1.5μm            |  |  |  |

| アイソレーション技術     | ●1.5μm幅のU溝アイソレーション       |  |  |  |

| 浅い接合形成技術       | ●エミッタ接合深さ0.25μm          |  |  |  |

| 高密度配線技術        | ●最小Al₁配線ピッチ 5 μm         |  |  |  |

| 超高速回路技術        | ●RL切換形メモリセル              |  |  |  |

| (4kビットECL RAM) | ●ダミーセル方式センス回路            |  |  |  |

| 高速高集積回路技術      | ●スピードアップコンデンサをもつpnp負荷形セル |  |  |  |

装置などの高性能化に大きく寄与することが期待される。

# 3 主要技術

4 kビット/5 ns, 16 kビット/15 nsの高速ECL RAMを開発するに当たって必要となった主要技術を表 2に示す。

バイポーラECL RAMの高速化を図る上で微細加工技術や浅い接合技術により、メモリLSIを構成するトランジスタの各種接合容量の低減、遮断周波数fTの向上やベース抵抗 $r_{bb}$ 'の低減が不可欠である。このために、最小パターン幅 $1.5\mu$ mの微細加工技術や、エミッタ接合深さ $0.25\mu$ mの浅い接合形成技術を確立した。一方、高集積化を図るためには、バイポーラ形LSIでは、LSIを構成する回路素子を電気的に分離するためのアイソレーション領域の縮小と回路素子を相互に結線するAI配線の高密度化が必要であり、最小パターン幅 $1.5\mu$ mのU溝アイソレーション技術と最小Al<sub>1</sub>配線ピッチ $5\mu$ mの高密度配線技術を確立した。これらの基盤技術の上に、4kビット/5nsのECL RAMには高速化に有利なRL切換形メモリセルかを軸とした超高速回路技術を,16kビット/15nsのECL RAMには高集積化に有利なpnp負荷形セルがを軸とした高速高集積回路技術を確立し、製品開発を行なった。

以下に、今回の開発で特にポイントとなったU溝アイソレーション技術と、超高速及び高速高集積メモリ回路技術について述べる。

# 3.1 U溝アイソレーション技術

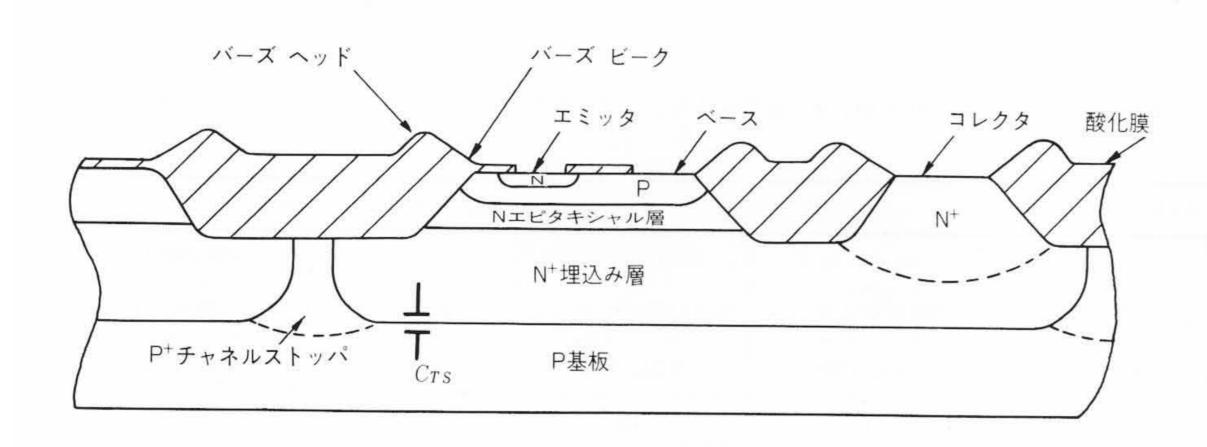

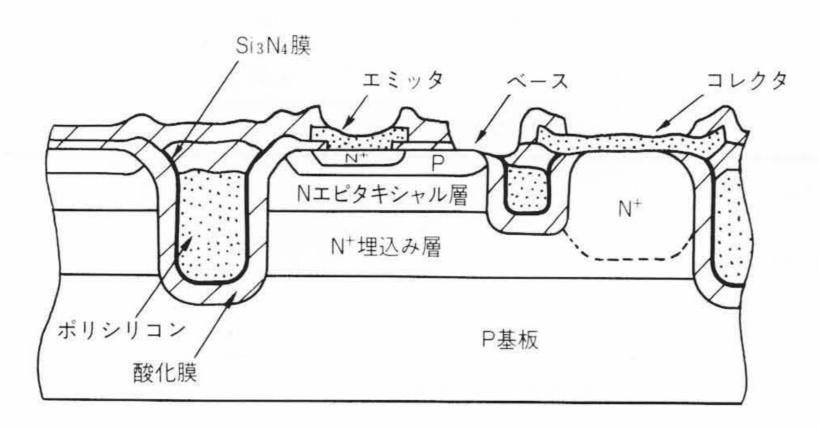

バイポーラ形LSIでは、LSI回路を構成するトランジスタ、ダイオード、抵抗などの素子を相互に電気的に分離するアイソレーション領域が必要である。これは素子間分離が不要なMOS(Metal Oxide Semiconductor)形LSIに比べ、高集積化を図る上のマイナス要因である。このため、高集積化が必要なメモリLSIでは、アイソレーション領域を縮小することが常に重要な開発課題となってきた。図1に、過去15年来バイポーラLSIに用いてきた酸化膜アイソレーション方式を、図2に今回開発したU溝アイソレーション方式を示す。

酸化膜アイソレーション方式は,1971年に実用化されて以来バイポーラICの集積度を飛躍的に向上させ,LSI化への発展を遂げる基になった技術であり,高速バイポーラメモリや高

図 I 酸化膜アイソレーション方式 厚い酸化膜を形成する際に生じるバーズ ビーク などがよりいっそうの集積度の向上を阻んでいた。 またN+埋込み層とP基板によるコレクタ基板間容 量Crs の大幅な低減が不可能になり、高速化を図 る上でのあい路になっていた。

図2 U溝アイソレーション方式 Si中に深い溝を形成することにより発生する結晶欠陥を, U溝上部にY字形のテーパと溝内部にSi<sub>3</sub>N<sub>4</sub>膜を埋め込むことによって防止した。

速論理LSIに適用されてきたが、よりいっそうの高速化、高集 積化を進めていく上で限界に達した。すなわち、この方式は、 窒化膜(Si<sub>3</sub>N<sub>4</sub>膜)をマスクにしてシリコンのエッチングを行な い、そのエッチング部を素子表面とほぼ同じ高さになるよう な1.4~1.8μmの厚い酸化膜(SiO₂膜)を選択酸化によって形 成し、素子間を分離する。この厚い酸化膜を形成する際に、 Si<sub>3</sub>N<sub>4</sub>膜との境界に鳥の形に似ていることから、バーズ ビー クと呼ばれる酸化膜の食い込み部と、バーズ ヘッドと称され る突起部が生じ, 寸法の縮小に限界をもたらしている。また, この方式では、N+埋込み層(N+BL)の上面と厚いSiO2の下面 を合致させなければならないため、それらを形成するマスク パターンに合わせ余裕をとる必要がある。これらが、よりい っそうの集積度の向上を阻んでいた。更に、素子特性面では、 比較的高濃度のN+埋込み層と厚い酸化膜直下のP+チャネルス トッパ層から成る接合が形成されるため、コレクター基板間 容量Crsが低減できない欠点をもち、よりいっそうの高速化を 図る上で大きなあい路になっていた。これら高集積化,高速 化の壁を打ち破るために確立した技術がU溝アイソレーション 方式である。

U溝アイソレーション方式では、Si<sub>3</sub>N<sub>4</sub>膜をマスクにしてプ ラズマエッチングにより、シリコン基板中にほぼ垂直で、4.5~ 5.5µm程度の比較的深い分離溝を掘り、その溝内を選択酸化 し、その後多結晶シリコン(ポリシリコン)を埋め込み、溝を 平たん化し、最後に溝上部のポリシリコンを酸化しアイソレ ーション領域を形成する。これは、プラズマエッチング技術 の発達により初めて可能となった方式であり、 集積度の限界 が微細加工技術で決まり、その進歩とともにアイソレーショ ン幅を狭くできる利点をもっている。またN+埋込み層を深い 溝で完全に分離でき、Crsも小さくなり高速化にも有利な構造 となっている。しかし、シリコン中に深い溝を形成するため に結晶欠陥が発生しやすいこと、溝の形成やその平たん化の 工程が複雑であることなど, 実用化に当たって克服すべき幾 多の技術的課題をもっていた。特に結晶欠陥の発生は、メモ リLSIの歩留まりを低下させる主因となるため、徹底的な対策 が必要であった。

結晶欠陥は、シリコン中に深い溝を掘りその内壁を酸化する際に生じる応力と、溝上部のポリシリコンを酸化する際に シリコンの表面にそって生じる応力によって発生する。これ

表3 アイソレーション方式による素子特性の比較 U溝アイソレーション方式により、大幅な素子面積の縮小と寄生容量の低減が実現でき、高速ECL RAMのいっそうの高速化、高集積化が可能となった。

|    | 項目        | 酸化膜アイソレーション | U溝アイソレーション |  |

|----|-----------|-------------|------------|--|

|    | 最小加工寸     | 法 2 μm      | 1.5μm      |  |

| 素子 | アイソレーション深 | خ ۱.4∼۱.8μm | 4.5~5.5μm  |  |

| 寸  | アイソレーション  | 幅 8 µm      | 3 µm       |  |

| 法一 | 素 子 面     | 積 450μm²    | 180μm²     |  |

| 表  | $C_{TE}$  | 0.04pF      | 0.03pF     |  |

| 素  | Стс       | 0.05pF      | 0.025pF    |  |

|    | CTS       | 0.10pF      | 0.03pF     |  |

注: C<sub>TE</sub>(エミッタ~ベース間容量) C<sub>TC</sub>(コレクタ~ベース間容量) C<sub>TS</sub>(コレクタ~基板間容量) らの応力を異方性エッチングにより溝上部にY字形のテーパを設けることや、溝内に $Si_3N_4$ 膜を形成することによって緩和し、結晶欠陥の発生を防止した。また、アイソレーション領域の幅を $1.5\mu$ mに限定することで工程の簡略化も図った。

このU溝アイソレーションと $1.5\mu$ mの微細加工技術を用い、 従来の $2\mu$ mの微細加工技術と酸化膜アイソレーションによる 素子の寸法及び特性が、**表 3** に示すように改良された。特に アイソレーション幅が $8\mu$ mから $3\mu$ mに縮小し素子面積が $450\mu$ m²から $180\mu$ m²に、また $C\tau$ cは0.05pFから0.025pFに、 $C\tau$ sが0.10pFから0.03pFに低減できた。

以上のU溝アイソレーション方式を踏まえ、超高速回路技術により  $4 \, \mathrm{k} \, \mathrm{i} \, \mathrm{k} \, \mathrm{fm} \, \mathrm{i} \, \mathrm{fm} \, \mathrm{fm} \, \mathrm{k} \, \mathrm{fm} \, \mathrm{i} \, \mathrm{fm} \, \mathrm{fm}$

# 3.2 超高速回路技術

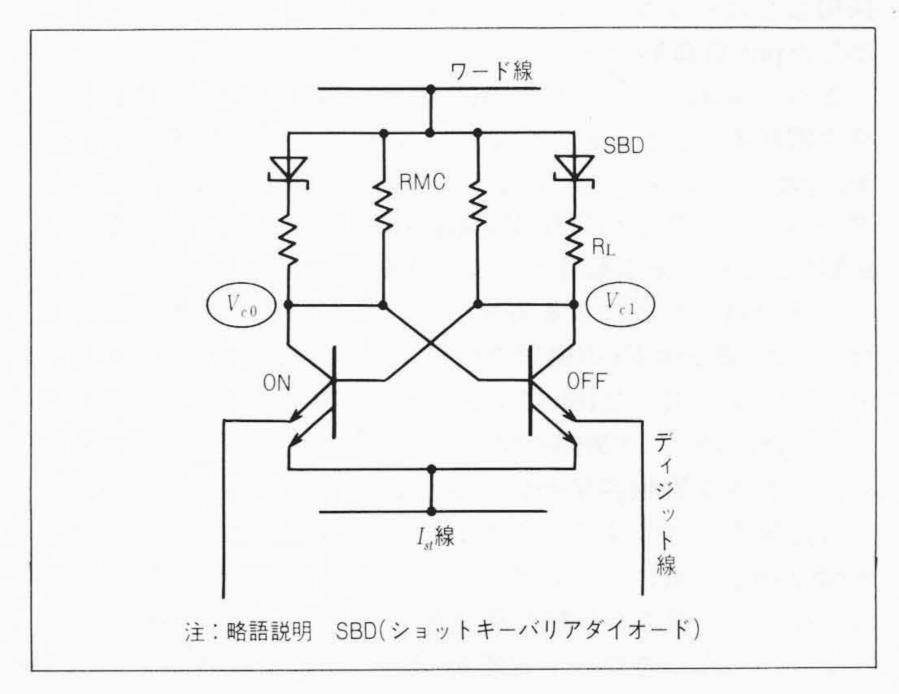

4 kビット/5 nsのECL RAMには,図 $3 \text{ に示す} R_L$ 切換形セルを用いている。このメモリセルは,非選択時に情報保持のためにセルに流れる必要最小限の保持電流Istと,選択時に情報を高速に読み出すために必要な最大限の読出し電流IRの比,すなわち非選択時から選択時(又はその逆)にセルに流れる電流の切り換わる比率IR/Istが大きくとれ,最も高速化に適している。しかし電流切換比を大きくとるために,数十キロオームのコレクタ負荷抵抗 $R_{MC}$ やそれに並列する大きな面積のSBD(ショットキーバリアダイオード)と $N^+$ 埋込み層による低抵抗 $R_L$ が必要であり,セルの構成が複雑で面積が大きくなる。このような複雑な構成のセルを大きな電流切換比で安定に動作させることが,製品化を図る上で重要な課題であった。

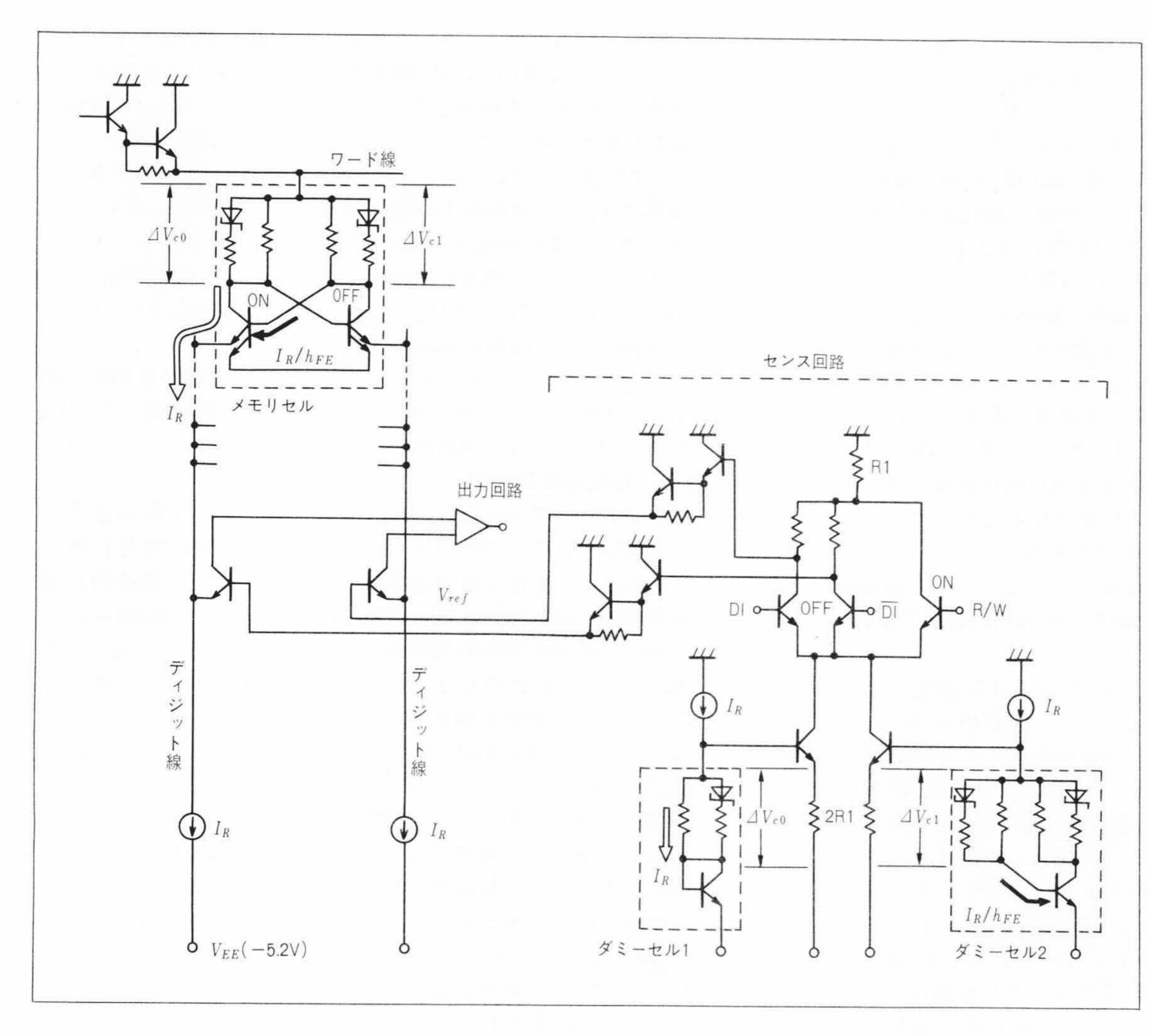

今回、高速性とともに安定な動作マージンを確保するために、図4に示したダミーセルをもつセンス回路を新たに採用した。このセンス回路には、メモリセルと同一構成の二つのダミーセルが配置され、メモリセルのディジット線に流れる電流と同一の電流がダミーセルにも流れる。ダミーセル1とダミーセル2には、読出し電流 $I_R$ と $I_R$ / $I_F$ Eによってメモリセルに発生する $\Delta V_{C_1}$ と $\Delta V_{C_0}$ と全く同一の電圧降下が生じる。これにより読出し/書込み回路の抵抗比を最適化することで、メモリセルの参照電圧Vrefを、メモリセルのオン側トランジスタのコレクタ電圧 $V_{C_0}$ の中間に精度よく設定できる。このVrefと $V_{C_1}$ 及び $V_{C_0}$ との電位差をメモリ $V_{C_0}$ との電位

図 3  $R_L$ 切換形メモリセル  $R_L$ 切換形メモリセルは、読出し電流 $I_R$  と 保持電流 $I_{st}$  の電流切換比率を大きくとれるために、最も高速化に適している。

図 4 ダミーセルをもつ センス回路 メモリセル に生じる $\Delta V_{c1}$ ,  $\Delta V_{c0}$ と全く同 一の電圧降下をダミーセルに 発生させることにより、メモ リセル参照電圧 $V_{ref}$ をメモリ セル電位 $V_{c1}$ ,  $V_{c0}$ の中間に精 度よく設定できる。

ることが安定な動作マージンを得る必要な条件である。本センス回路の採用で、メモリセルのワード線駆動信号の低振幅化が可能となり、十分な動作マージンをもつ、より超高速なECLRAMの製品化を可能とした。

#### 3.3 高速高集積回路技術

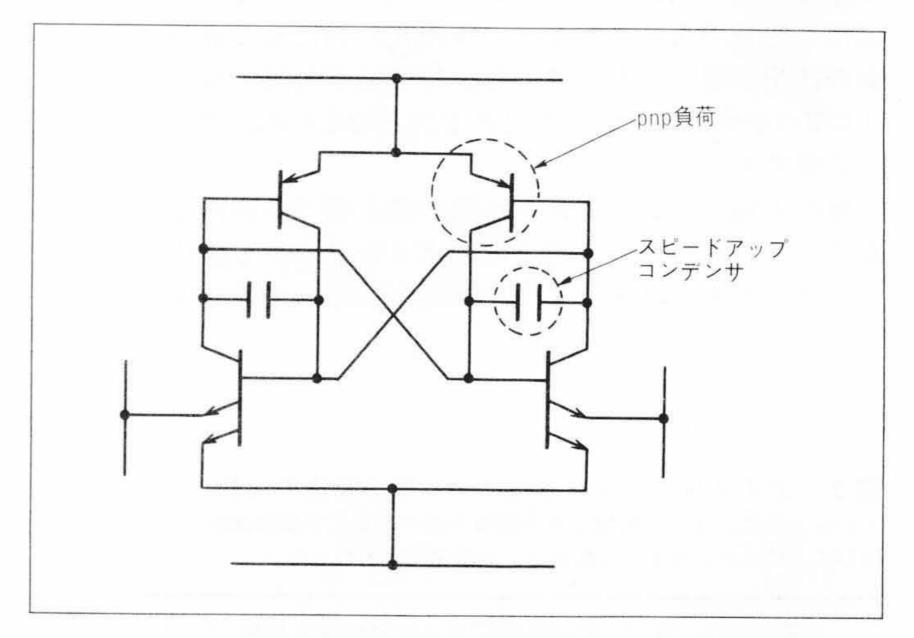

高速な16kビットECL RAMを実現するには、消費電力の面から情報保持に必要なメモリセルに流れる電流Istと、集積度を上げるために面積を最小にすることのできるメモリセルを採用しなければならない。この両方を具備したセルが図5に示したpnp負荷形セルである。

このセルは、メモリセルの振幅(オン側トランジスタのコレクタ電圧  $V_{C_1}$ とオフ側トランジスタのコレクタ電圧  $V_{C_0}$ の差)が、pnpトランジスタのエミッタ~ベース間電圧  $V_{BE}$ とコレクタ~エミッタ間飽和電圧  $V_{CE}$ (SAT.)の差で決まり、 $I_{St}$ を2~3 $\mu$ Aにしても十分な動作マージンが確保でき、かつpnpトランジスタを自己整合による寄生素子により精度よく形成できるため、セル面積が $R_L$ 切換形の約 $\frac{1}{3}$ にできる利点をもっている。

このセルを用いた16kビットの高速高集積RAMの開発に当たっては、特に、128個のワード線駆動回路をデコードするために、大きな寄生容量が付加されるアドレスバッファ回路の信号遅延を小さくすることが必要であった。このため、素子の微細化とともにアドレスバッファ回路を構成するECL回路により多くの電流を分配し高速化を図った。更に128個のメモリセルがつながるワード線駆動回路も同様な観点から高速化を図った。

また,以上の高速化に伴い,任意のメモリセルが非選択状

図5 コンデンサ付きpnp負荷形セル pnp負荷形セルは、メモリセルの低消費電力化と小面積化に優れている。更にスピードアップコンデンサを挿入して、メモリセルの高速応答と動作マージン確保を可能にした。

態から選択状態に移る過渡時で、メモリセルの応答が遅く、その振幅が小さくなり、動作マージンが確保できなくなることが明らかになった。このためメモリセルを構成するトランジスタのコレクタ~ベース間に、スピードアップコンデンサを挿入してメモリセルの応答を高速化し、高速かつ十分な動作マージンをもつ16kビットの高速高集積ECL RAMの製品化

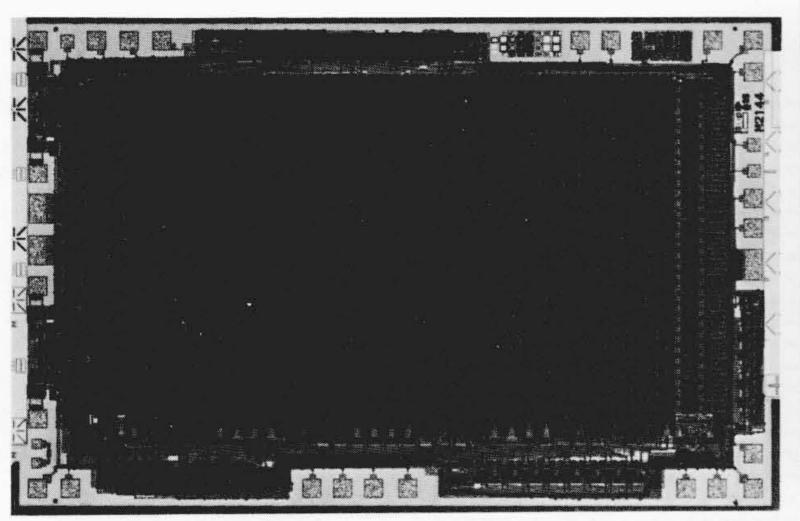

図 6 4 kビット超高速ECL RAM "HM2144" チップ写真 チップサイズは2.87mm×4.46mm=12.8mm<sup>2</sup>である。

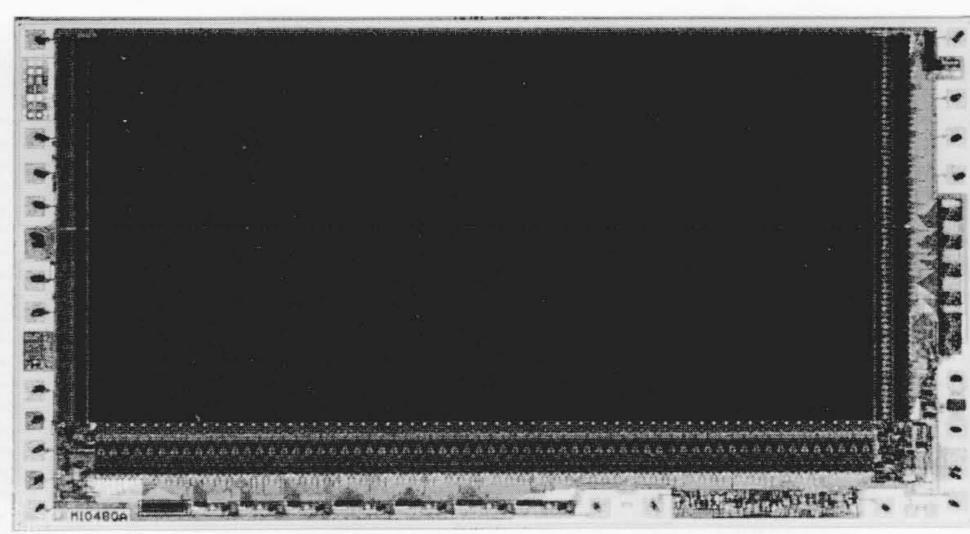

図 9 I6kビット高速高集積ECL RAM "HMI0480-I5" チップ写真 チップサイズは2.96mm×5.60mm=16.6mm²である。

を可能にした。

# 4 性能評価結果

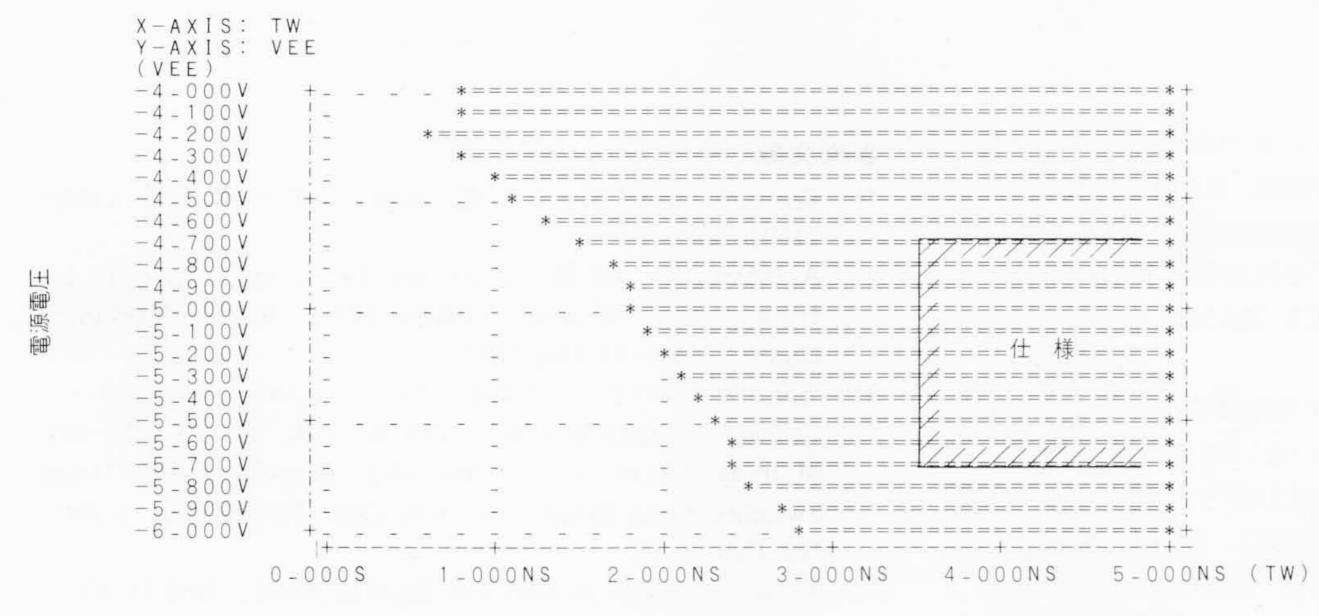

図 6 に今回開発した 4 kビット/ 5 nsの超高速ECL RAM "HM2144" のチップ写真を、図 7、8 には、アドレスアクセス時間と書込みパルス幅の電源電圧依存性の代表例を示す。電源電圧 $-5.2\text{V}\pm10\%$ での最大アドレスアクセス時間は4.5 ns、最小書込みパルス幅は2.5 nsであり、製造条件のばらつき

や使用条件を考慮しても、最大アドレスアクセス時間 5 ns及び最小書込みパルス幅3.5nsの仕様を満たすことができる。このほか、直流特性、交流特性、ファンクション特性、耐α線強度、更には信頼性についても、超高速ECL RAMとしての使用条件で全仕様を満たしており、各種高性能コンピュータのバッファ記憶装置やコントロール記憶装置に用いられ、システムの高性能化が一段と進むものと期待される。

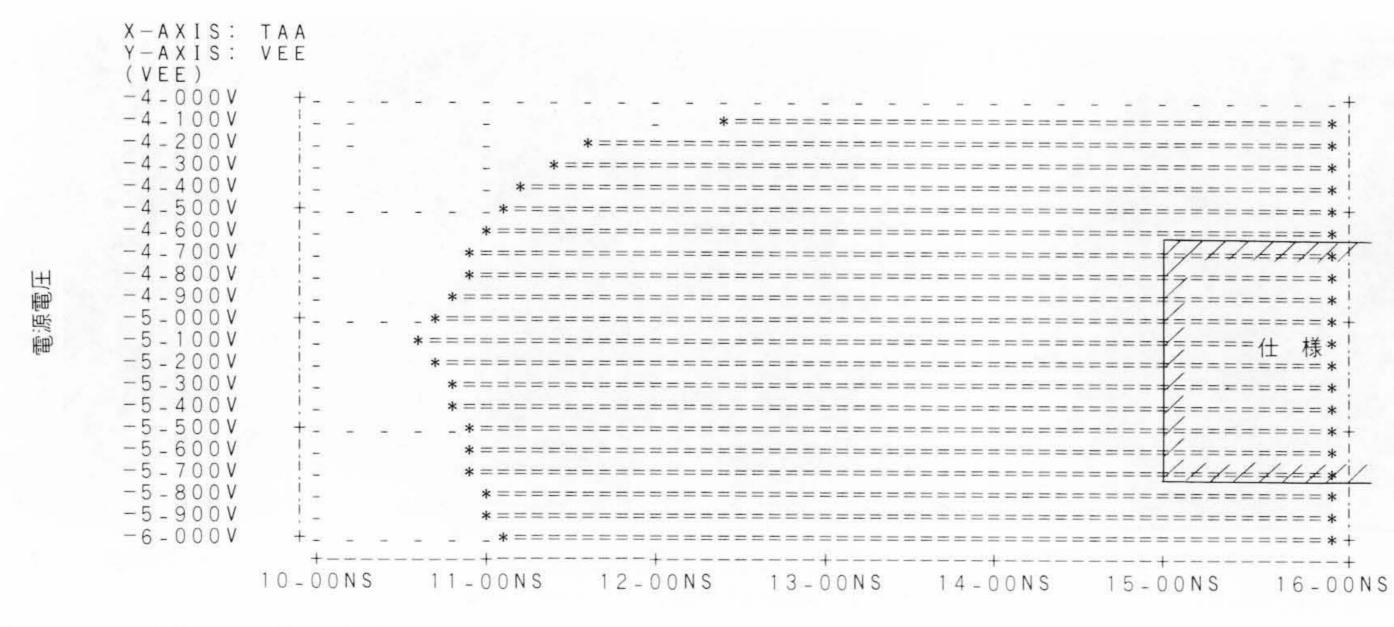

図9に16kビット/15nsの高速高集積ECL RAM"HM10480-

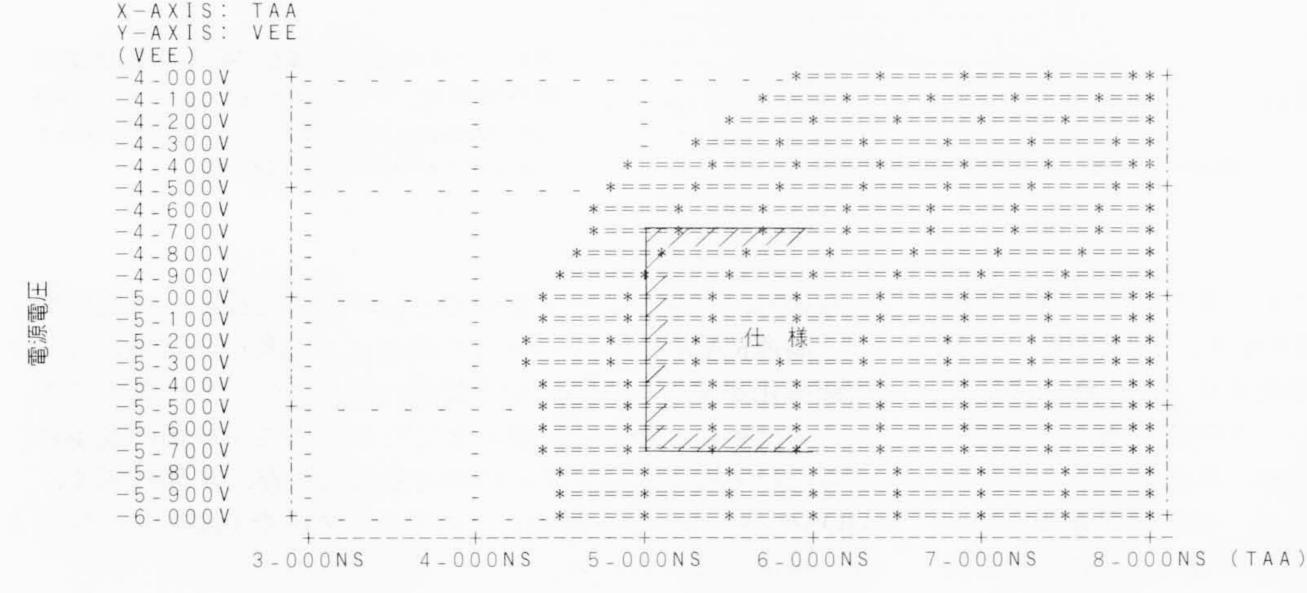

注:\*===が動作している領域を示す。

アドレスアクセス時間

図7 HM2I44アドレスアクセス時 ===\* 間の電源電圧依存性 電源電圧-5.2 8-000NS (TAA) V±10%で最大アドレスアクセス時間は 4.5nsであり、仕様 5 nsを満足する(周囲温度50℃)。

注:\*===が動作している領域を示す。

書込みパルス幅

図 8 HM2I44書込みパルス幅の電源電圧依存性 電源電圧-5.2V±10%で最小書込みパルス幅は2.5nsであり、仕様3.5nsを満足する(周囲温度50℃)。

図10 HM10480-15アドレスアクセス時間の電源電圧 依存性 電源電圧-5.2V± 10%で最大アドレスアクセス時間はII.0nsであり、仕様15nsを 満たすことは明らかである(周囲 温度50℃)。

注:\*===が動作している領域を示す。

アドレスアクセス時間

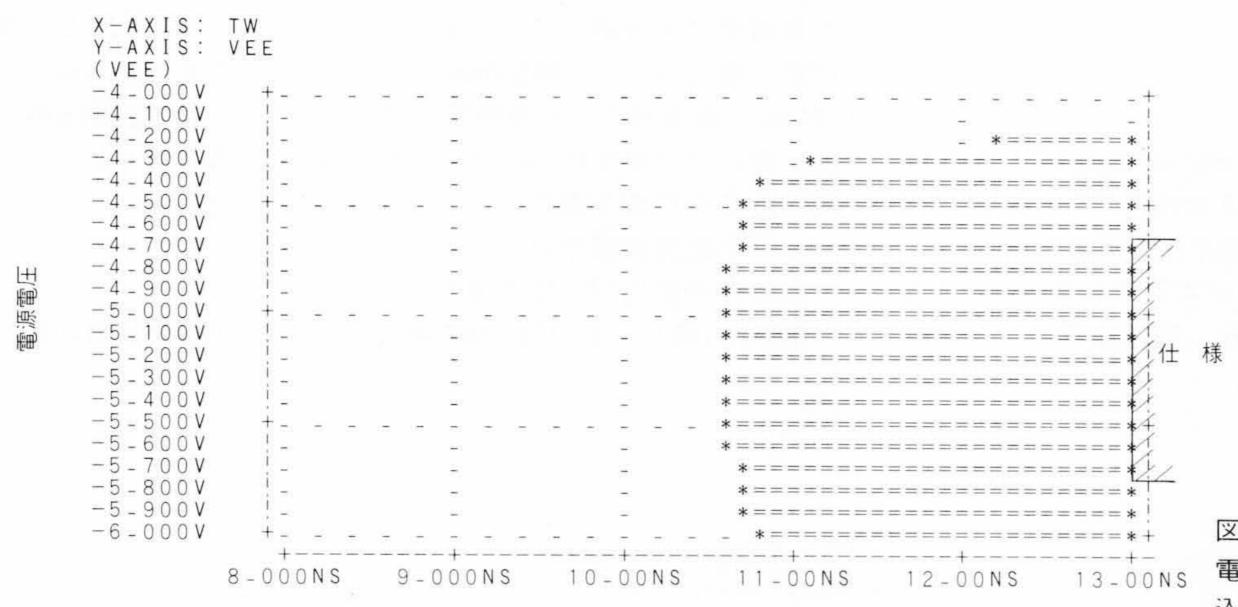

図II HMI0480-I5書込みパルス幅の電源 電圧依存性 電源電圧-5.2V±I0%で最小書 込みパルス幅はI0.7nsであり、仕様I3nsを満たす ことは明らかである(周囲温度50℃)。

注:\*===が動作している領域を示す。

書込みパルス幅

15"のチップ写真を、図10、11にアドレスアクセス時間及び書込みパルス幅の代表的電源依存性を示す。電源電圧-5.2V  $\pm 10\%$ で、最大アドレスアクセス時間は11.0ns、最小書込みパルス幅は10.7nsであり、製造ばらつきや使用条件を考慮しても、最大アドレスアクセス時間15ns、最小書込みパルス幅13nsの仕様を十分満足している。また、直流、交流及びファンクション特性、耐 $\alpha$ 線強度、更には信頼性でも、高速高集積ECL RAMとしての仕様を十分満たしており、各種コンピュータやディジタル画像処理装置、高性能テスタなどの広い用途に使用されると予想される。

今後も、コンピュータを中心とした情報化社会の発展に従い、高速RAMのよりいっそうの高速化、高集積化、更には高信頼度化が望まれることが予想される。このような要求にこたえるために、微細化を中心とした半導体加工技術の進歩によるだけでなく、システムに適合した新回路、実装技術や、MOSやバイポーラを超越した新デバイス技術を開発し、製品化を推進していきたい。

#### 5 結 言

OA化の進展に伴う各種コンピュータの高性能化のために、 需要が高まっている高速バイポーラECL RAMを、U溝アイソ レーション技術や超高速回路及び高速高集積回路技術などを 用いて開発し、最大アドレスアクセス時間 5 nsの 4 kビット ECL RAMや、15nsの16kビットECL RAMシリーズを製品化 した。

これらは、高速性能とともに、十分な動作マージンと耐 $\alpha$ 線強度、更には高い信頼性をもっている。また、多様化する顧客のニーズに対応できるよう、入出力信号レベルやビット構成の異なる 4 kビット、16 kビットのECL RAMの製品化を進めており、今後システムの高性能化に重要な役割を果たすことが期待される。

### 参考文献

- 1) 荻上,外:高速LSIメモリ,電子通信学会誌,67巻,11号,1160~1169(昭59-11)

- A. Hayasaka, et al.: U-groove Isolation Technique for High Speed Bipolar VLSI's, IEEE IEDM Technical Digest, p.62~65 (Dec. 1982)

- 3) 光定,外:α粒子による高速バイポーラRAMのソフトエラー, 電子通信学会論文集(C編),63-C巻,2号,61~65(昭55-02)

- 4) M. Inadachi, et al.: A 6ns 4kb Bipolar RAM Using Switched Load Resister Memory Cell, 1979 ISSCC, p.108~109 (Feb. 1979)

- 5) Y. Kato, et al.: A 16ns 16k Bipolar RAM, 1983 ISSCC, p.106~107 (Feb. 1983)