# メモリ搭載可能な高速CMOSゲートアレーの開発「HG61Hシリーズ」

## Development of High Speed Gate Array with Static RAM "HG61H Series"

高度情報社会の発展に伴いこれに関連する機器の電子化が積極的に図られており、これに相応して短い開発期間、安価な開発費、少量多品種などの特長をもったゲートアレーの需要が増大している。この要求にこたえるため、高速でメモリ搭載可能かつ豊富な機能をもった入出力回路のCMOSゲートアレー「Hシリーズ」の開発を行なった。ゲート数は448ゲートから2,560ゲートまでの6タイプで、Hi-CMOS技術を用い、ゲート1段当たり2nsの遅延時間を実現しメモリ機能搭載を可能とした。

入出力回路機能については、従来に比べて6機能を追加し動作スピードも大幅に改善した。端子数については、多ピン化を図り論理設計の自由度を向上させた。適用パッケージについてはDILP28~FPPの100ピンまで拡大した。

阿部道郎\* Michirô Abe 戸井田徳次\* Tokuji Toida 道下 智\* Satoshi Michishita

#### 11 緒 言

ゲートアレーはカスタムLSIのなかでも配線工程マスクにより所要の論理動作を実現させる特別仕様のLSIである。

概要としてはゲートをあらかじめ配列したチップ上に,回 路仕様に基づいて自動設計された配線マスクによりLSIが実現 できる。フルカスタムと比べて次のような特長が挙げられる。 (1) 短期開発, (2) 安価な開発費, (3) 少量多品種の生産が可能で ある。また、ゲートアレーの実現手段として、大別してバイ ポーラ形とCMOS形(Complementary Metal Oxide Semiconductor) に分けられる<sup>1)</sup>。バイポーラ形の特長として は、ゲート1段当たりの遅延時間(ファンアウト3, AL配線 3 mm 負荷)が0.3~1nsのECL(Emitter Coupled Logic)形と1~ 4nsのTTL(Transistor Transistor Logic)形に分けられる が、消費電流はゲート当たり0.5~5mW程度と大きく、集積 度も3,000ゲート程度と比較的小さい。CMOS形の消費電流は 動作周波数に比例するが、TTLと比較すると約一けた程度少 ない。ゲート遅延は1.5~4nsでTTL同等あるいはそれ以上 のものも商品化されているが,外部負荷の駆動能力では劣っ ている。集積度については、加工技術の進歩とゲートアレー をサポートしている自動設計の進歩と同期して向上している。 今まで述べてきたように、低消費電流、ECLに迫る高速性が 実現可能, 高集積化が可能という理由で, CMOSゲートアレ ーが主流になってきている。その他に最近ROM(Read Only Memory), RAM (Random Access Memory) によるメモリ機 能内蔵可能, Bi-CMOS (Bipolar-CMOS) などの複合タイプの ゲートアレーが発表されている2)。

本稿ではメモリ機能内蔵搭載可能でゲート遅延時間 2 ns, 入出力回路の多機能化を実現したHG61Hシリーズ(以下, Hシ リーズと略す。)の 6 タイプのベースチップの開発について述 べる。

#### 2 目標仕様

表1に目標仕様を示す。一般的な電子機器でコンピュータのメインフレームなどの特別な分野を除けば、標準TTLの動

作速度で十分である。TTL以上の高速動作が実現できれば、動作スピードのマージンが十分取れることを意味し、電子機器自体の品質向上にもつながる。Hシリーズではユーザーニーズの高い24MHz動作にも耐えられるゲート遅延時間として2nsを設定した。メモリ搭載については、HD61MMシリーズと同様にスタティックRAMによるものとする。

入出力回路は、(1) TTLレベルシュミット、(2) CMOSレベル、(3) CMOSレベルシュミット、(4) プルアップ抵抗、(5) プルダウン抵抗、(6) 水晶発振、の6機能を従来機能に追加設定した。

入出力端子数については従来よりも多ピン化を図り、端子 当たりのゲート数を少なくすることにより論理設計での自由 度の向上を図るように設定した。

ゲート数区分についてはHD61J/K/L/MMの区分を見直し、448ゲート $\sim 2,560$ ゲートの6タイプを設定し細分化を図るように設定した。

パッケージについては多ピン化のニーズに対応するために、 従来タイプに面付きタイプのFPP100ピンを追加し、プラスティックパッケージによりDILP28~FPP100ピンまで6タイプ の適用展開が図れるように設定した。

#### 3 デバイス設計

#### 3.1 高速化の実現

高速化についてはゲート1段当たりの遅延時間を少なくすることによりLSIの高速化が達成されるが、その実現手段として一般的にはMOSトランジスタの平面構造のスケールダウン(比例縮小)の方法が採用されている³)。ゲート遅延時間とMOSトランジスタサイズの関係は比例関係にあり、トランジスタサイズの縮小による効果が最も効果的である。

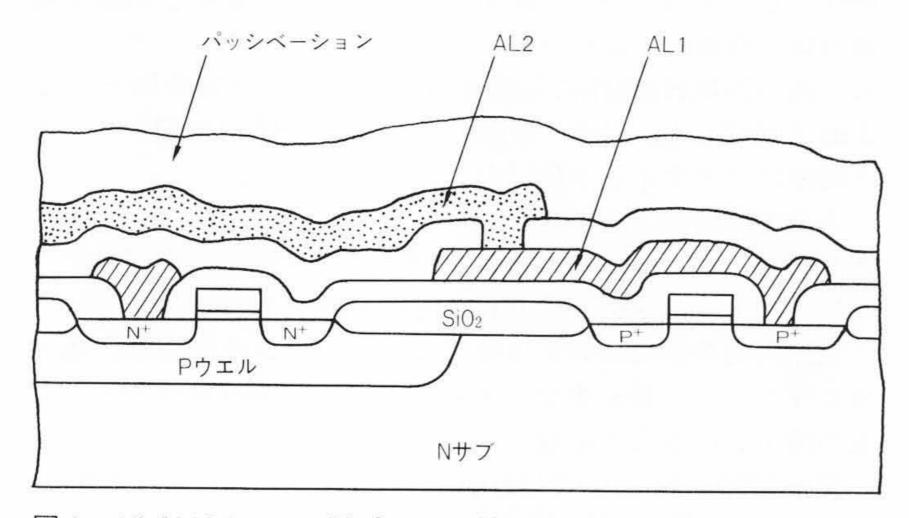

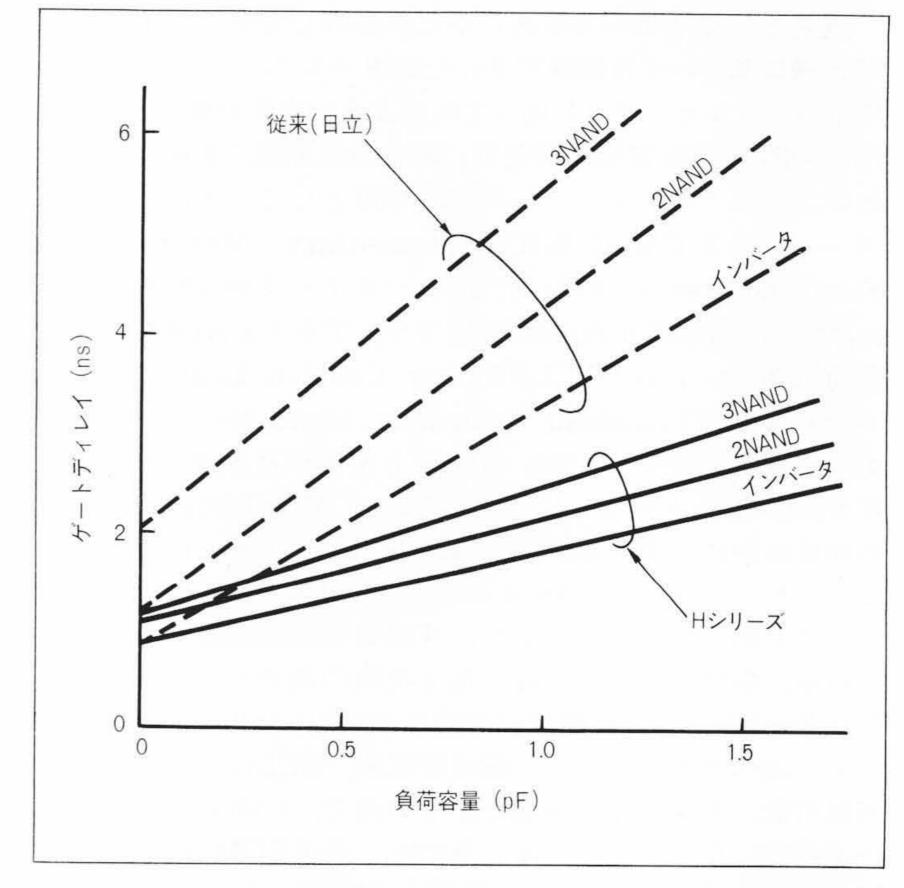

Hシリーズのゲート用のセルはゲート長2.0µmで設計を行なった。製造プロセスは図1に示す信頼性が高くコストパフォーマンスのあるHi-CMOS AL2層プロセスを採用した。その結果、ゲート遅延時間と負荷容量の関係を図2に示す。

内部ゲートの従来品(3 µmプロセス)をHシリーズの各論理

表 I HG61Hシリーズの仕様概要 従来品に比べ高速動作、入出力バッファの機能、パッケージ展開に大幅な改善がみられる。

| 項目                          | 形式      | HG61H04*                  | HG61H06              | HG61H09                          | HG61H15                                    | HG61H20                          | HG61H25*                         | (当社従来品<br>HD61MM                 |

|-----------------------------|---------|---------------------------|----------------------|----------------------------------|--------------------------------------------|----------------------------------|----------------------------------|----------------------------------|

| ゲート数                        | 内 部     | 448                       | 660                  | 968                              | 1,560                                      | 2,010                            | 2,560                            | 2,496                            |

|                             | RAM     | 8 b× 8 w                  | $12^b\!\times\!12^w$ | 16 <sup>b</sup> ×16 <sup>w</sup> | $16^{\mathrm{b}}\!\times\!24^{\mathrm{w}}$ | 16 <sup>b</sup> ×28 <sup>w</sup> | 16 <sup>b</sup> ×32 <sup>w</sup> | 16 <sup>b</sup> ×32 <sup>w</sup> |

| 端 子 数                       | (電源含む。) | 56                        | 68                   | 82                               | 86                                         | 98                               | 110                              | 108                              |

| ゲートディレイ<br>ns typ<br>(標準負荷) | 入力      | 7.7                       |                      |                                  |                                            |                                  |                                  | 9.0                              |

|                             | 内 部     | 2.0                       |                      |                                  |                                            |                                  |                                  | 3.5                              |

|                             | 出力      | 9.5(C <sub>L</sub> :50pF) |                      |                                  |                                            |                                  |                                  | 20                               |

| メモリアクセスタイム (ns) 40typ       |         |                           |                      |                                  |                                            |                                  |                                  | 60typ                            |

| 入 出 力                       | レベル     | TTL, CMOS, シュミット, レベル可能   |                      |                                  |                                            |                                  |                                  | TTLのみ                            |

|                             | 機能      | トライステート、トーテムポール、入出力組合せ    |                      |                                  |                                            |                                  |                                  | -                                |

|                             |         | プルアップ, プルダウン, 水晶発振回路可能    |                      |                                  |                                            |                                  |                                  | 不可                               |

| 消費                          | 電 流     | 175μW/ゲート                 |                      |                                  |                                            |                                  |                                  | 130                              |

| パッケージ                       | DILP28  | 0*                        | 0                    | 0                                | 0*                                         | _                                |                                  | _                                |

|                             | DILP40  | 0*                        | 0                    | 0                                | 0                                          | 0                                | 0*                               | _                                |

|                             | DILP64  | 0*                        | 0                    | 0                                | 0                                          | 0                                | 0*                               | 0                                |

|                             | FPP64   | 0*                        | 0*                   | _                                | =                                          | _                                | _                                | -                                |

|                             | FPP80   |                           | 0                    | 0                                | 0                                          | 0*                               | _                                | _                                |

|                             | FPP100  |                           | <u></u>              | _                                | _                                          | 0*                               | 0*                               | 0*                               |

注:略語説明など CMOS(Complementary Metal Oxide Semiconductor), TTL(Transistor Transistor Logic) DILP(Dual In Line Plastic), FPP(Flat Plastic Package) \*(開発中を示す。)

図 I Hi-CMOS AL 2 層プロセス断面図 Pウェルを用いたCMOS AL 2 層配線プロセスの断面を示す。

機能別に比較すると、単純に比較ができないので、2入力 NANDで負荷容量はファンアウト 3、AL配線 3 mmが負荷として出力に付いた場合の比較を行なう。この条件で従来品の 2入力 NAND 1 段当たりの負荷容量としては次段トランジスタ 3 個分のゲート容量、基板一ジャンクション間の寄生容量、AL配線 3 mm分の配線容量をそれぞれ加算した平均値が0.75 pFとなり、 $\mathbf{2}$  から遅延時間は3.5nsとなる(ただし、負荷容量については使用プロセスの層間膜厚、ゲート酸化膜厚により決定される)。同様に $\mathbf{H}$ シリーズの負荷容量を求めると、0.75 pFとなり、ゲート遅延時間は2 nsの結果が得られ従来と比較して1.7倍の改善がなされ、所期目標を達成した。

### 3.2 入出力回路の多機能化の実現

今後ゲートアレーがいろいろな電子機器へ組み込まれる場合,市販されている標準ICとのインタフェースが可能でなければならない。Hシリーズでは従来品に下記の機能を追加した。

- (1) CMOSレベル入力

- (2) TTLレベルシュミット入力

- (3) CMOSレベルシュミット入力

図 2 ゲートディレイと負荷容量 高速化については、従来品とHシリーズでは約1.7倍の改善がなされている。

- (4) プルアップ抵抗

- (5) プルダウン抵抗

- (6) 水晶発振回路

示す。

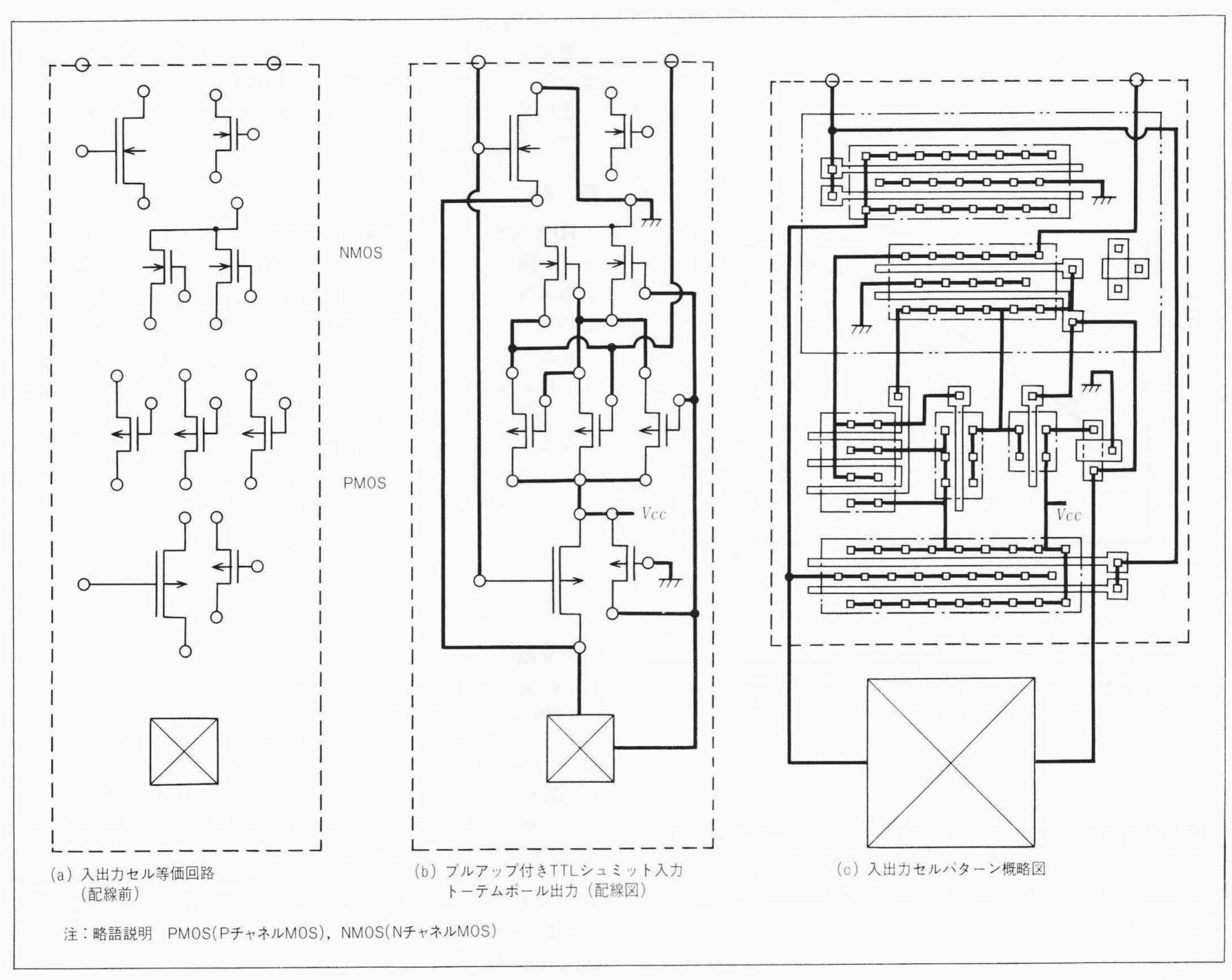

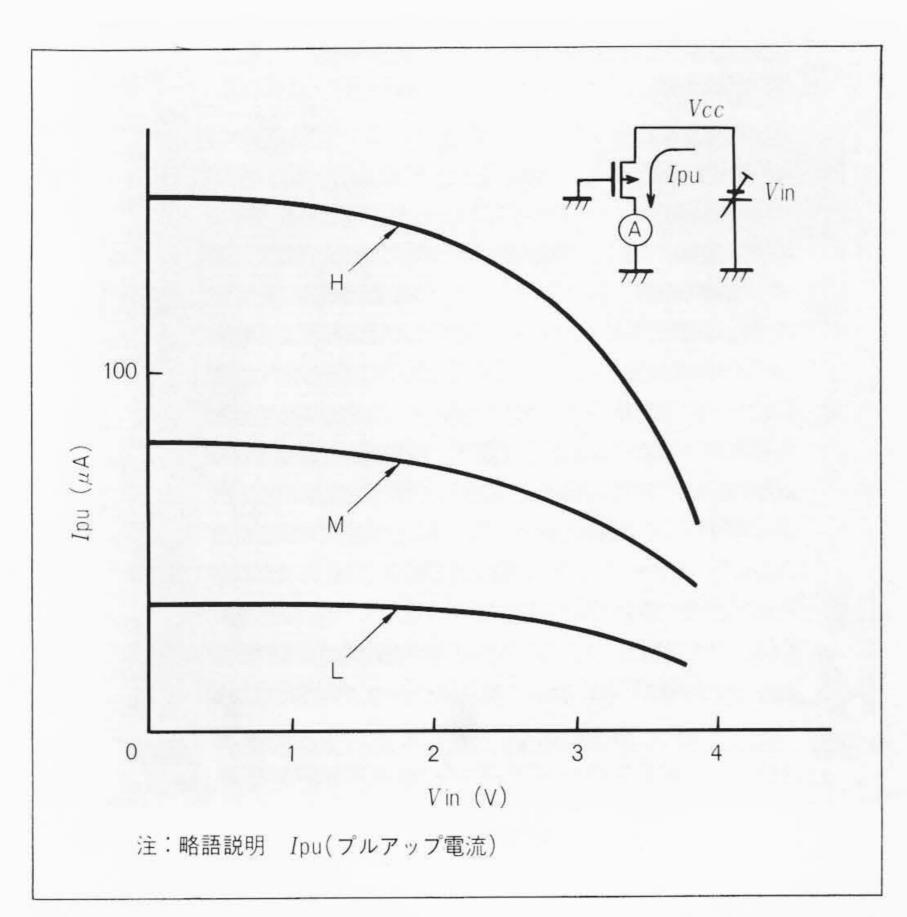

図3に多機能入出力回路の概略図を示す。各機能の実現手段は従来品に比べ種々なサイズのトランジスタを配置しておき,機能ごとにトランジスタを結線して実現するようにした。 図4に新しく追加したプルアップの3種類の電気的特性を

#### 3.3 メモリ機能搭載の実現

ゲートアレーの集積度が向上するにつれて1チップである

MOSトランジスタサイズの異なる各種サイズのトランジスタを結線することにより、いろいろな機能の入出力回路が構成可能に 多機能入出力回路 図 3 なる。

3種類のプルアップMOSの電流と電圧 プルアップ抵抗の特性 の関係を示す。

程度のシステムが可能となり、メモリ機能をゲートアレー内 部へ組み込む要求が出てきている。基本的にはフリップフロ ップでメモリ機能は構成可能であるが、使用されるゲート数 が多いためメモリがチップを占有する面積が非常に広くなり 効率が悪くなる。

Hシリーズでは日立製作所で開発したHD61MMシリーズと 同一設計法を採用することにより、スタティックRAMによる メモリ機能が搭載可能となった。

#### 3.4 多ピン化の実現

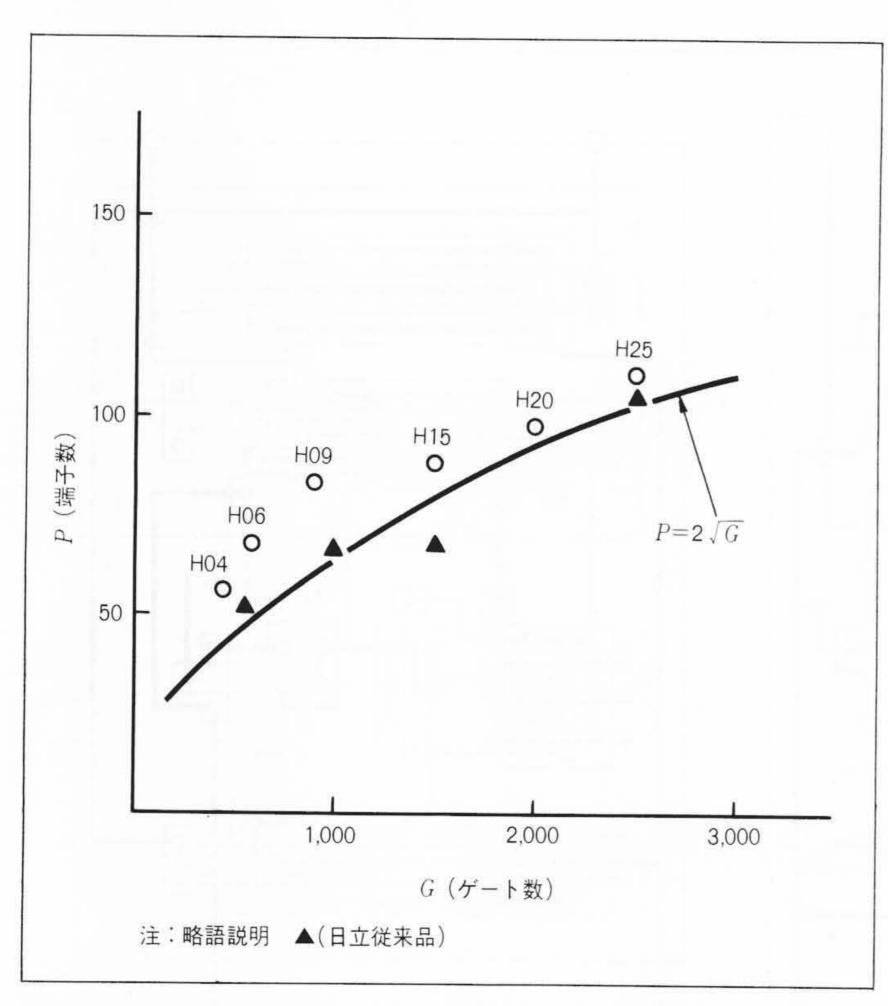

微細加工技術が向上するにつれてチップに搭載できるゲー ト数は増加する。しかし入出力端子数については、実装する パッケージにより制限される。最大ピンのパッケージに合わ せて入出力端子数を決定した場合,ゲート数の少ないチップ にまで適用するとチップサイズが大きくなり、製品の原価は 上昇し経済性が無くなってしまう。そこでこの問題について は、内部ゲート数と最適ピン数との関係かについてある提案が なされており、Hシリーズは今までの他社状況、経験により最 少端子数を $P=2\sqrt{G}$ とした(P:入出力端子数,G:ゲート 数)。そこで最終的には、下記の項目との整合性をとりながら 入出力端子数を決定した。

- (1) 内部ゲート数から推定される最適端子数

- (2) 適用パッケージのピン数

従来品と比較して多ピン化が 図5 入出力端子数とゲート数の関係 図られており、設計の自由度も改善された。

#### (3) チップサイズ(経済性)

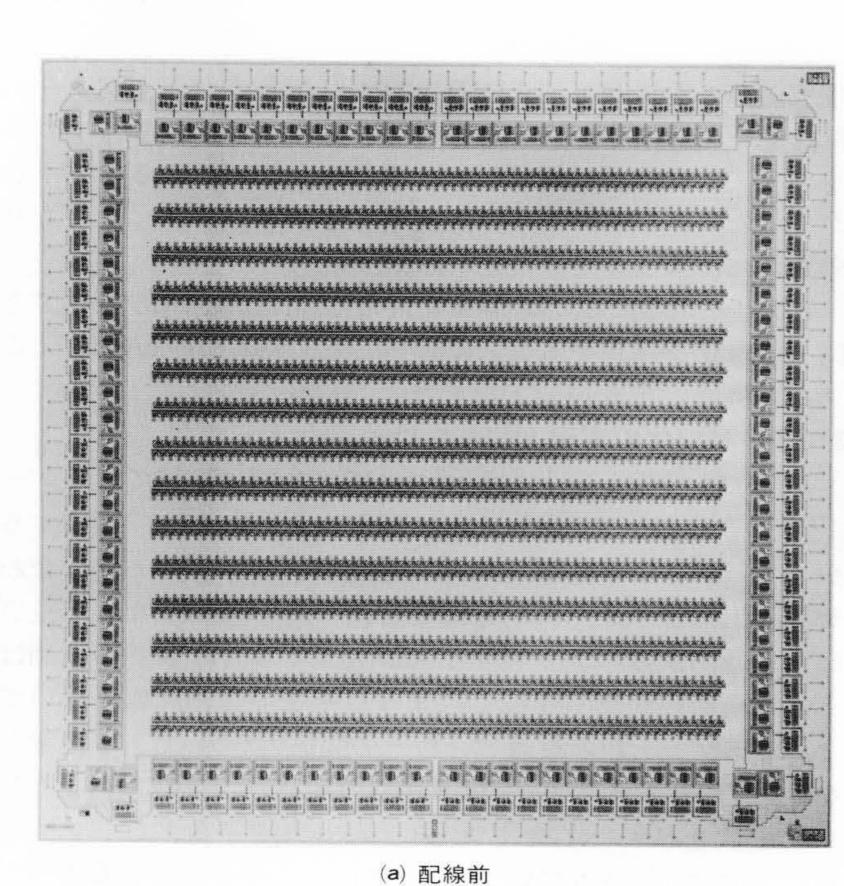

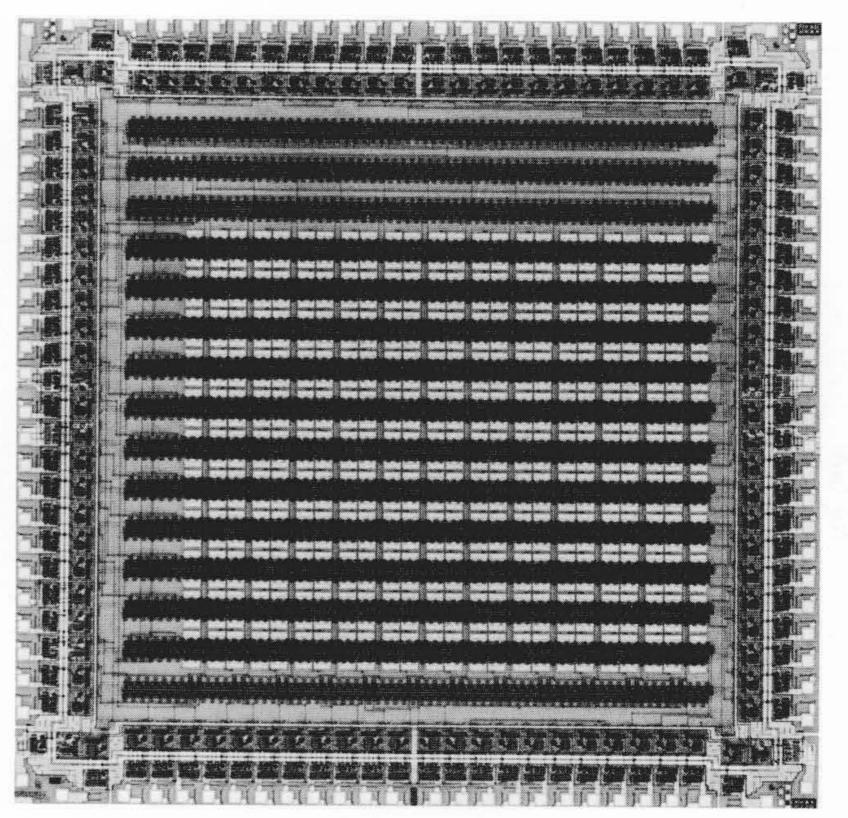

図5に従来品との比較結果を示す。特にユーザー需要の多 いクラスについては, 大幅な多ピン化を図り論理設計段階で の自由度を向上させた。図6にHG61H20の配線前と配線後の 写真を示す。

#### 3.5 豊富な適用パッケージ

適用するパッケージについては, 従来パッケージ系列に多 ピン化対応のためFPP100ピンを追加した。

また重点的にコストパフォーマンスの良いプラスチックパ ッケージとの組合せを可能とした。

#### 4 結 言

Hi-CMOS, AL2 層技術を使用してHG61Hシリーズの 6 タ イプを開発した。ゲートディレイ 2 ns, スタティックRAMに よるメモリ機能搭載可能,豊富な入出力回路機能,多ピン対 応のパッケージを備えたCMOSゲートアレーはパーソナルコ ンピュータ,ワードプロセッサ,ファクシミリなどのOA機器 及びあらゆる分野のシステムへ適用され、新しくゲートアレ 一の応用分野を広げてゆくものである。

今後ゲートアレーはますます高速化、高集積化、多機能化 し, そのマーケットニーズは高まっていくので, ニーズに的 確にこたえるゲートアレーを開発してゆきたい。

#### 参考文献

- 市場が急成長し始めたゲートアレイ: 日経エレクトロニクス, No.311, p.111(1983.2-28)

- 鳥居,外:複合形ゲートアレイの開発,日立評論,66,7,535 ~539(昭59-7)

- Dennarc.R.H: Design of Ion-implanted Mos FETS with Very Small Physical Dimensions, IEEE J. of Solid-State Circuits SC-9 pp. 256~268 (1974)

- Landman.B. et al.: On a Pin Versus Block Relationship for Partitions of Logic Graphs, IEEE Trans Computers-20 pp.  $1469 \sim 1476 (1971)$

(b) 配線後

図 6 HG61H20チップ写真 チップサイズ7.38mm×7.50mmの内に2,010ゲートのベースセルと98入出力端子(電源を含む。)が実装されている。