# プラント制御用PC(プログラマブルコントローラ) "HISEC 04-M"

# PC(Programmable Controller) "HISEC 04-M/D, DG for Industrial Plant Control

制御システムの分散化、全ディジタル化が進む中で、電気制御技術者が容易に取り扱える制御装置としてPCは、機能、性能の両面で発展を遂げてきた<sup>1),2)</sup>。また、最近の制御システムは大規模複雑化する一方で、製品品質、生産性の向上などのニーズが一段と強まり、より高機能で高速制御に対応でき、かつハードウェア・ソフトウェア両面でのミニマム インタフェースを実現するPCが要望されている。

日立製作所では、高性能化(当社HISEC 04-E比 2 倍)を図るとともに、プロセス入出力装置を共有するマルチコントローラ構成が可能で、また光多重伝送装置の採用などにより経済性を追求したPC "H-04-M/DG"を完成し、最適分散システムを構築できるようにした。

高倉満郎\* Mitsurô Takakura

天日康博\* Yasuhiro Tennichi

加藤享良\* Takayoshi Katô

山岡弘昌\* Hiromasa Yamaoka

# 1 緒 言

鉄鋼,火力,原子力をはじめとする産業制御システムは,省力化,省エネルギー,製品品質の向上などを背景とした高度な制御に対応するため,高級な演算はもとより,機能分散や危険分散を指向した小規模から大規模にわたる分散制御システムが求められている。このように多様化,高度化するニーズに対応すべく,高性能,高信頼性,高保守性,経済性,更新のしやすさなどの追求<sup>2),3)</sup>はもとより,PI/O(プロセス入出力装置)及びリンケージハードウェア,アプリケーションドキュメント削減などハード,ソフト両面にわたるミニマム インタフェースを基本コンセプトとするPC(プログラマブルコントローラ)HISEC 04-M/D及びHISEC 04-M/DG(以下,H-04-M/D,DGと略す。)を完成し,既に多数のプラントへ適用している。

以下, H-04-M/D, DGの概要, 機能, 代表的なシステム構成及びプログラミング・デバッグ装置PADT (Programming and Debugging Tool)の機能について述べる。

#### 2 HISEC 04-M/D, DGの特長

H-04-M/D, DGは次のような指針のもとに開発した。

- (1) 制御システムの構築に当たり、ハードウェア及びソフトウェア両面からインタフェースのミニマム化が可能な最適分散制御システムの実現

- (2) 高速・高性能制御装置の実現

- (3) 信頼性・保守性の向上

- (4) システム構成能力の強化

分散制御システム内のインタフェース用ハードウェアを最小にするには、PI/OやPC間リンケージデータを共用することが有効である。H-04-Mによる分散システムでは、バス結合装置によるインタフェース最小化を実現し、制御装置の盤面数を削減している。

更に高機能化のため、H-04-M/D、DGは、ビット演算(シーケンス処理)とワード演算の混在実行処理機能、フローティング演算機能、関数機能、アドレス修飾機能などのDDC (Direct Digital Control) 処理能力の増強を図るとともに、高速化のた

めこれら機能をマイクロプログラム方式により実現している。 プログラミング・デバッグ装置としてCRT (Cathode Ray Tube)付きPADTを採用し、現場でのプログラム作成、修正、編集を容易にするとともに、プログラムをビジュアル化し図面との対応性も向上している。また、上位計算機リンケージ装置、PC間リンケージ装置、各種PI/Oの充実により、幅広いシステム構成を可能としている。なお、コントローラシリーズとしては、DDC専用のH-04-M/Dも用意し、用途に応じH-04-M/DGと使い分けが可能である。

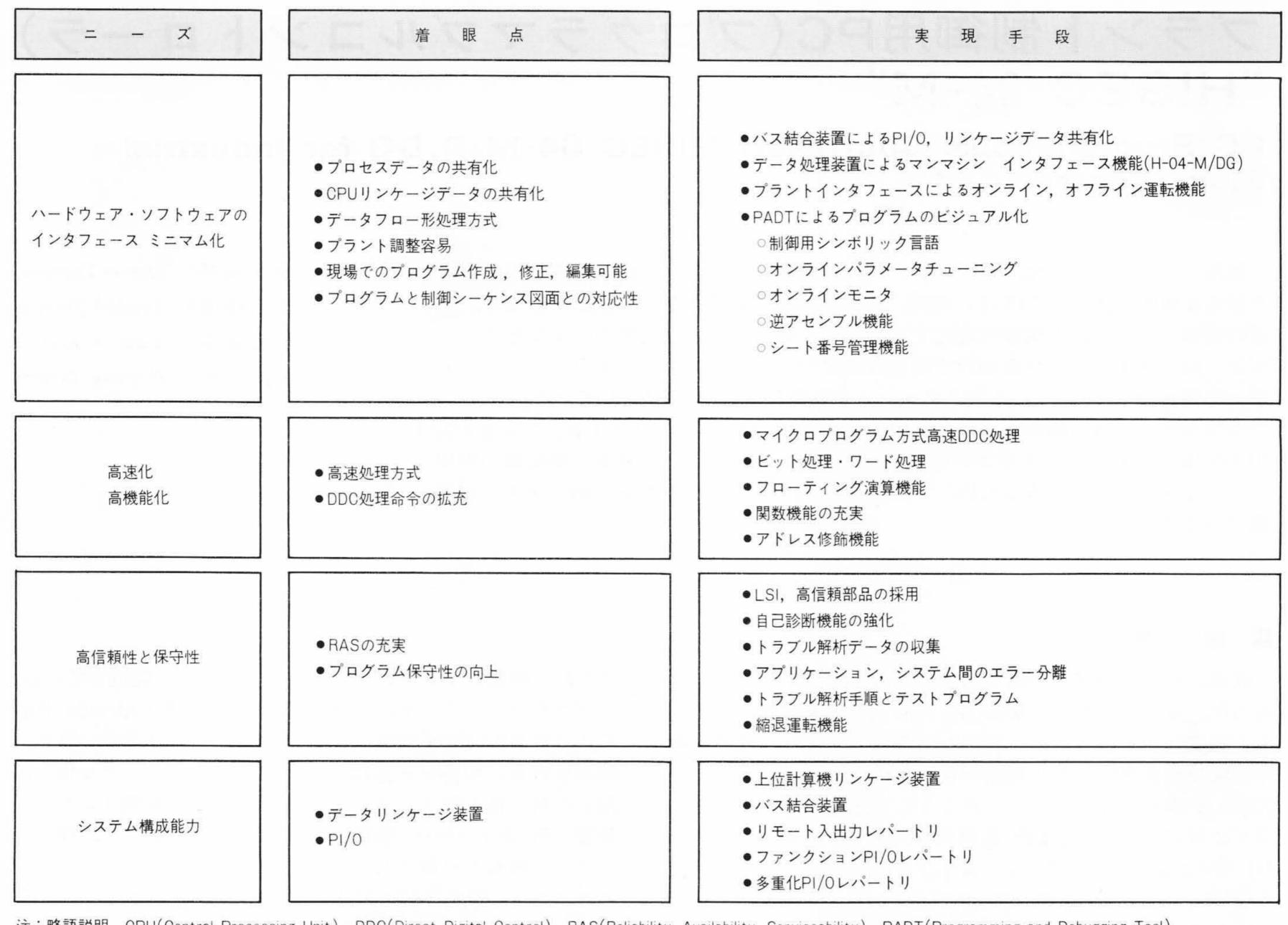

図1にH-04-M/DGの特長を示す。

#### 3 応用システム構成例

H-04-M/D, DGは, スタンド アロン コントローラシステム, バス結合装置によるマルチコントローラシステム, マルチPI/Oを使用した多重化コントローラシステムなど各種システム構成が可能である。

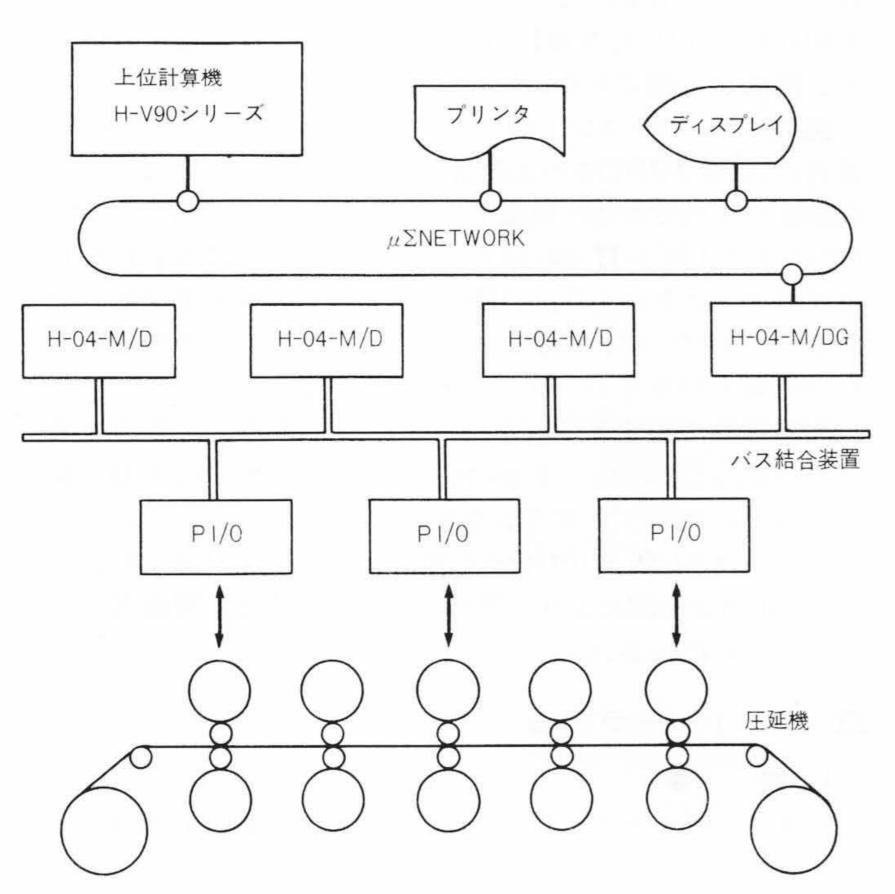

図 2 に、マルチコントローラシステム構成の一例を示す。複数台のPC及びPI/Oをバス結合装置で結合することにより、PI/O情報とPC間で共通に使用するデータの共有化を行なう。また、PCのうち1台を H-04-M/DGとし、これに  $\mu\Sigma$ NETWORKを接続することにより、HIDIC V90システムを上位計算機とするネットワークシステム、CRT及びプリンタを接続してデータ処理も行なうシステムを構成できる。

高信頼性が必要とされる場合には、三重化システムを提供している。この場合、3台のCPUにマルチポートPI/Oを接続し、各々に同一プログラムを実行させておく。プラント入力信号は各々のCPUがPI/Oから読み出し、ディジタル出力信号は2 out of 3 論理により、アナログ出力信号は中間値選択により、外部に出力される。

### 4 コントローラ構成

# 4.1 概 要

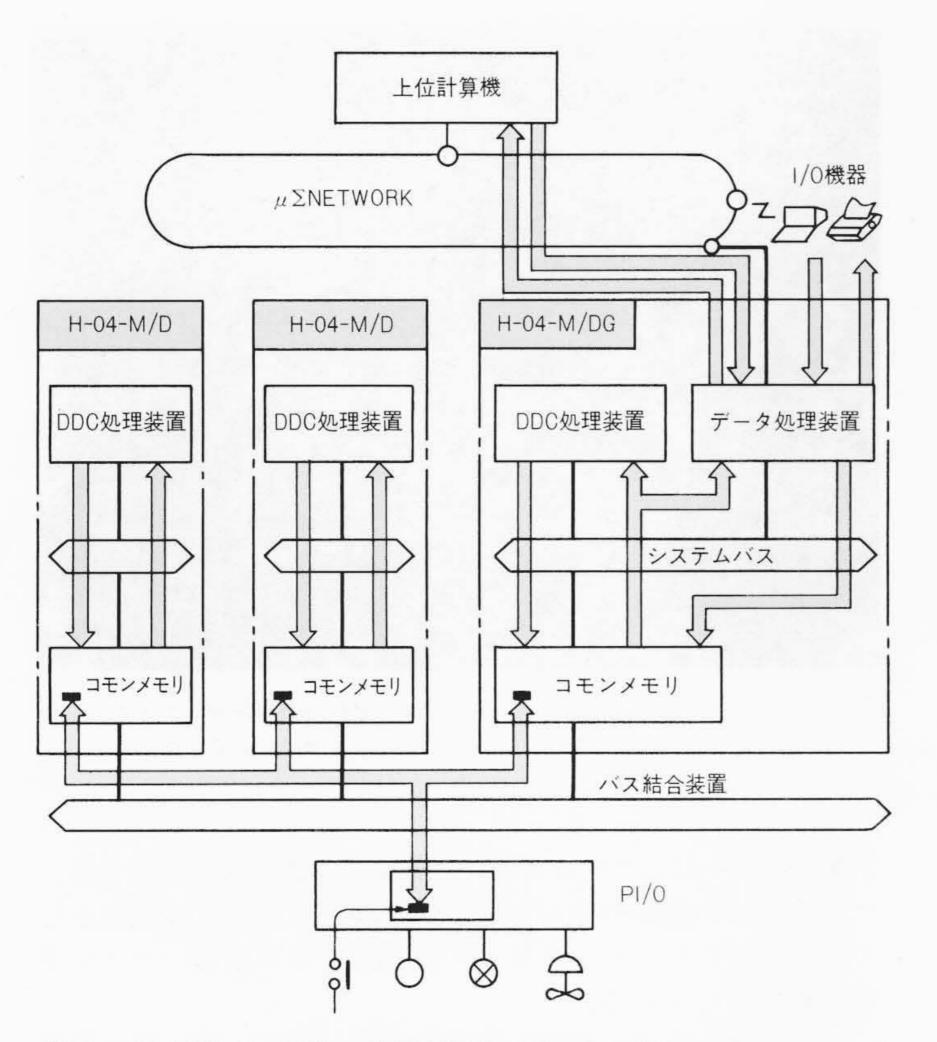

図3に、マルチコントローラシステムでのH-04-M/D, DG

<sup>\*</sup> 日立製作所大みか工場

注:略語説明 CPU(Central Processing Unit), DDC(Direct Digital Control), RAS(Reliability, Availability, Serviceability), PADT(Programming and Debugging Tool) PI/O(Process Input/Output)

図 I HISEC 04-M/DGの特長 HISEC 04-M/DGの特長であるインタフェースミニマム、高速高性能、高機能化、高信頼性と保守性、システム構成能力強化を実現する具体的事項を示す。

図 2 HISEC 04-Mのシステム構成マルチコントローラシステム バス結合装置 $\xi \mu \Sigma NETWORK$ によるマルチコントローラ構成を示す。

の構成とデータの流れを示す。

H-04-M/DGは、PI/Oを介して対象プロセスを高速に制御するDDC処理装置と、I/O機器制御や上位計算機とのネットワーク制御を行なうデータ処理装置の二つの処理装置で構成される。一方、H-04-M/Dは、DDC処理装置だけで構成される。両コントローラは、PI/O情報とコントローラ間で共通に用

両コントローフは、PI/O情報とコントローフ間で共通に用いるデータをコモンメモリを介して共有する構成を採り、マルチコントローラ間のインタフェースハードウェアを最小化している。

# 4.2 処理装置

表1にDDC処理装置とデータ処理装置の仕様を示す。

両者の違いは、DDC処理装置がデータフロー形のプログラムによりビット演算とワード演算を高速に実行し、データの入出力先はプロセスが主であるのに対し、データ処理装置はデータのフォーマット変換や編集などの処理を高速に実行し、データの入出力先はI/O機器や上位計算機が主である。そのため、DDC処理装置は、ビット情報を処理するシーケンス命令と、アナログ量に対する数値情報を処理する数値演算命令とを混在して高速に実行するアーキテクチャを採っている。更に、水平形のマイクロプログラム技術の活用、及びパイプライン処理方式を採用し、制御用のシンボリック(マクロ)言語を直接高速で実行できるようにしている。また、インタフェ

図3 HISEC 04-M/D, DGの構成とデータの流れ HISEC 04-M/ D, DGコントローラは、コモンメモリ上に共有データをもつ。更にHISEC 04-M/DGコントローラ内でもDDC処理装置とデータ処理装置のデータ共有化を図 り、インタフェースの効率化を実現している。

ースはPI/Oも含めメモリインタフェースに一本化し、取扱い を容易にしている。

一方, データ処理装置はデータ編集などが主な処理である ため,バイト処理機能をもっており、主記憶には大容量メモ りを使用している。

両処理装置は、個別の主記憶を設けているが、PI/O入出力 情報や共通データはコントローラ内部のシステムバスを用い て共有できるマルチプロセッサ構成を採っている。

## 5 信号伝送装置

H-04-M/DGに接続される伝送装置は各種あり、用途に応じ て機種が選択できる。表2に伝送装置のレパートリを示す。

#### 5.1 光STU(Signal Transmission Unit)

構内伝送用装置として高速・大容量化及び耐ノイズ性の向 上のため、光伝送技術を導入した光STUを開発した。光STU はシリアルサイクリック方式を採用しており、下記の特長が ある。

- (1) 端末機器間の伝送、コントローラのリモート入出力、コ ントローラ間の小容量データリンケージなどに適用できる。

- (2) コントローラ側での伝送用ソフトウェアは不要である。

- (3) 従来の電気式のSTUにも接続できる。

- (4) 1回線当たりディジタル量256点(16ワード), 伝送周期0.5 msと高速化した。

#### 5.2 バス結合装置

バス結合装置は、H-04-M/D, DGとPI/O間の高速データ転 送を行なう。各H-04-M/D, DGはPI/O情報, リンケージ情報 を共有するため,システムの負荷分散,機能分散に効果があ

表 I DDC処理装置とデータ処理装置の仕様 DDC処理装置は、データフロー形のプログラミングによりシーケンス演算と数値演算の両者を高速に実行 する。一方、データ処理装置はCRT、プリンタなどのI/O機器に対するデータ編集を効率的に処理する。

|                    |                                         |             |              | <b>社</b>                   |             |  |

|--------------------|-----------------------------------------|-------------|--------------|----------------------------|-------------|--|

| 項目                 |                                         |             |              | DDC処理装置                    | データ処理装置     |  |

| CPU                | 演算方式                                    | 繰返し演算方式     |              | 0                          |             |  |

|                    |                                         | 周期起動演算方式    |              | 0                          | 0           |  |

|                    |                                         | 割込起動演算方式    |              | 0                          | 0           |  |

|                    |                                         | プログラム起動演算方式 |              | 0                          | 0           |  |

|                    | 命令                                      | シーケンス演算     |              | 17                         |             |  |

|                    |                                         | 数値演算, その他   |              | 120                        | 56          |  |

|                    |                                         |             | バイト          |                            |             |  |

|                    |                                         | -: A.T      | ワード          | 0                          | 0           |  |

|                    |                                         | データ刑        | ド式ロングワート     |                            | 0           |  |

|                    |                                         |             | フローティング      |                            |             |  |

|                    |                                         | レジスタ修飾      |              | 0                          | 0           |  |

|                    | 命令実行 問                                  | シーケンス演算     |              | 1 μs                       |             |  |

|                    |                                         | 加減算         |              | 1 μs                       | 1.6μs       |  |

|                    |                                         | 乗算          |              | 3.6µs                      | 10.6μs      |  |

|                    | 割込                                      |             |              | 4レベル                       | 4レベル        |  |

| 主記憶                | プログラムメモリ                                |             | メモリ素子        | ICRAM(バッテリーバックアップ付き)       | IC RAM      |  |

|                    |                                         |             | 容量           | 32/64 k ワード                | 最大IMワード     |  |

| 土 記 思              | データメモ                                   | П           | メモリ素子        | ICRAM(バッテリーバックアップ付き)       | (プログラム・データ) |  |

|                    | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 9           | 容量           | 6 · 32kワード                 | 共 用 /       |  |

|                    | タイマ                                     |             | 点数           | 最大768点                     |             |  |

| シーケンス<br>タイマ, カウンタ |                                         |             | 設定時間         | 0.1~3,276.7s<br>1 ~32,767s |             |  |

|                    | カウンタ                                    |             | 点 数          | 最大64点                      |             |  |

|                    |                                         |             | 設定値          | 1~32,767点                  |             |  |

|                    | バルス                                     |             | 点 数          | 最大64点                      |             |  |

|                    |                                         |             | 設定時間         | 0.1~3,276.7s               |             |  |

| PI/O               | PI/Oユニット シマ                             |             | シングル<br>システム | 最大 7 ユニット<br>16スロット・ユニット   |             |  |

|                    |                                         |             | マルチシステム      | 最大32ユニット<br>15スロット・ユニット    |             |  |

|                    | アドレス範囲                                  |             |              | 最大 4 kワード(64kビット)          |             |  |

表 2 HISEC 04-M/D, DG伝送装置のレパートリ 豊富な伝送装置レパートリにより、システム構成能力を向上している。

| 名 称        | 用 途                                            |            | 主要諸元                      |

|------------|------------------------------------------------|------------|---------------------------|

|            | • 上位計算機とのデータ伝送                                 | 伝送速度       | I Mbps                    |

| μΣ NETWORK | <ul><li>PC間のデータ伝送</li><li>PCと入出力装置間の</li></ul> | 伝送距離       | I km(光)                   |

|            | データ伝送                                          | システム<br>規模 | 32ステーション/ループ<br>2 ループ/CPU |

|            | • 高速DDC用                                       | 転送速度       | 500kワード/s                 |

| バス結合装置     | プロセスデータ転送                                      | システム<br>規模 | 最大 8 台<br>(PI/O含 む。)      |

|            | • PC間データ、リンケージ                                 | 伝送速度       | I Mbps                    |

| 光STU       | • リモート入出力用                                     | 伝送容量       | 16ワード/チャネル                |

|            |                                                | 伝送距離       | 最大Ikm                     |

注:略語説明 STU(Signal Transmission Unit) PC(プログラマブルコントローラ)

る。データの転送方式は、転送手順プログラムの不要なハードウェア方式を採用し、各CPUの動作とは独立して高速転送を実現している。したがって、各CPUは独立に動作が可能であり、CPU単位の分割調整が可能である。

#### 5.3 μΣNETWORK

$\mu\Sigma$ NETWORKは、H-04-M/DG、HIDIC-V90シリーズ計算機、ディスプレイ、タイプライタなどの各種入出力装置の間のデータ伝送を行なうネットワークシステムである。  $\mu\Sigma$ NETWORKの伝送路は二重化されており、伝送路断線、ステーション障害時には、ループバック機能により障害部位を切り離し運転を続行するので、高信頼なシステムが構築できる。

# 6 PADT(プログラミング・デバッグ装置)

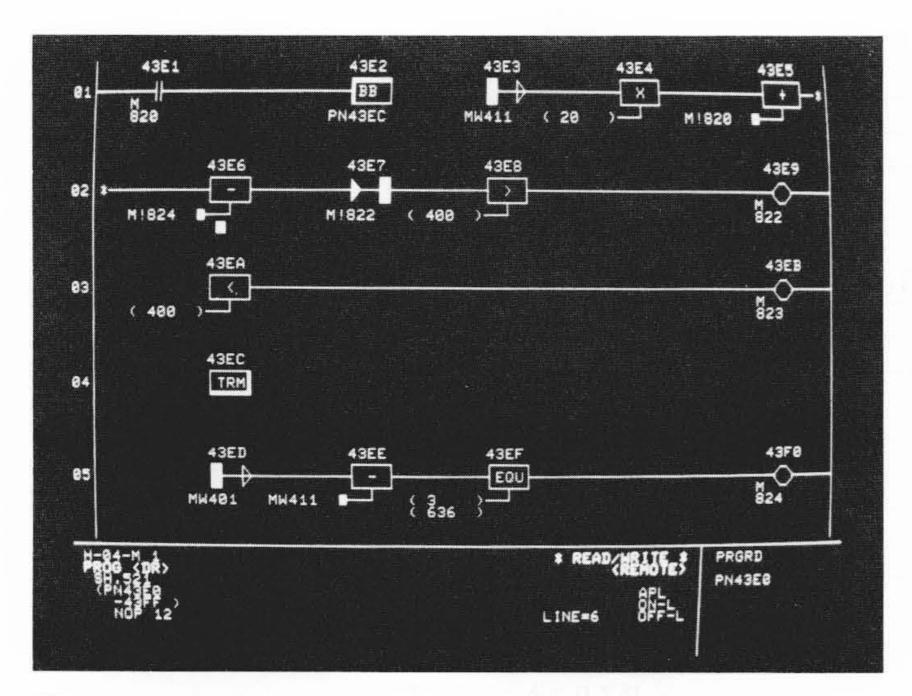

PADTはプログラムの作成、編集、デバッグなどを行なうマンマシンツールである。命令語を表現する方法として図4に例示するようなシンボル表示方式を採用し、プログラムを視覚的に理解しやすいように配慮している。プログラムは電気技術者が用いるシーケンスダイヤグラムに沿った形で直接作成し、これが直ちにCRT画面上に表示される。シーケンスダイヤグラムに付けられているシート番号をもとにして、プログラムを管理するシート番号管理機能を設けており、シー

図4 PADTのプログラム表示例 シンボル表示方式を採用し、プログラムを直観的に判読できるようにしている。

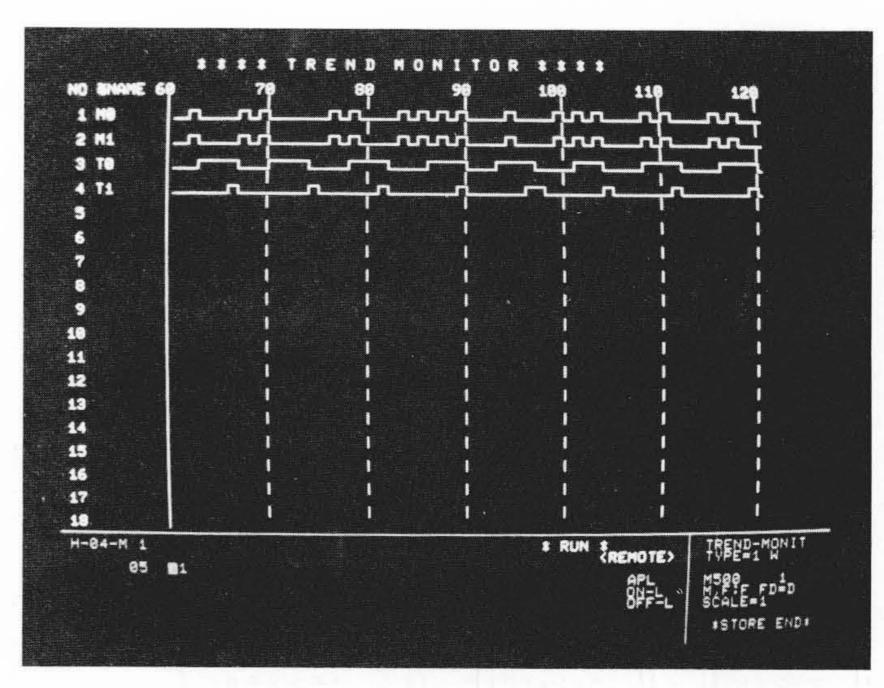

図 5 トレンドモニタの例 デバイスの動作経過を記録しタイムチャートで表示している。デバイス相互間の動作を分かりやすくしている。

ト番号をキーにしてプログラムの読出し、書込みが行なえる。 プログラムの作成や修正作業の効率向上を支援する機能として、クロスリファレンスリスト出力、マップ出力、コメントなども具備している。

プログラムデバッグ時に有効な機能として,シングルステップ実行やプログラムの任意ブロック実行機能,文法チェック機能などを備え,デバッグの効率化を図っている。

オンラインモニタ機能としては、シーケンスモニタ、ホールドモニタ、I/Oモニタ、トレースバック、トレンドモニタなどがある。シーケンスモニタは、モニタ結果を図4に示すようなシンボル表示画面上に表示する。ビット演算処理に対してはオン・オフの区別を色を変えて表示し、数値演算処理に対しては演算結果の値を演算命令の近傍に表示することによってプログラムの動作状態が一目ではっきり理解できるようにしている。これらオンラインモニタ機能の充実により、プログラムのテスト、デバッグ、メンテナンスの効率が向上することはもとより、ますます大規模、複雑化する制御システムの保守性を大幅に向上している。

図5にトレースバック(又はトレンドモニタ)時に収集した ビット情報をタイムチャート形式で表示した例を示す。

#### 7 結 言

ハードウェア及びソフトウェア両面のインタフェースミニマムを基本コンセプトとする高速・高機能PC H-04-M/DGについて述べた。

これにより、コストパフォーマンスの高い設備の実現を可能とした。今後とも更に日進月歩のエレクトロニクス技術を追求するとともに、ユーザーのニーズを反映しながら使いやすいプログラマブルコントローラ、DDCシステムの発展に寄与してゆきたいと考える。

# 参考文献

- 1) 下山,外:PCの高速制御システムへの応用,電気学会雑誌, 102,4,289~292(昭57-4)

- 2) 桜井,外:最近の鉄鋼圧延制御システム,日立評論,**61**,9,641~644(昭54-9)

- 3) 浅川,外:圧延機制御システムの新展開,日立評論,**67**,4,325~330(昭60-4)