# CMOS $1.0 \mu \text{mゲートアレー} 「HG62Eシリーズ」$

CMOS 1.0 m Gate Array "HG62E Series"

CMOSゲートアレーは電子機器の高機能化・小形化・低価格化の強い要求,及びLSI技術とCAD技術の進歩に支えられて,高速化・高集積化が進んでいる。このような背景からCMOS1.0μmプロセスを用いた「HG62Eシリーズ」を開発した。ゲート数は4,300ゲートから2万4,000ゲートまでの7マスタチップ,ゲート1段当たりの遅延時間は0.7nsという高速動作を実現した。適用パッケージについても多ピン対応として新たにQFP136,168・PGA240を追加し,実装密度の向上を図った。また,設計サポートについても論理インタフェース,自動レイアウト,自動診断の三つのサブシステムによって構成されるゲートアレーDAシステムの改良を行い,ユーザーフレンドリー性の向上を行った。

戸井田徳次\*Tokuji Toida甲把健\*Takeshi Gappa道下智\*Satoshi Michishita関光穂\*\*Mitsuho Seki

# 1 緒 言

近年、電子機器の小形化及び多機能・高性能化、そして低価格化を図るうえで、システム専用のLSIの導入は不可欠になりつつある。システム専用のLSIにはゲートアレー、スタンダードセル、PLD(Programmable Logic Device)などがあり、こうしたセミカスタムLSIをASIC(Application Specific IC)と言い、これまでシステム専用のカスタムLSIに手の届かなかったユーザーが気軽にカスタムLSIを手に入れられるようになった。これはLSI技術とCAD技術の発展により、短い開発期間で多品種の開発が可能となったことによる。

ゲートアレーは数百から数万の未配線のままのトランジスタを配列したチップをあらかじめ大量に作っておき,個々のユーザー論理回路をCAD技術で配線を行うセミカスタムLSIで,高駆動タイプのバイポーラ形と低消費電力タイプのCMOS (Complementary Metal Oxide Semiconductor)形の二つがある。CMOSゲートアレーは最近のプロセス技術の進歩で高速化・高集積化が著しく、主流となりつつある。

ユーザーの要求する製品ニーズは高速性と高集積性などデバイス性能や豊富なパッケージのほか設計サポートの充実である。設計サポートではユーザーがゲートアレーでカスタムLSI化する場合、いかに短い期間で効率良く、品質が高い製品設計を実現できるかが重要なポイントになる。

このため日立製作所では、設計サポートとして論理インタフェース(論理検証を含む。)、自動レイアウト、自動診断の三つのサブシステムから構成されるゲートアレーDA(Design Automation)システムを開発しているが、そのいっそうの改良を行った。特に、日立製作所では従来から自動診断のサポート<sup>1)</sup>を行ってきたが、更に、大規模化に伴い重要性が急激に高まっており、自動診断方式の改良を行いユーザーゲート使用率の向上を図った。

以上の背景から、新しいデバイスとしてCMOS1.0µmプロセスを用いてゲート遅延時間0.7nsの高速かつ4,300ゲートから2万4,000ゲートまでの大規模高集積のCMOSゲートアレーを開発した。本稿ではこのCMOSゲートアレー「HG62Eシリーズ」の製品概要とその設計サポートシステムであるゲートアレーDAシステムについて述べる。

# 2 製品概要

## 2.1 マスタチップ

HG62Eシリーズの主要諸元を表1に示す。本シリーズのゲート数はすべて2入力NAND換算とし、ユーザー使用可能ゲート数は自動診断ありで70%、自動診断なしで90%となるように設定されている。本シリーズのマスタチップは、4,300ゲートから2万4,000ゲートの七種類で構成されている。これにより、ユーザーは自己のシステム規模に合わせて最適なゲート数のマスタチップを選択することが可能となっている。更に、最大ゲート数が2万4,000ゲートまであることによって、大規模なシステムを1チップ化でき、高性能化を図ることが可能となっている。また、従来から日立製作所のゲートアレーの特徴である多機能I/O(入出力)及び高駆動出力は継続するとともに入出力の高速化も実現している。

# 2.2 主要特性

HG62Eシリーズは従来シリーズと同じ絶対最大定格を保ちながら、高速・高集積化を図るために、最先端のAl2層配線技術とCMOS1.0 $\mu$ mプロセスを採用した。このことで十分に余裕を持ったシステムのタイミング設計を可能にした。ゲート遅延時間はファンアウト2でAlの配線長が2mmの負荷条件で2NANDの内部ゲートは0.7ns、ファンアウト2でAlの配線長が2mmの負荷条件で入力バッファは2.0ns、また、出力

<sup>\*</sup> 日立製作所武蔵工場 \*\* 日立製作所日立研究所

バッファは50pFの負荷容量で7.0nsと高速性を実現した。

# 2.3 パッケージ

パッケージは**表 1** に示すようにDIP(Dual In Line Package), QFP(Quad Flat Package), PLCC(Plastic Leaded Chip Carrier), PGA(Pin Grid Array)の4種類のパッケージをラインアップ化している。この4種類のパッケージのピン数は7種類のマスタチップのI/Oバッフア数,適用電子機器 実装方法やI/O数に対して適切なピン数を選択できるように準備した。特に,電子機器の小形化に対応するため,実装密度の高い面付け多ピンパッケージQFP136,168及び超多ピンPGA240をラインアップ化した。また,ユーザーの実装方法の多様化に伴いPLCCもラインアップ化した。

# 2.4 チップ構成

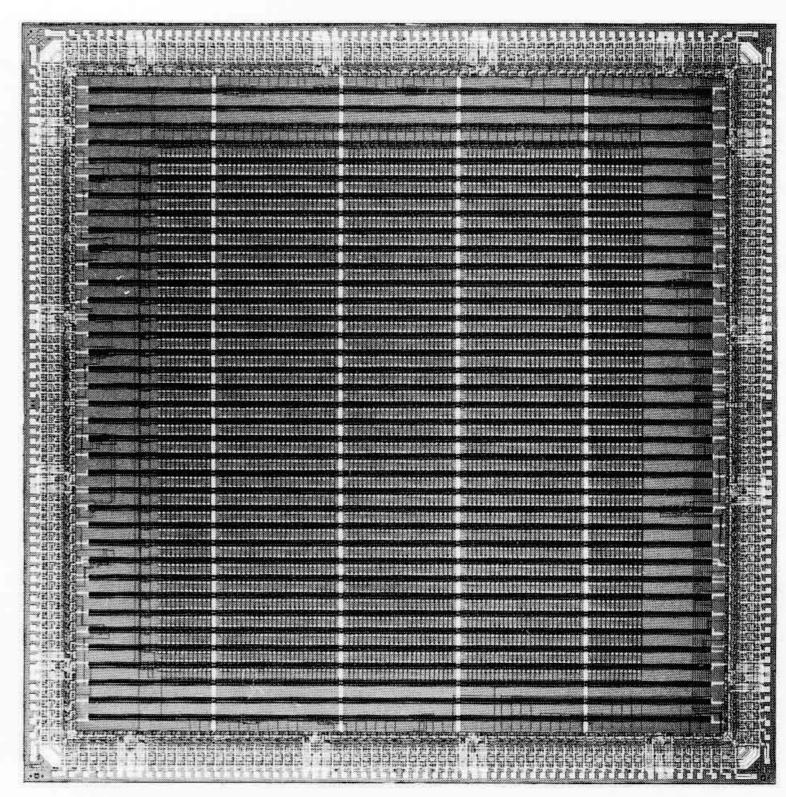

マスタチップのレイアウトは、7種類のマスタチップについて同様のレイアウトになっている。図1に例として、2万4,000ゲートのHG62E240のチップ写真を示す。チップの4辺には外部と内部のインタフェースとしてI/Oバッファを配置し、I/Oバッファの内側に論理回路を組むベーシックセルが横一列に並び、その論理ブロックを結ぶための配線チャネル列を交互に配置した。また、ベーシックセル100個から150個ごとに電源を補強する補助電源ラインを配置した。

I/Oバッファはボンディングパット側から出力部,入力部, プリバッファ部を配置した。今回プリバッファを設けること によって,従来内部ゲートで組んでいた回路が不要になると ともに,安定な出力特性が得られるようになった。また,I/O

図 I HG62E240チップ写真 チップサイズ12.52mm×12.52mmの中に2万4,000ゲートのベーシックセルと272端子が実装されている。

バッファ内にいろいろなサイズのトランジスタを配置しその 組合せにより、下記機能を実現した。

- (1) CMOS/TTL(Transistor Transistor Logic)レベル入力

- (2) CMOS/TTLレベルシュミット回路

- (3) プルアップ・プルダウン回路

表 I HG62Eシリーズの主要諸元 内部ゲート遅延時間0.7ns,最大ゲート数2万4,000ゲートと高速・高集積のCMOSゲートアレーである。

| 項目            | HG62Eシリー | ・ズ                      | HG62E43                     | HG62E58              | HG62E75 | HG62E101    | HG62E130 | HG62E182 | HG62E240              |  |

|---------------|----------|-------------------------|-----------------------------|----------------------|---------|-------------|----------|----------|-----------------------|--|

| ゲー            | ŀ        | 数                       | 4,309                       | 5,821                | 7,488   | 10,076      | 13,015   | 18,176   | 24,020                |  |

| 使用可能          | 入出力共通    |                         | 88                          | 106                  | 122     | 146         | 166      | 206      | 232                   |  |

| バッファ数         | 出力専用     |                         | 8                           | 8                    | 8       | 8           | 8        | 8        | 8                     |  |

| ゲート           | 内部ゲート    |                         | 0.7ns/2NAND, F.O=2, AI配線2mm |                      |         |             |          |          |                       |  |

| 遅延時間          | 入力バッフ    | 入力バッファ                  |                             | 2.0ns/F.O=2, AI配線2mm |         |             |          |          |                       |  |

| (Typ.) 出力バッファ |          | $7.0$ ns/ $C_L = 50$ pF |                             |                      |         |             |          |          |                       |  |

| 消費            | 電        | カ                       | 200μW/ゲート, 10MHz            |                      |         |             |          |          |                       |  |

| 入 出 力         | レベ       | ル                       | TTL/CMOS選択可能                |                      |         |             |          |          |                       |  |

| 特 殊           | 機        | 能                       | 水晶                          | 発振回路                 | シュミット回路 | プルアッ        | プ・プルダウン回 | 路 自動診    | 自動診断機能                |  |

| パッケージ         | DP 40    |                         | 0                           | 0                    | 0       |             | _        |          | -                     |  |

|               | 645      | 3                       | 0                           |                      |         |             | 0        |          | _                     |  |

|               | QFP 64   |                         | 0                           | 0                    |         | _           |          |          | ( <u>**** * * *</u> ) |  |

|               | 80       |                         | 0                           | 0                    |         | 0           | _        |          | :                     |  |

|               | 100      |                         | 0                           | 0                    | 0       |             | _        |          | -                     |  |

|               | 136      |                         | -                           | 0                    | 0       | 0           | 0        |          | -                     |  |

|               | 168      |                         | -                           | =                    |         | $\triangle$ | Δ        | -        | -                     |  |

|               | PLCC 68  |                         | 0                           | 0                    | 0       | 0           | 0        |          |                       |  |

|               | 84       |                         | Δ                           | Δ                    | Δ       | Δ           | Δ        |          |                       |  |

|               | PGA 135  |                         | =                           | -                    | 0       | 0           | _        | —        | -                     |  |

|               | 179      |                         | 2 <del></del> 2             | _                    | 0       | 0           | Δ        | <u> </u> | 155                   |  |

|               | 240      |                         |                             | _                    | =       | _           | _        | 0        | 0                     |  |

注:略号説明など TTL/CMOS(Transistor Transistor Logic/Complementary Metal Oxide Semiconductor)

DP(Dual In Line Plastic Package)

QFP(Quad Flat Package)

PLCC(Plastic Leaded Chip Carrier)

PGA(Pin Grid Array)

## (4) 水晶発振信回路

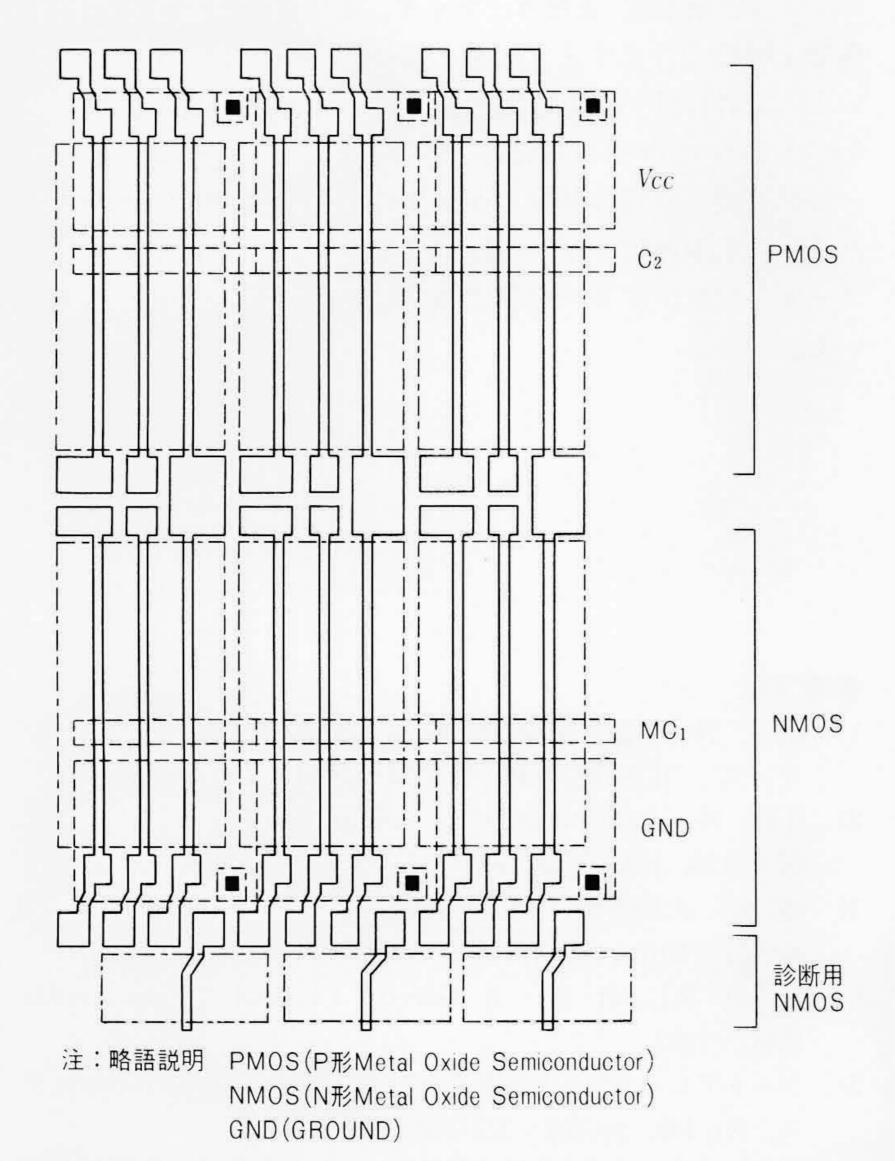

図2に示すように、ベーシックセルは設計サポートの一つであるテストパターンの自動生成を可能とする自動診断機能を効率よく行うため、3組みのPチャネルトランジスタ、Nチャネルトランジスタ、及び自動診断用のNチャネルトランジスタで構成した。また、ベーシックセルの配線領域は電源ライン及び自動診断用の二つの専用クロックライン、並びに論理ブロックを構成する配線から成っている。

# 2 設計サポート(ゲートアレーDAシステム)

# 3.1 論理インタフェース

# 3.1.1 標準論理インタフェースフォーマットの新設

ユーザーとメーカー間で設計データの受渡しを行う場合、多様化するユーザーの設計データ構造に対応するため、メーカー側では記述能力が高く、かつ多数のユーザーが理解しやすい標準化された設計データフォーマットが必要である。これに対応するため、日立製作所では標準インタフェースフォーマットとしてCLIF(Customer Logic Interface Format)を新規に設定した。CLIFの大きな特徴は階層表現が可能なことである。これにより、大規模LSIの設計データが効率よく表現できる。その他にバス記述、入出力共通バッファの直接的な表現、信号文字数の制約の大幅な緩和などを実現しており、これからのASICビジネスでの標準フォーマットとなるものであり、HG62Eシリーズのインタフェースとして使用される。

図 2 ベーシックセル 3ベーシックセルを示す。 $C_2$ ,  $MC_1$ は診断専用のクロックである。

#### 3.1.2 EWSインタフェース

1983年ごろから普及の始まった市販EWS (Engineering Work Station)は高価ではあるが、ユーザーがそれを購入することによって、ユーザー側で論理設計から論理検証を完結することができ、設計期間も大幅に短縮できることから、ゲートアレー分野での設計サポートツールとして地位を築きつつある。高級EWSメーカーとしてはMENTOR社、DAISY社、VALID社のものが世界的規模で普及している。また、EWSの廉価版としてはFUTURE NET社のDASHが普及している。

日立製作所としても、これらのEWSで論理設計するユーザーに対して、論理セルライブラリ及び設計されたデータを日立標準フォーマットCLIFに自動変換するツールを開発してサポートしている。一般的にEWSの設計サポートに当たって、EWS自身の持っている基本機能に加えて、LSIに合わせた設計ルールチェックなどのユーザーの使いやすさを考慮したサポート機能を付加していく必要がある。日立製作所では、各EWSに対してこのようなプログラムを準備している。これにより、ユーザーでの設計が容易になるとともに品質も向上し、ひいては設計期間の短縮につながる。なお、市販EWSのほかに市販シミュレータとして普及しているGENRAD社のHILO及びGE・CALMA社のTEGASシミュレータとの変換ソフト及びライブラリは完備しており、現在、普及している市販設計サポートツールとのインタフェースはほぼ網羅している。

#### 3.1.3 TTLインタフェース

3.1.2で述べたEWSインタフェースは普及しつつあるが、国内で見れば依然として図面インタフェース(ユーザーとメーカー間で論理図とテストデータをインタフェースにするケース)が占める割合が高い。図面インタフェースの場合、ユーザーが作成する論理図はTTLをベースに作成されることが多い。今後ゲートアレーが大規模化するにつれて、ますます論理設計時の部品単位も大きくなり、ユーザーがTTLマクロを使用して設計できる環境を提供することは重要である。日立製作所では既にTTL-GA(Gate Array)自動変換プログラムを開発し、試行していたが、今回、HG62Eシリーズに適用すべくTTLマクロセルライブラリの準備を進めている。

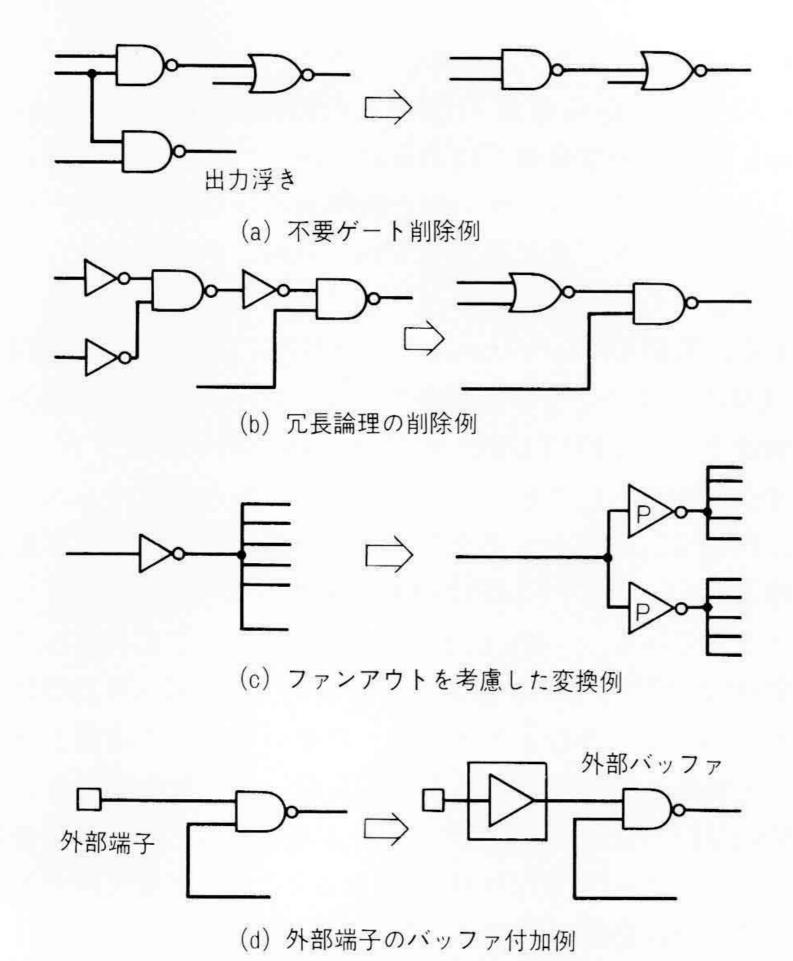

TTL-GA自動変換プログラムは不要ゲートの削除、ファンアウトを考慮した論理変換、ある規則に基づいてTTLレベルの入出力をCMOSレベルの入出力に変換する機能などを持っている。今後、TTL-GA自動変換プログラムを本格的に適用することによって、ユーザー及びメーカーの双方で大幅な設計工数低減を図れると見込んでいる(図3参照)。

# 3.2 自動レイアウト

## 3.2.1 一括レイアウト

20kゲートクラスの大規模ゲートアレーを、TAT (Turn Around Time)を損なうことなく処理するために、31ビットOS (Operating System)を使用して一括レイアウトする自動レイアウトシステムを開発した。一般的に規模が増大すると処理するデータ量が増大するため、メモリの制限から従来は分割レイアウトによる設計手法がとられていたが、チップ分割などの人手を要しTAT増大の要因になっていた。本開発では、31ビットOSを使用した一括レイアウト方法を開発することで

図3 TTL-GA自動変換例 変換ルールライブラリに基づいて各種のTTL-GA(Transistor Transistor Logic-Gate Array)変換を行う。図中左側はTTLでの論理を、右側は変換後のGAでの論理を示す。

TATの確保を実現できた。また、一括レイアウト法により分割方式で発生しやすかった無効領域の減少も同時に実現することができた。

## 3.2.2 配置配線性能の向上

大規模なゲートアレーの未配線を発生させることなく高速に自動処理するための配置配線のアルゴリズムを開発した $^{20}$ 。配置プログラムは結線率を重視した配置階層の概念を導入した。これにより,配置で重要な役割を占める初期配置時の予想配線長と混雑度のバランスを高精度に算出できるようになり,配置改善への負担を軽減して,トータルとしての配置時間を大幅に短縮した。配線アルゴリズムとしては,高速アルゴリズムの観点から概略配線として線分探索法 $^{30}$ ,詳細配線として新アルゴリズム $^{40}$ をベースに新たなコラムスキャン法を考案し,配線処理時間の大幅な短縮を実現した。以上の処理によって,従来手法と比較して配置配線に要したCPU時間を,約 $\frac{1}{6}$ に短縮できた。

# 3.3 テスティングDA

# 3.3.1 自動診断システム

LSIが大規模化するにつれて、製造したLSIの品質を保証するテストパターン設計の工数は急速に増大している。これに対処するために、既に、HG62Bシリーズでランダムスキャン方式と呼ばれる高い故障検出率(295%)を持つテスト回路、及びパターン自動生成システムを開発し、実用化している。本システムはスキャン回路の自動生成まで含めて完全自動化しており、設計工数の大幅低減を実現している50,60。ここで採用されているランダムスキャン方式は、アドレススキャン方式の一種でフリップフロップをデコードするテスト専用信号線

が多いため、実装性能上比較的未配線が発生しやすいという性質を持っている。このため、ユーザーゲート使用率(ユーザー論理回路のゲート数/ベースチップのゲート数)は60%程度にとどまっていたが、今回の改良により70%まで向上させることができた。

# 3.3.2 ユーザー使用ゲート率の向上

HG62Eシリーズの開発に当たっては、ユーザーゲート使用率の向上を目指して、従来のランダムスキャン方式をベースに改良を加えて、デコーダ回路が不要な新シフト方式によるテストパターン自動生成システムの開発を行った。新シフト方式はシフト動作専用のシステムブロックを設けたが、ランダムスキャン方式で用いた2種類の診断専用システムクロックはそのまま使用していることから、ランダムスキャンの利点(論理制約が極めて少ないなど)はそのまま受け継がれている。実装性能評価を行った結果、ユーザーゲート使用率も大幅な改善が図られており、今後HG62Eシリーズに適用が可能なことを確認した。

# 4 結 言

以上、 $CMOS1.0\mu m$ プロセス技術を用いた高速・高集積 CMOSゲートアレーHG62Eシリーズの製品概要とその設計サポートを中心に述べた。

CMOSゲートアレーはその適用分野が大形コンピュータからLAN(Local Area Network), FAX(ファクシミリ)のような通信・端末機器,そしてワードプロセッサやタイプライタのようなOA機器,またオーディオ,ビデオ,楽器などの民生機器と幅広く,ますます高速・高集積化の要求が強くなっている。これに伴い豊富な製品系列,実装密度が高くかつ実装しやすいパッケージの整備,ユーザーが設計しやすい開発ツールの充実,支援体制などが必要になる。これらの要求にこたえるべくHG62Eシリーズを開発したが,今後更に充実させ,ユーザーフレンドリーな製品開発を行っていきたいと考えている。

# 参考文献

- 1) 道下,外:自動診断機能付きCMOSゲートアレー「HG62Bシリーズ」,日立評論,68,7,573~576(昭61-7)

- 2) 小林,外:大規模マスタスライス用配置手法,情報処理学会全 国大会33, p.2245(昭61後)

- 3) 関,外:大規模ゲートアレー用高速自動配線手法,情報処理学 会設計自動化,33,4,(1986-7-15)

- 4) Rivest R.L., et al, : A Greedy Channel Router, p.425 DAC, 1982

- 5) ゲートアレイのテスト設計を自動化する:日経エレクトロニクス, No.400, pp.301~322(1986-7-28)

- 6) 林, 外: 検査容易なLSI論理回路の自動設計方式, 情報処理学 会論文誌, 27, No.1, pp.90~95(1986-1)