# 1 Mビットフレームメモリ"HM53051"

# 1 Mbit Frame Memory "HM53051"

カラーテレビジョンやVTRのディジタル化に伴い、大容量かつ信号処理に適した高速動作が可能な画像処理専用メモリの要求が強まっている。

入出力にシリアルーパラレル変換回路を用いて、32ワード単位の内部データ転送を行い、60 ns以下の高速動作と32ワード単位のランダムアクセスを実現した1MビットフレームメモリHM53051を開発した。

HM53051の特性は、標準測定条件でアクセス時間が23 ns、消費電流が29 mAである。

大石貫時\* Kanji Ôishi 小島 昇\*\* Noboru Kojima 近藤和夫\*\* Kazuo Kondô

## 1 緒言

カラーテレビジョンやVTR(ビデオテープレコーダ)の高画質化と多機能化を実現するために、画像信号のディジタル信号処理が一般的になりつつある。ディジタル画像信号処理を目的としたメモリとして、カラーテレビジョン画像信号の1走査線又は2走査線を記憶し、走査線のノンインタレース化や走査線上のノイズを取り去り高画質化を図るノイズキャンセラなどに使用するラインメモリが、既に開発されている。更に、高画質化と多機能化を実現するためには、カラーテレビジョン信号の1画面を記憶し、フレーム相関を利用した高画質Y(輝度信号)・C(色信号)分離<sup>1)</sup>や静止画表示、マルチ画面表示に使用するフレームメモリが必要である。

アレビジョン信号1フィールドを記憶するためには、約1.9 Mビットの容量が必要であり、サイクル時間69 nsと高速で入出力同時動作を行う必要がある。はん(汎)用DRAM(Dynamic Random Access Memory)を用いてフレームメモリを構成すると、インタリーブによるスピード変換やアドレス発生回路などの周辺回路が必要であり、システムコストが上昇する。このため、ディジタルテレビジョン、ディジタルVTRの高画質化と多機能化を容易に実現できる専用のフレームメモリへの要求が強かった。この要求にこたえるため、1 Mビットフレームメモリ HM53051(以下、HM53051と略す。)の開発を行った。

以下, HM53051の設計, 電気的特性及び応用について述べる。

#### 2 目標仕様

表1に目標仕様を示す。NTSC (National Television System Committee) 方式のテレビジョンは525本の走査線によって構成されており、1走査線ごとに飛び越し走査 (インターレース)を行い、 $\frac{1}{60}$ 秒ごとに走査線262.5本の偶数フィールドと奇数フィールドを交互に走査する。サンプリング周波数を色信号副搬送波周波数 (fsc=3.58 MHz)の 4 倍の周波数

表 I HM53051の目標仕様 NTSC方式で、サンプリング周波数4fsc、量子化ビット数 8 ビットのシステムで、高画質化、高機能化を容易に実現できる仕様とした。

| 項目        | <b>仕</b> 様                      |

|-----------|---------------------------------|

| メ モ リ 構 成 | 262,144ワード× 4 ビット               |

| ポート構成     | シリアル入出力2ポート構成                   |

| サイクル時間    | 60 ns                           |

| アクセス時間    | 40 ns                           |

| 消費電流      | 40 mA typ                       |

| 電源電圧      | 5 V ± 10%                       |

| アドレス発生    | 内蔵                              |

| リフレッシュ    | 内蔵(外部制御不要)                      |

| ランダムアクセス  | 可(32ワード×4ビット単位)                 |

| 入出カクロック   | セミ同期                            |

| パッケージ     | 7.62 mm (300 mil) 18ピンプラスチックDIP |

注:略語説明 DIP(Dual Inline Package)

4fscとし、8ビットの量子化ビット数でディジタル信号化する場合、1走査線当たり910ドット×8ビット、1フィールド当たり約1.9 Mビットのメモリ容量が必要となる。このため、1 HM53051を2 個で1フィールドの画像情報を記憶できるように、メモリ構成を256 kワード×4ビットとした。また、サンプリング周波数 4fscを満たすためのサイクル時間は100 ms以下が必要であり、100 msで入出力同時動作できることを目標とした。

外付け周辺回路を減らし、システム設計を容易にするため、 アドレス発生回路を内蔵し、外部からのアドレス入力を必要 としないでシリアルアクセスを可能とした。また、内部で自 動的にリフレッシュを行い、外部からのリフレッシュ制御を

<sup>\*</sup> 日立製作所武蔵工場 \*\* 日立製作所家電研究所

#### 不要とした2)。

ディジタルテレビジョンの高機能化としてのピクチャイン ピクチャやマルチ画面表示に対応可能なように, ランダムア クセス機能, 時間軸圧縮・伸長機能を持つこととした。

## 3 論理・回路設計技術

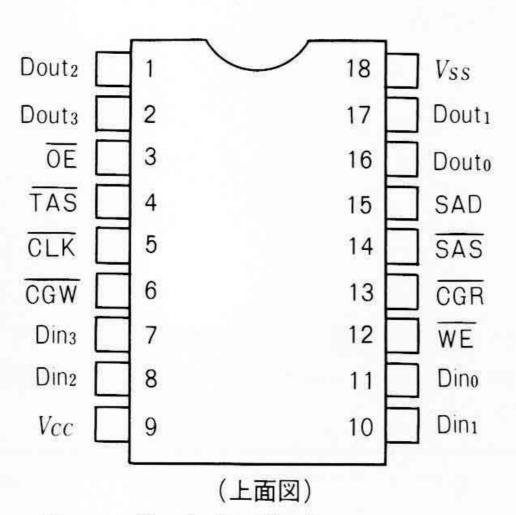

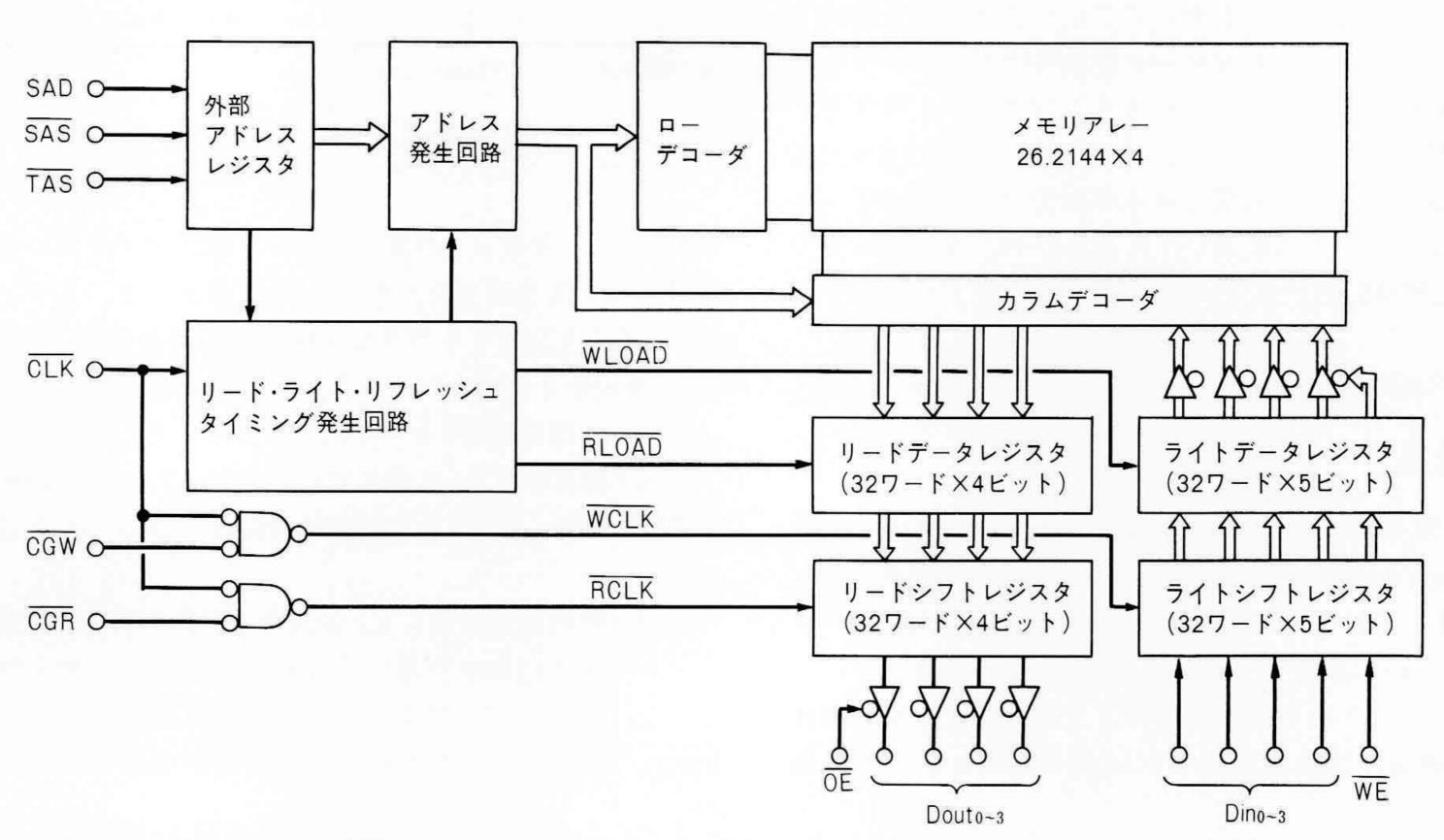

図1にHM53051のピン配置を、図2にブロック図を示す。 HM53051は、メモリセルにダイナミックメモリセルを用いており、メモリセルをアクセスするための速度変換が必要とな

$Din_{0}\sim_{3}$ :  $\vec{r}-\beta A \sim J'' \sim h$   $Dout_{0}\sim_{3}$ :  $\vec{r}-\beta P \sim h \sim h$  $\overline{OE}$ :  $P \sim h \sim h \sim h$

TAS:トランスファアドレスストローブ

CLK: システムクロック

CGW: クロックゲート(ライト)

CGW: クロックゲート(リード)

SAS: シリアルアドレスストローブ

WE: ライトイネーブル SAD: シリアルアドレス

図 I HM53051のピン配置 ランダムアクセス時の外部アドレスをシリアルアドレスSADにより行うことによって、ピン数の低減を図った。

る。このため、入出力部でシリアルーパラレル変換を行い、 内部では32ワード単位でデータ転送を行うこととし、メモリ へのアクセスはシステムクロックCLK8サイクルを割り当てる こととした。これにより、シリアルーパラレル変換1サイク ル(最小で32 CLKサイクル)中に、リード、ライト及びリフレ ッシュを時分割で行えるようにした。

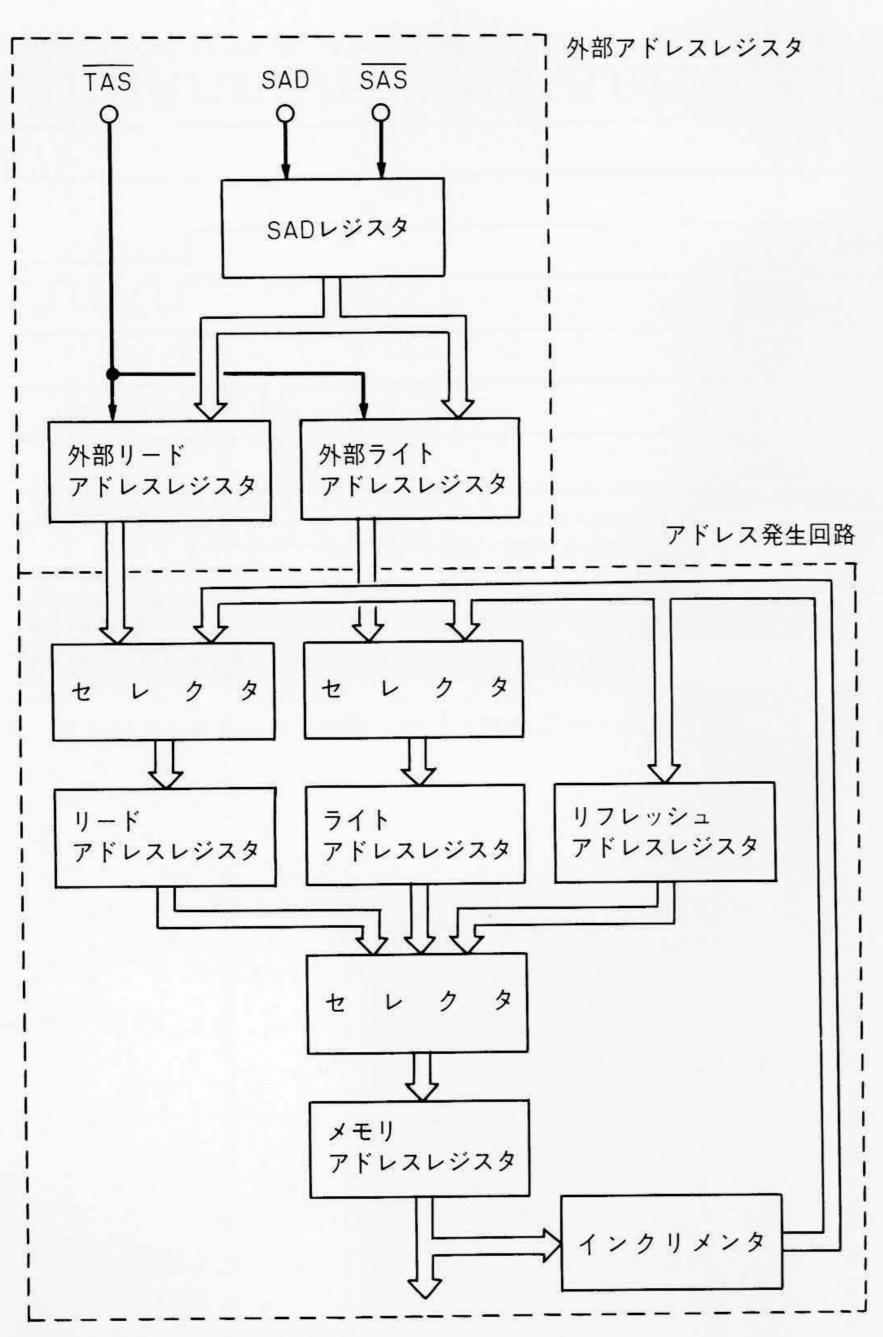

図3にアドレス系回路ブロック図を示す。ランダムアクセス時の外部アドレスは、ピン数低減のためシリアル入力とした。SADから入力されたリードアドレス(AR12-AR0)及びライトアドレス(AW12-AW0)は、SASに同期してSADレジスタに取り込まれる。TASをローにすることにより外部リードアドレスレジスタ、外部ライトアドレスレジスタに転送された外部アドレスは、メモリの動作に応じてアドレス発生回路に転送され、ランダムアクセスが行われる。ランダムアクセスは、内部のデータ転送と同じ32ワード単位で行う。ランダムアクセス後は、SADにより設定したアドレスを自動的にインクリメントする。

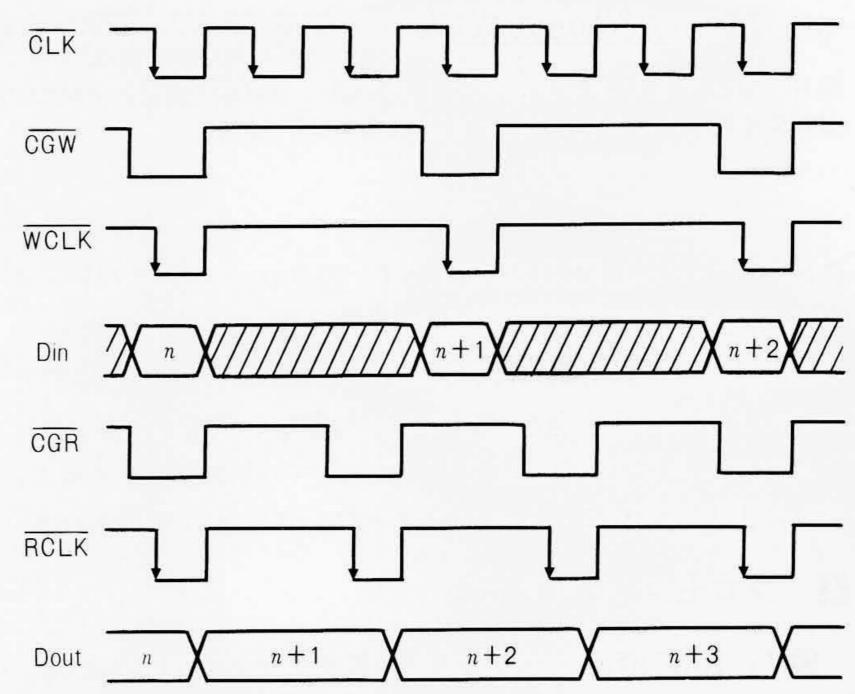

時間軸圧縮・伸長のため,入出力は $\mathbf{24}$ に示すようにゲート信号 $\overline{\mathbf{CGW}}$ , $\overline{\mathbf{CGR}}$ により $\overline{\mathbf{CLK}}$ をゲートするセミ同期方式を採用した。 $\overline{\mathbf{CLK}}$ を独立にゲートし,入出力クロック $\overline{\mathbf{WCLK}}$ , $\overline{\mathbf{RCLK}}$ を発生することによって, $\overline{\mathbf{CLK}}$ に同期した任意の異なるサイクルで,リード・ライトを可能とした。

だいじジョンの高画質化のための $Y \cdot C$ 分離には、単純遅延機能によるフレーム遅延が必要となる。このためには、ライト・リードアドレスを同時に"0"に初期設定するシステムリセット機能と、入出力タイミングを合わせる機能が必要となる。システムリセットは、SADによってリードアドレス、ライトアドレスを"0"に設定する方法のほかに、 $\overline{SAS}$ と $\overline{TAS}$ を共にローにするだけで行えるようにした。次に、入出力タイミングを合わせるために採用した回路について説明する。

図 2 HM53051ブロック図 入出力部でシリアルーパラレル変換を行うことによって、メモリをアクセスする時の速度変換を可能とした。

アドレス回路は,外部アドレスレ 図3 アドレス回路ブロック図 ジスタとアドレス発生回路で構成される。

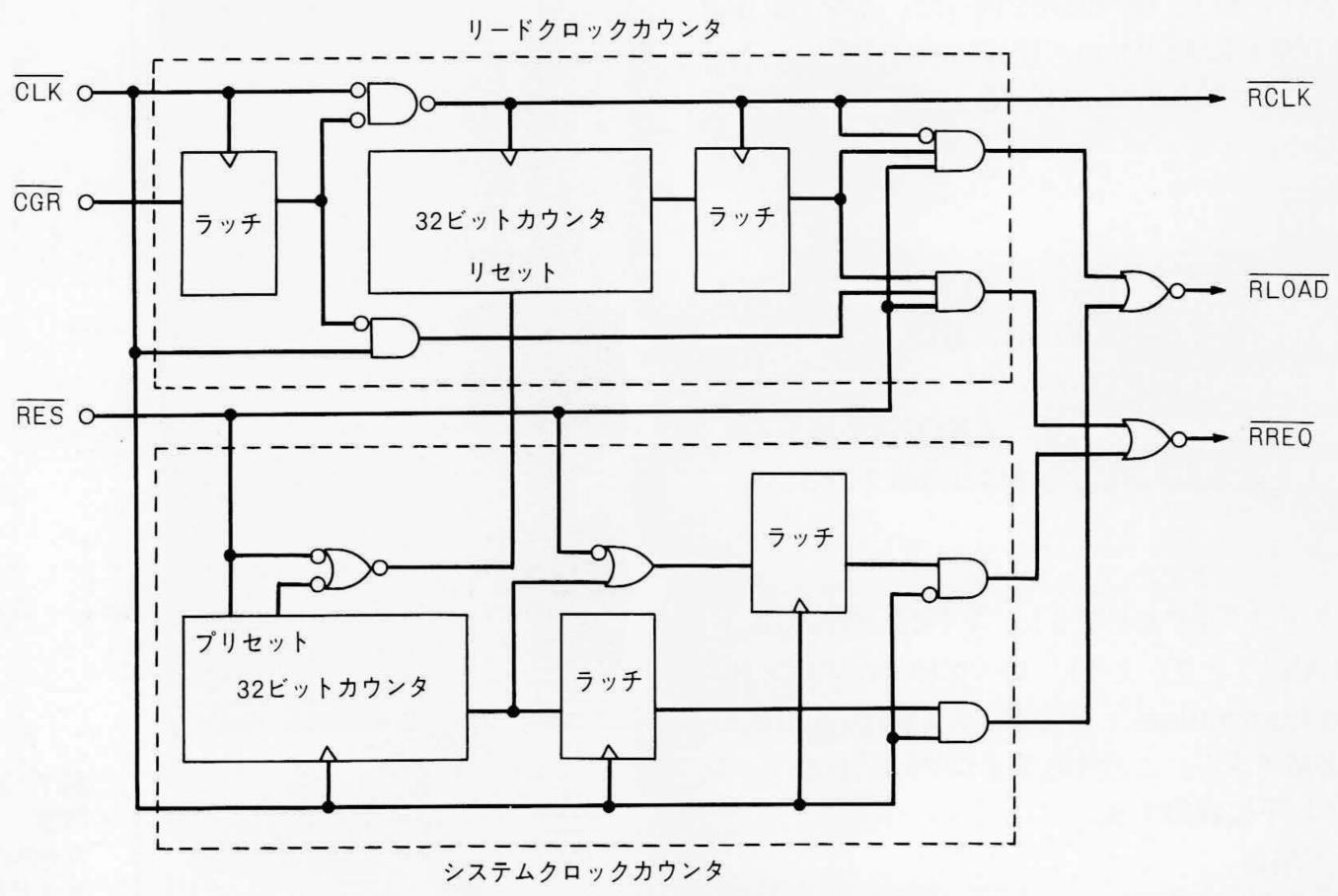

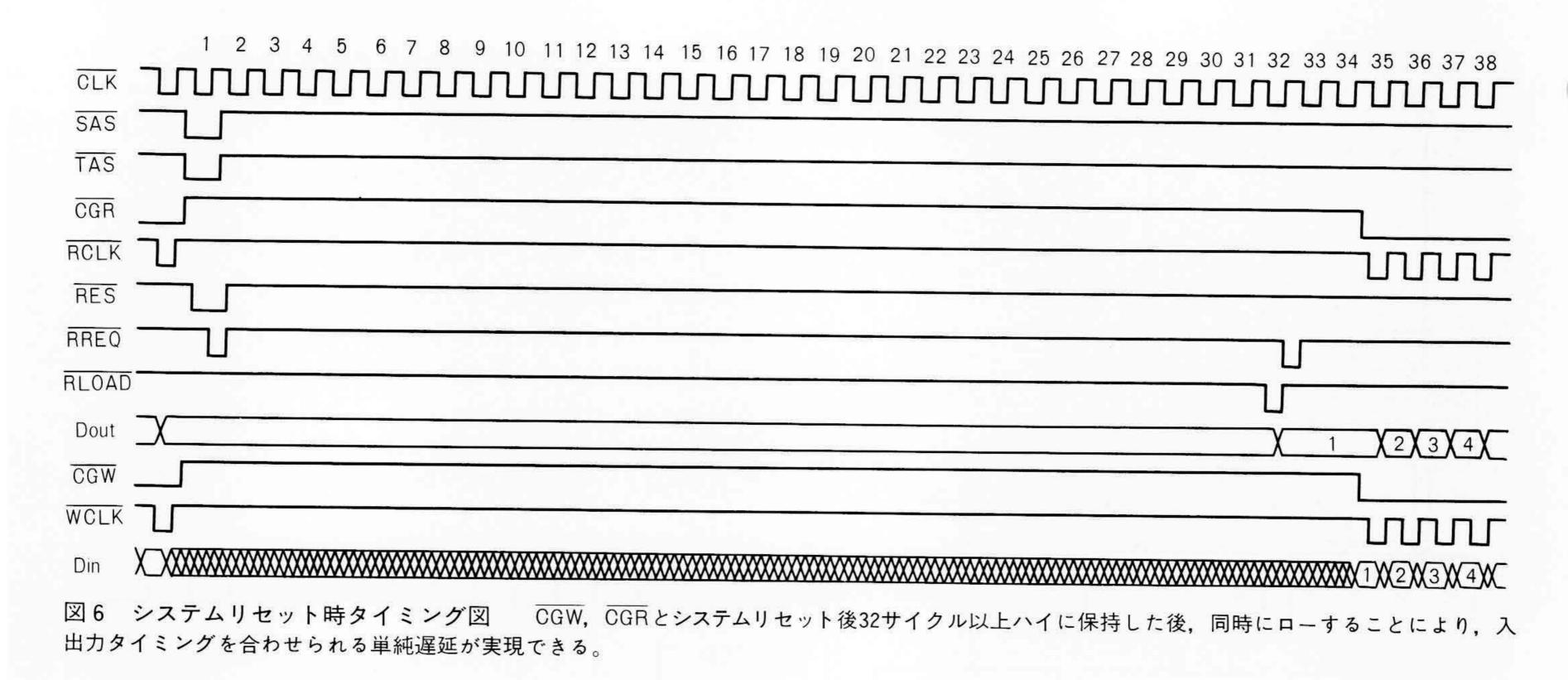

図5にデータ出力を制御するカウンタ部を、図6にシステム リセット時のタイミング図を示す。通常はリードクロックカ ウンタによりRCLKをカウントし、リードシフトレジスタの状 態をモニタする。リードシフトレジスタから32ワードのデー 夕がすべて出力されると、リードデータレジスタからリード シフトレジスタへのデータ転送信号RLOADとメモリへのリー ド要求信号RREQが出力される。SAS, TASがローになり、 システムリセットモードになると、リセット信号RESが出力 され,システムクロックカウンタが動作を開始するとともに, リードクロックカウンタはリセットされ,動作を停止する。 これにより、システムリセット後はCGRに無関係にCLKをカ

WCLKは、CGWがローのときのCLKに 入出力セミ同期方式 同期して出力する。RCLKは、CGRがローのときのCLKに同期して出力する。

出力制御用カウンタは、通常のリード動作を制御するリードクロックカウンタ 図 5 出力制御用カウンタ回路 と、システムリセット時に入出力タイミングを合わせるためのシステムクロックカウンタで構成される。

ウントし、RREQ、RLOADを出力し、32クロック目でアドレス "0"の32ワードの先頭のデータを出力する。システムリセット後32クロック以上CGW、CGRをハイにしておくと、入出力データのタイミングを合わせられる単純遅延が可能となる。システムクロックカウンタによる32クロックの動作を終了すると、データ出力は再びリードクロックカウンタによって行われる。

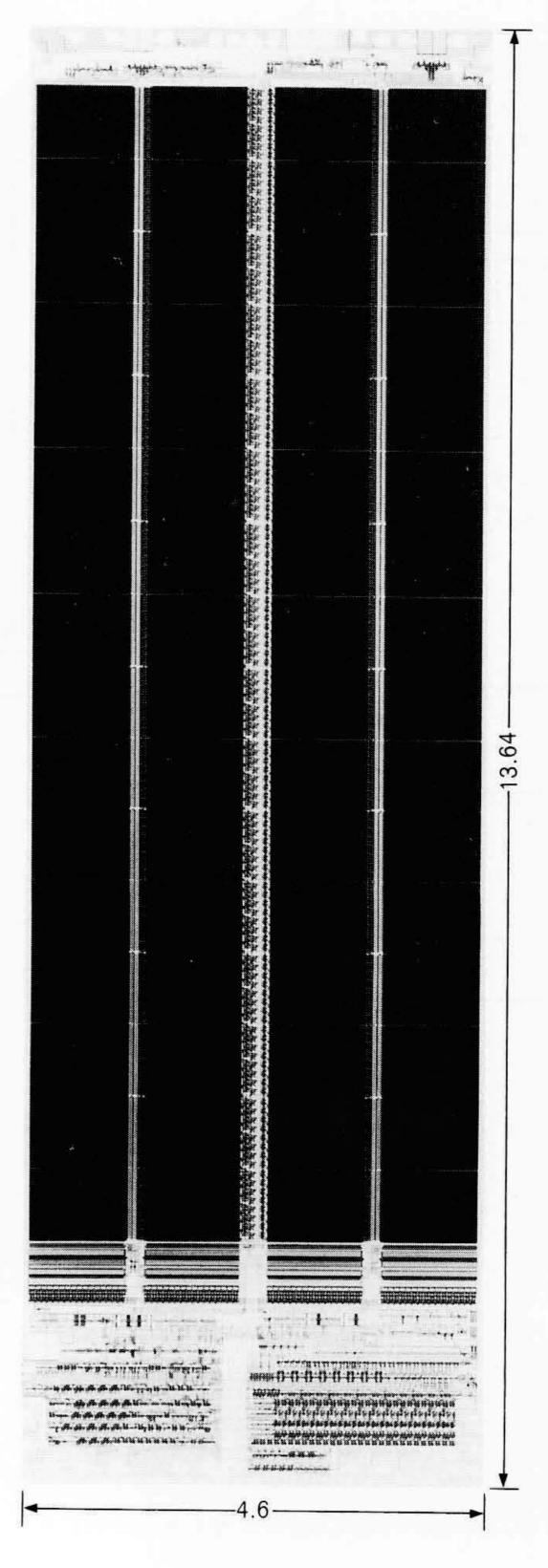

# 4 プロセス レイアウト

図7にHM53051のチップ写真を示す。1 M DRAMと同じ  $1.3 \mu m$  CMOSプロセスの採用によってメモリセルサイズ $3.4 \mu m \times 10.2 \mu m$ を実現した。メモリマットを 4 マット構成とし、中央にリード・ライトデータレジスタ、シフトレジスタを配置することによってチップ幅の低減を図った。本マット構成によって、チップサイズは $4.6 \mu m \times 13.64 \mu m$ を実現し、 $7.62 \mu m$   $\{300 \mu mil\}$   $18 \nu \nu \nu \rightarrow 18 \mu m$   $\{300 \mu mil\}$   $\{18 \nu \nu \nu \rightarrow 18 \mu m$   $\{18 \nu \nu \rightarrow 18 \mu m\}$   $\{18 \nu \nu \rightarrow 18 \mu m$

# 5 電気的特性

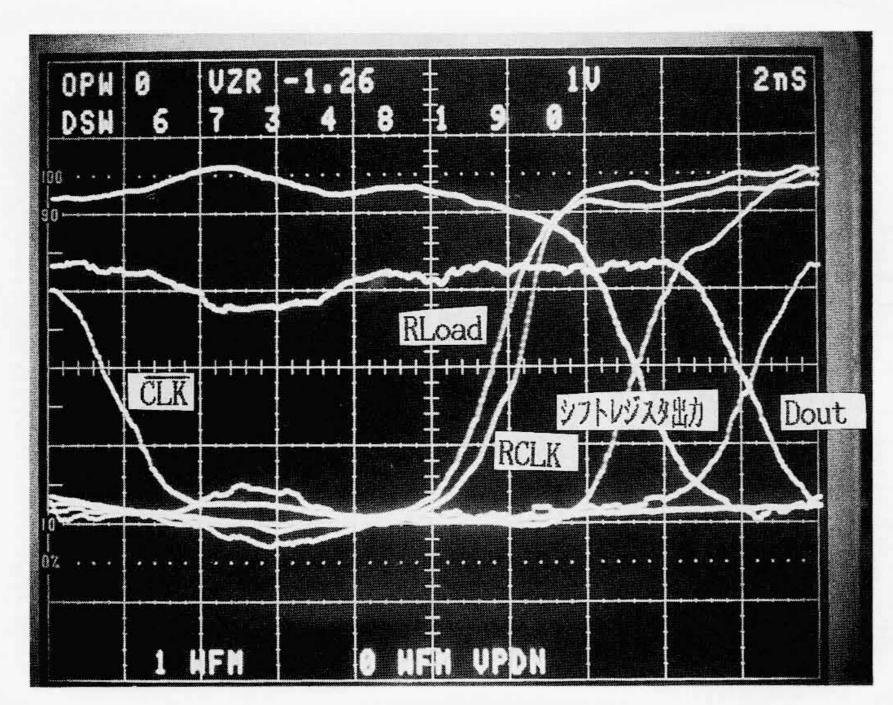

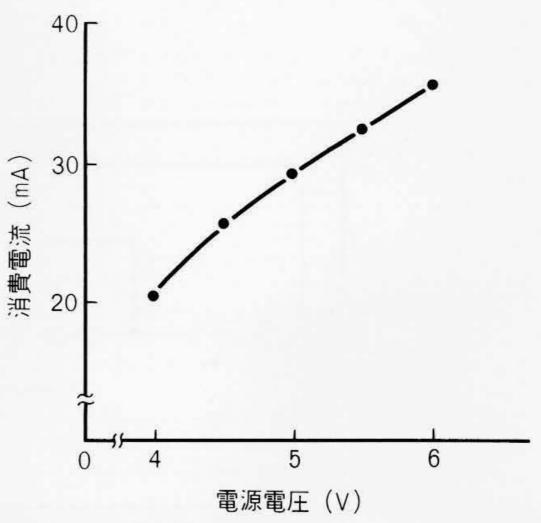

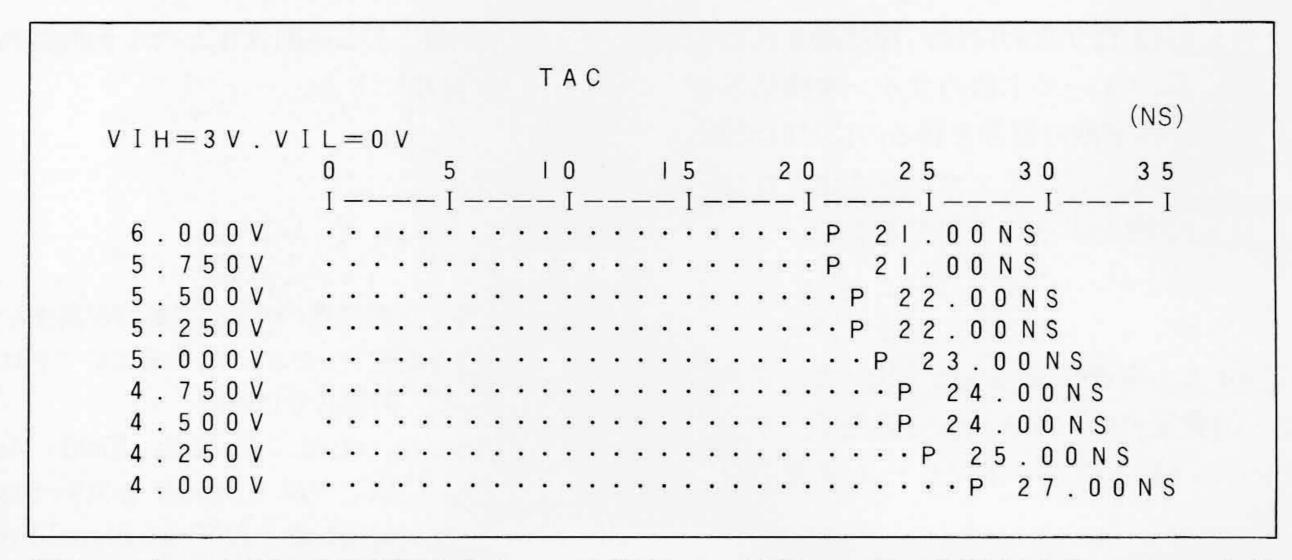

図8にアクセス時の内部波形を、図9にアクセス時間の電源電圧依存性を示す。このサンプルでは、電源電圧 5 V、周囲温度25  $\mathbb{C}$ の標準測定条件で $\overline{CLK}$ からのアクセス時間は23 nsを示す。図10にサイクル時間60 nsでの消費電流の電源電圧依存性を示す。標準測定条件で消費電流は29 mAである。

#### 6 応 用

HM53051はディジタルテレビジョン、VTRなどの映像機器システムや、FAX(ファクシミリ)、レーザビームプリンタなどのOA(Office Automation)・通信システムの各種画像信号処理に幅広く応用できる。このうちディジタルテレビジョンの応用について以下に説明する。

### 6.1 フィールド遅延

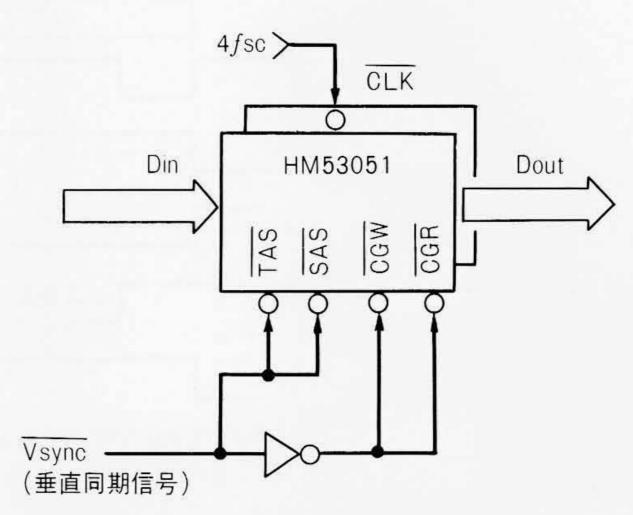

図11に、HM53051を2個用いて1フィールド遅延を構成する場合の応用例を示す。1フィールドに1回アサートされる

図7 HM53051チップ 写真 1.3 µm CMOSプロセスの採用と、メモリマット 4 マット構成によりチップサイズ4.6 mm×13.64 mmを実現した。

図8 アクセス時の内部波形 リードデータレジスタからシフトレジスタへデータ転送時の内部波形を示す。

垂直同期信号 ( $\overline{V}$ sync) を $\overline{T}$ AS,  $\overline{S}$ ASに入力することによって、システムリセットを行う。また、 $\overline{V}$ syncを反転して $\overline{C}$ GW,  $\overline{C}$ GR に入力し、システムリセット後、32クロック以上 $\overline{C}$ GW,  $\overline{C}$ GR をハイにすることによって、入出力データのタイミングを合わせる。

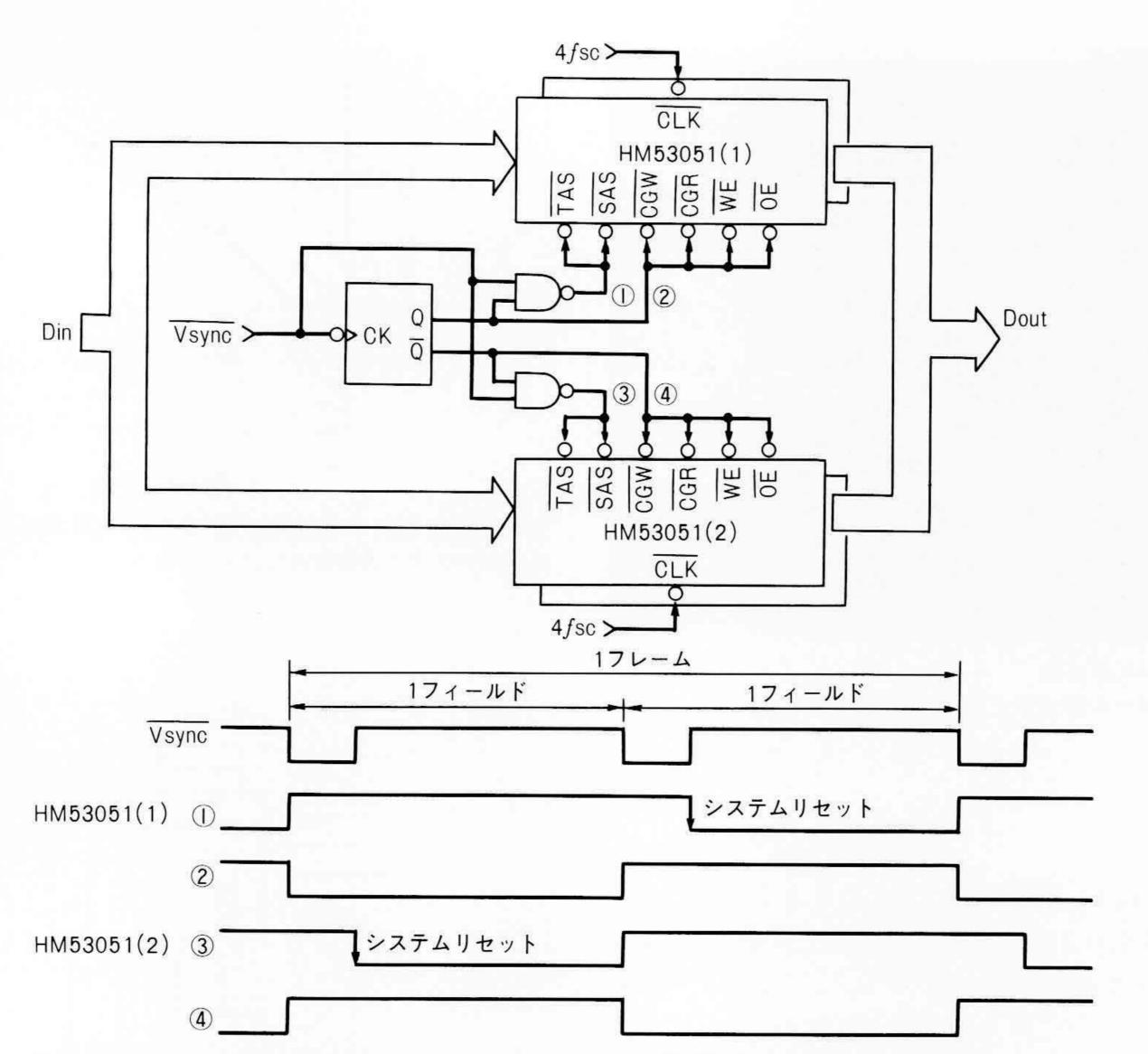

#### 6.2 フレーム遅延

図12はHM53051を 4 個用いて 1 フレーム遅延を構成した場合の応用例を示したものである。 1 フィールドごとに $\overline{CGW}$ ,  $\overline{CGR}$ をアサートし, 1 フレームに 1 回システムリセットを行うことにより,フレーム遅延を構成する。入力と出力は, $\overline{WE}$ ,  $\overline{OE}$ により 1 フィールド毎に切り換えている。

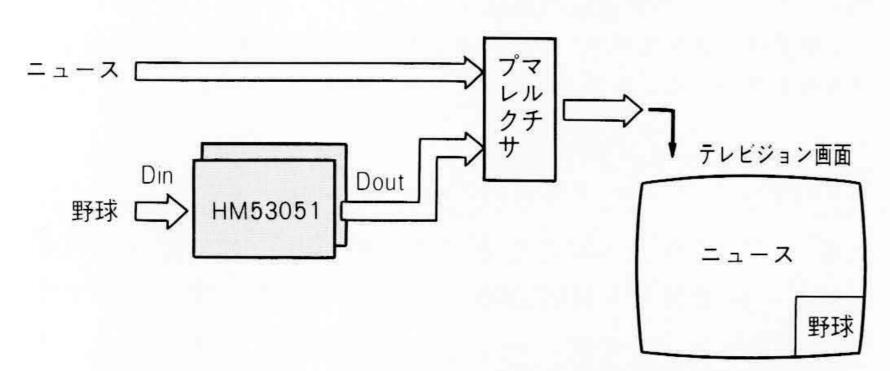

## 6.3 ピクチャインピクチャ

ピクチャインピクチャは一つのテレビジョン画面(親画面)の中に別チャネルの映像信号を圧縮して子画面とし、親画面の一部に埋め込む処理が必要となる。垂直方向の圧縮は、ラインアドレスを外部で演算し、ランダムアクセスを行うことによって実現する。水平方向の圧縮は、CGWによりデータを

図10 消費電流の電源電圧依存性 電源電圧 5 V, 周囲温度 25 ℃の標準測定条件で消費電流は29 mAである。

図II | フィールド遅延の構成例 | フィールドに | 回アサートされる垂直同期信号を用い、システムリセットと入出力データのタイミングを合わせることによって、| フィールド遅延をつくる。

スキップしてライトすることによって行う。このようにして 圧縮した映像信号をHM53051に記憶しておき、図13に示すよ うに、ブラウン管に映し出すときに親画面と子画面をマルチ プレクスする。

#### 6.4 ラインメモリとの組合せによる倍速変換

図14にラインメモリHM630213)との組合せによる倍速変換

図 9 アクセス時間の電源電圧依存性 電源電圧 5 V, 周囲温度25 ℃の標準測定条件でアクセス時間は23 nsである。

図12 | フレーム遅延の構成例 | フィールドごとにCGW, CGRをアサートし、| フレームに | 回システムリセットを行うことで、フレーム遅延を構成する。

図13 ピクチャインピクチャ 圧縮した子画面の映像信号をHM53051 に記憶しておき、ブラウン管に映し出すときに親画面と子画面をマルチプレクスする。

図14 倍速変換 倍速変換を行うためのライン補間信号として, HM53051に記憶された | フィールド前の映像信号を用いる。

の応用例を示す。倍速変換を行うためには、飛び越されたラインの補間信号として、1フィールド前のライン映像信号が必要となる。この1フィールド前の信号を得るのにHM53051を使用する。倍速変換により、ノンインタレース化された信号が得られ、垂直解像度を向上することができる。

#### 7 結 言

1.3 μm CMOSプロセスと高速化回路技術を用いて、アクセス時間は23 ns typ., 消費電流は29 mA typ.と高速で、かつ低消費電力特性を持っている 1 Mビットフレームメモリ HM 53051を開発した。

高速シリアルアクセス機能とともに、ランダムアクセス機能を備えており、テレビジョンやVTRのフレーム相関を利用

したY・C分離による高画質化とマルチ画面表示などの多機能 化を容易に実現できる。

#### 参考文献

- 1) 吉沢,外:次期家電の柱として期待が高まるディジタル技術を使った高解像度テレビジョン,日経エレクトロニクス,No.405,p.123~143,9月8日号(1986)

- 2) I. Nakagawa, et al.: A 1Mb Field Memory for TV Pictures, CICC, Vol. CH2430, p.319~322, Sep. (1987)

- 3) S. Matsumoto, et al.: A Video Signal Processing 20 ns 2 k×8 Multi-Function Memory, ISSCC Digest of Technical Papers, p.186~187, Feb. (1987)