U.D.C. (621.3.049.774.2'14:681.325) : [658.512.2.011.56.012.7:681.322.068]

# 自動診断技術

## ―テスト設計の自動化―

Auto-Diagnosis Technology

—Design Automation for Testing—

LSIの高集積化とともに、ASIC(Application Specific IC)でも、ユーザー設計工数削減の意味から、テスト設計の自動化が重要となってきた。しかし、単にテストパターンの自動生成を用いただけでは高品質のテストパターンを生成することは望めない。そこで、論理設計の段階からテスト容易化を考慮するテスト容易化設計方式が必要となっている。このような背景から、ゲートアレー用テスト設計自動化システムとして、テスト容易化設計からテストパターン設計まで一貫してサポートするシステムを開発した。これは、QTAT(Quick Turn Around Time)と高品質テストパターンの作成という両立困難と考えられる課題をクリアすることを可能とするシステムであり、CMOSゲートアレーへの適用によって効果を発揮している。

畠山一実\* Kazumi Hatayama 林 照峯\* Terumine Hayashi 甲把 健\*\* Takeshi Gappa 道下 智\*\* Satoshi Michishita

## 1 緒言

近年, LSIの高集積化に伴って, ASIC (Application Specific IC)の世界でも、フリーチャネルゲートアレーによる大 規模論理の搭載、およびセルベースICによるCPUコアなどの 搭載が可能になってきた。これとともに, ユーザー設計工数 削減の意味から、テスト設計(故障検査用テストパターンの作 成)の自動化が重要になってきた。しかし、単にテストパター ンの自動生成を用いただけでは, 高品質のテストパターンを 生成することは望めない。これに対処する方法として、論理 設計の段階からテストがしやすいように配慮するテスト容易 化設計方式1)がある。その中でも、スキャン設計方式2),3)は有力 な方法としてコンピュータ用LSIの設計などに広く適用されて いる。しかし、この方式は煩雑な論理設計規則を守る必要が あるため、一般のASICユーザーには使いにくいものであった。 さらに、ASICでは、トータルQTAT(Quick Turn Around Time)\*1)が重要であるため、論理設計者の負担増となる方式 は採用困難であった。これらの問題を解決するのが以下に示 す自動診断技術である。

ここで紹介するゲートアレー用テスト設計自動化(DA: Design Automation)システムは、テスト容易化設計からテストパターン設計まで一貫してサポートするシステムである。スキャン方式としては、論理設計者に負担をかけないスキャンバス方式4)、またはその変形であるスキャンシフト方式が用いられる。また、テストパターンの生成では、高精度なモデ

ル化および高性能なアルゴリズムにより,高い故障検出能力を達成している。以下,本システムの機能概要および特徴ならびに適用状況について述べる。

### 2 システム機能の概要

ゲートアレー用テスト設計自動化システムを,より有効な システムにするためには,以下の点に留意する必要がある。

- (1) 論理設計者の負担をできるかぎり少なくする。

- (2) 人手によるテストパターン追加作成を不要にする。

- (3) 対象となるハードウェアの進歩に柔軟に対応できる。

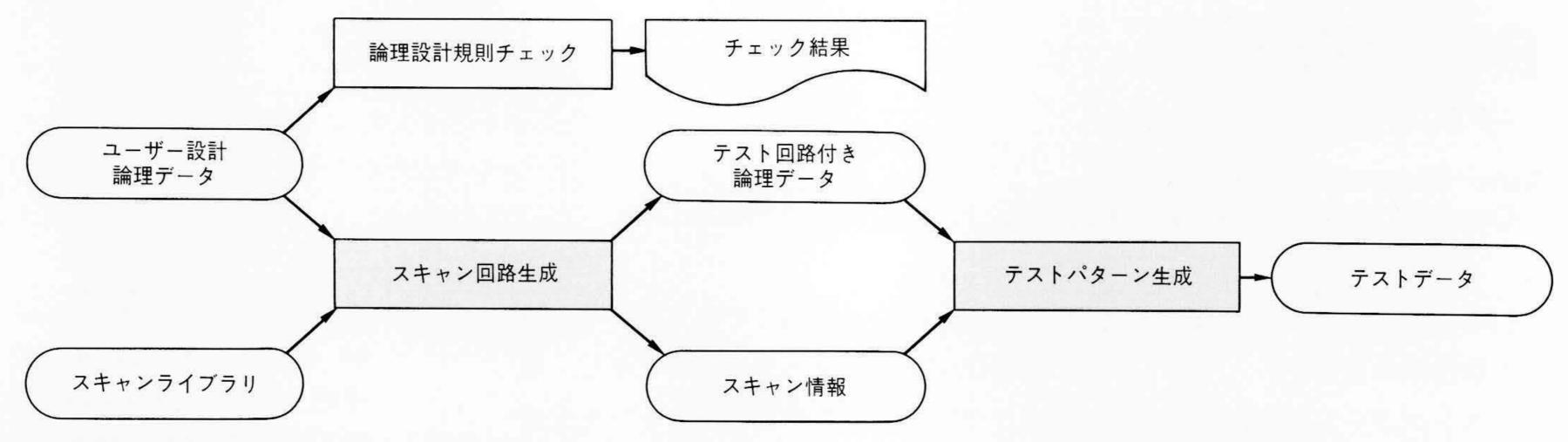

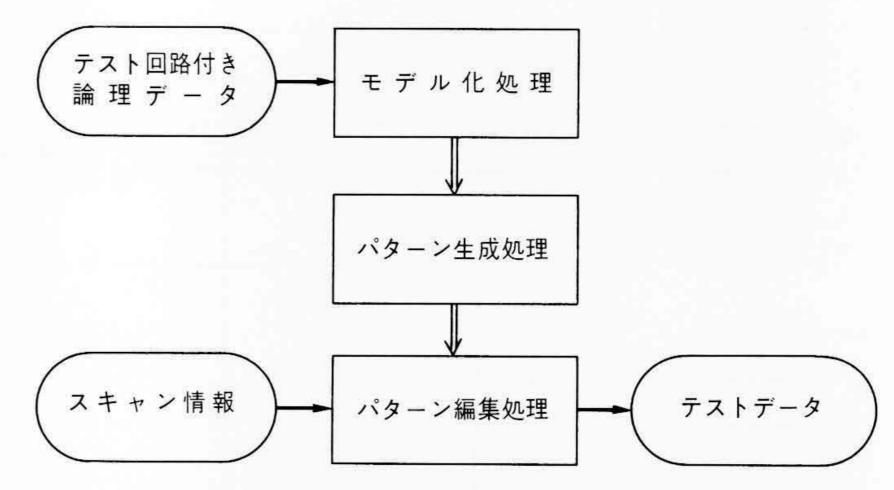

以上を考慮して**、図1**に示すような三つのプログラムから 成るテスト設計自動化システムを開発した。

論理設計規則チェックプログラムは、スキャン方式による テストを行うために必要となる論理設計規則が守られている かどうかをチェックする。ただし、スキャンバス方式および スキャンシフト方式では、論理設計者が守るべき論理設計規 則はゲートループ\*2)の禁止だけであるため、論理設計規則チ

<sup>※1)</sup> 一つのLSIの構想から製品の入手までの期間の短縮

<sup>※2)</sup> フリップフロップなどの記憶素子を含まない、ゲート素子だけから成るフィードバックループである。一種の記憶回路となるため、スキャン方式によるテストの有効性が失われる。

<sup>\*</sup> 日立製作所 日立研究所 工学博士 \*\* 日立製作所 半導体設計開発センタ

図 | テスト設計自動化システムの構成 本システムは、テスト容易化設計からテストパターン設計までを一貫してサポートする。

ェックプログラムは、ゲートループの有無だけをチェックしている。このプログラムで違反が指摘された場合には論理変更が必要となるが、これについては、違反時にはループに含まれるゲート名を出力することにより、簡単に論理変更できるようにしている。

スキャン回路生成プログラムは、スキャン設計方式によらずに設計されたユーザーの論理回路データを、スキャン構造を持つテスト回路付きの論理回路データに変換する。

また、テストパターン生成プログラムは、スキャン構造を持つ論理回路に対して、分割診断方式\*\*3)によってテストパターンを生成する。これらのプログラムについては、次章以下で述べる。

## 3 スキャン回路生成

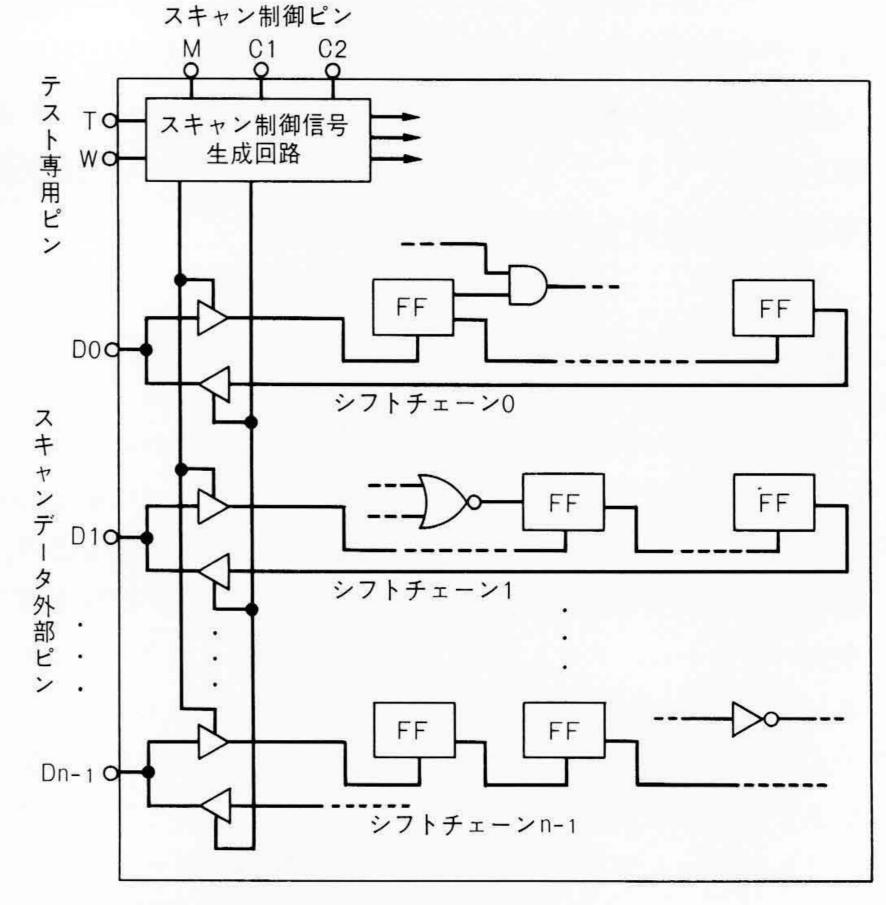

スキャン回路生成プログラムでは、ユーザー設計による一般の論理回路をスキャン構造を持つ論理回路へ自動変換する。本システムでサポートしているスキャン方式の一つであるスキャンシフト方式を用いた場合の、スキャン構造の概略を図2に示す。スキャンシフト方式は、テスト用回路として、テスト用外部ピン\*4,スキャン制御信号生成回路\*5,シフトチェーン\*6)などを必要とする。また、フリップフロップとしては、スキャン機能付きフリップフロップ(図3に一般構成を示す。)を用いる必要がある。そこで、スキャン回路生成プログラム

注:略語説明

FF (フリップフロップ), M (スキャンモード制御) C1 (スキャン第1相クロック), C2 (スキャン第2相クロック) T (テストモード), W (スキャン イン モード), D (スキャンデータ)

図2 スキャンシフト方式でのスキャン構造の概略 スキャンシフト方式では、各フリップフロップへのスキャンインおよびスキャンアウトはシフトチェーンを経由して行われる。

※3) 全体回路(順序回路)を部分組合せ回路の集合に分割して,分割の路単位でテストパターンを生成する方式である。

- ※4) テスト用信号を供給・観測するための外部ピンである。テスト専用ピン、スキャン制御ピン、スキャンデータ外部ピンがあるが、テスト専用ピン(2ピン)以外は通常動作用の外部ピンとの兼用が可能である。

- ※5) スキャンインおよびスキャンアウトを制御するための内部信号を生成する回路である。

- **※6**) スキャンインあるいはスキャンアウトされるデータを,順次 シフトするための伝送路である。

では、スキャン情報の生成およびスキャン回路の生成の2段 階処理によって論理回路の変換を行っている。

スキャン情報の生成では、スキャン構造の枠組みの決定、テスト用外部ピンの割り当て、およびフリップフロップへのスキャンアドレスの割り当てを行う。ここでは、テスト回路によるゲート数の増加(ゲートオーバヘッド)をなるべく大きくしないように考慮している。また、一般にテスト専用ピン以外のテスト用外部ピンは、通常動作用の外部ピンと兼用されるが、割り当て対象ピンおよび割り当て禁止ピンの指定により、ピン兼用時のディレイ増に伴う問題の発生を回避でき

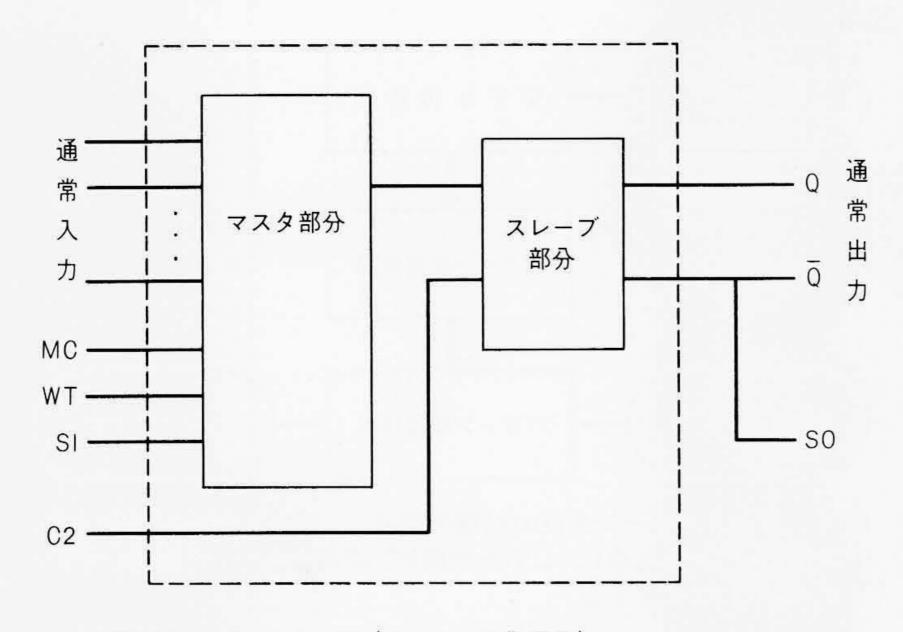

注:略語説明 MC, WT, C2 (スキャン制御信号) SI (スキャン イン データ), SO (スキャン アウト データ)

図3 スキャン機能付きフリップフロップの一般構成 一種のマ スタ スレーブ タイプの構成により、スキャン方式によるテストを行う ために必要となる論理設計規則を自動的に満足する。

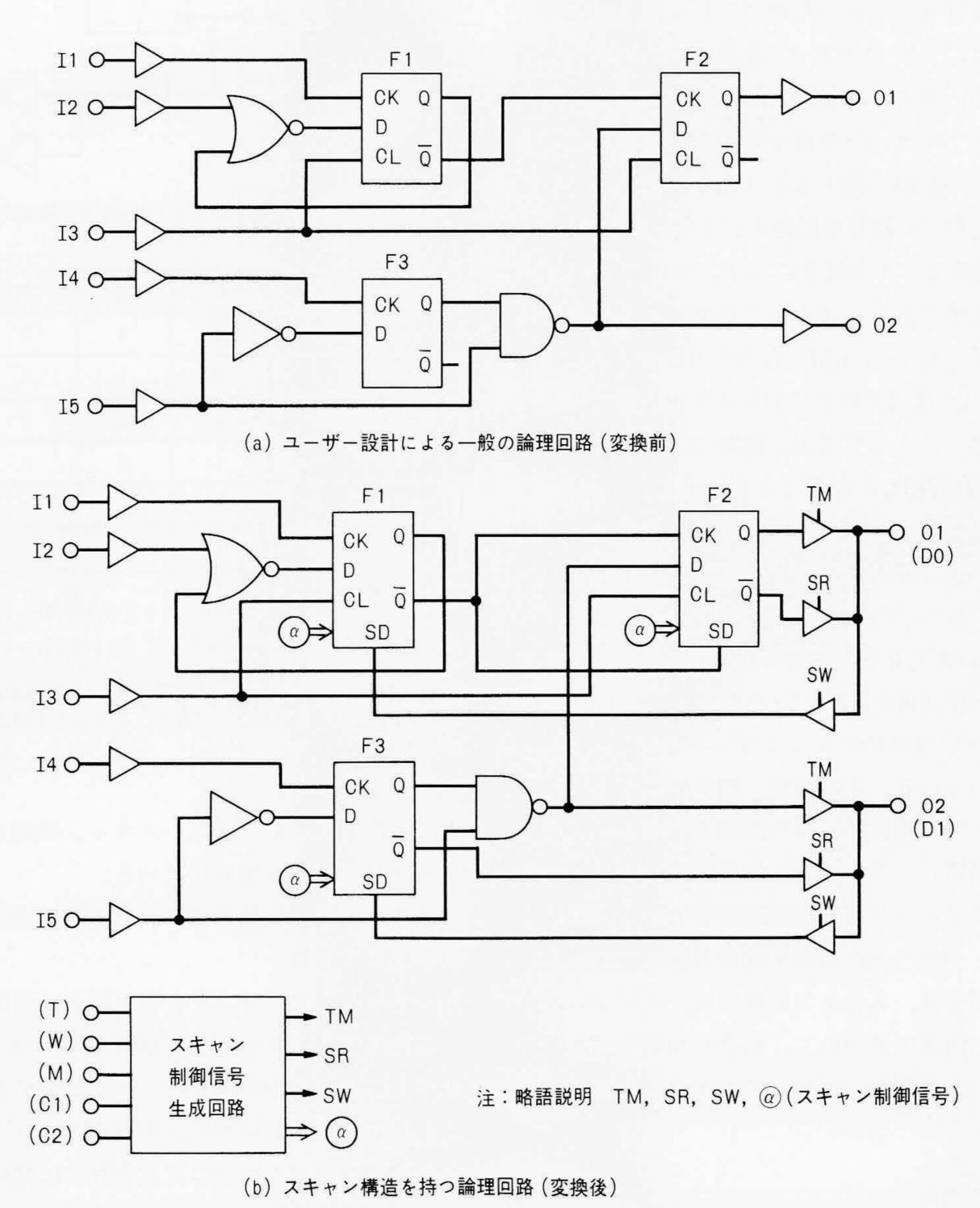

図 4

るようにしている。スキャン情報を生成したのち、これに基 づいてスキャン回路の生成を行う。ここでは、テスト専用の 外部ピンの生成と外部ピンの兼用に伴う切換回路の生成, フ リップフロップの置き換えとフリップフロップへのスキャン 信号の付加、およびその他のテスト用回路の生成を行ってい る。一般の論理回路からスキャン構造を持つ論理回路への変 換例を図4に示す。同図で、(a)の3個のフリップフロップに 対して2本のシフトチェーンを用いるものとした。また、こ れに伴い、スキャンデータ外部ピンD0、D1をそれぞれ通常動 作用外部出力ピンO1, O2とそれぞれ兼用するものとした。(a) の各フリップフロップがスキャン機能付きフリップフロップ に置き換えられたのち、スキャン制御信号およびシフトチェ ーンが接続される。さらに、スキャン制御信号生成回路およ び兼用ピン切換回路が付加されて、(b)のスキャン構造を持つ 論理回路が生成される。

(a)の論理回路にテスト用回路が付加されて, (b)のようになる。ただし, 論理回路の変換例 OI, O2はテスト用外部ピンD0, DIとそれぞれ兼用されている。

最後に、以上に述べた以外のスキャン回路生成プログラム の特徴を以下にまとめて述べる。

#### (1) テストパターン生成プログラムとの整合性

テスト回路付き論理データに加えて、スキャン情報も出力 しており、スキャン構造がスキャンパターンに正しく反映さ れることを保証している。

#### (2) スキャンライブラリ利用による柔軟性

スキャン回路の生成規則などの論理回路の変換に用いるルールは、スキャンライブラリに記述されている。このため、スキャン回路の仕様変更、I/Oの強化、新たなフリップフロップの追加などにも柔軟に対応することができる。さらに、異なったスキャン方式にも対応が可能である。

## 4 テストパターン生成

テストパターン生成プログラムでは,スキャン構造を持つ 論理回路に対して,故障検査用テストパターンを作成する。 テストパターン生成プログラムの処理の流れを図5に示す。

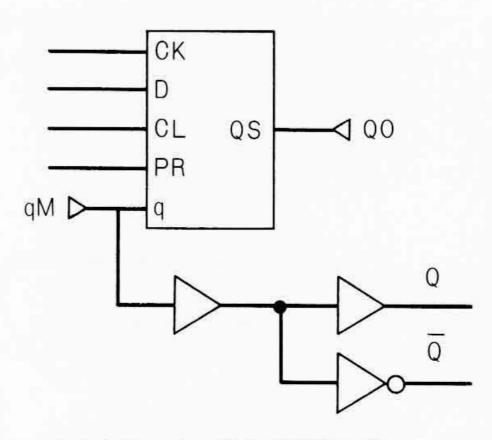

モデル化処理では、テストパターン生成のための組合せ回路モデルを作成する。スキャン設計方式により、組合せ回路モデルを用いたテストパターン生成が可能となるが、ここではクロック系回路上の故障も扱えるようにするため、フリップフロップを含めた形での組合せ回路モデル化を行っている。Dラッチの組合せ回路モデルを図6に示す。ここで、qは初期状態に対応する入力値であり、スキャンインによって自由に設定できるため、仮入力エッジqMからの入力信号とみなすことができる。また、QSは内部状態に対応する出力値であり、やはりスキャンアウトによって自由に観測できるため、仮出力エッジQOへの出力信号とみなすことができる。

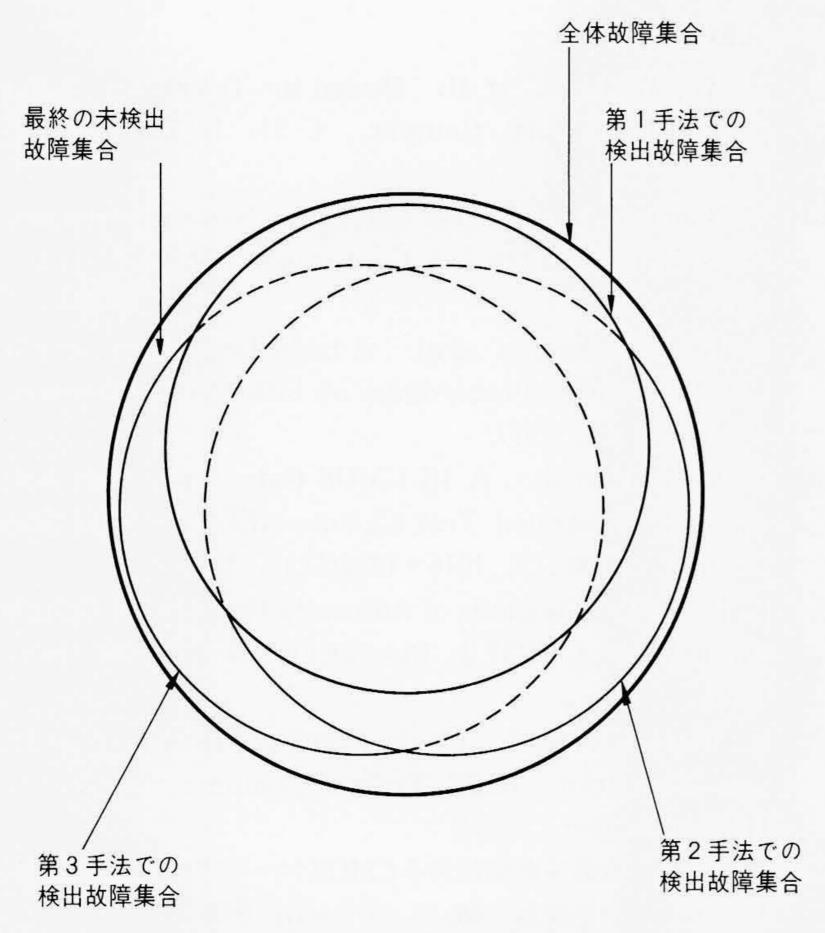

パターン生成処理では、組合せ回路モデル上でのテストパターンを生成している。組合せ回路を対象としたテストパターン生成アルゴリズムとしては、Dアルゴリズム<sup>5)</sup>、FANアルゴリズム<sup>6)</sup>など多くの有力な手法が知られている。本プログラムでは、これらの手法の考え方をベースとして、実回路を扱えるように拡張した\*<sup>7)</sup> 3種のアルゴリズムを開発し、これらを組み合わせて用いている。すなわち、図7に示すように、第1のアルゴリズムで未検出となった故障を対象として第2のアルゴリズムを適用し、さらにそれでも未検出となる故障に対しては、第3のアルゴリズムを適用するという方法により、高品質なテストパターンの自動生成を可能にしている。

パターン編集処理では,スキャン回路生成プログラムから 出力されたスキャン情報に基づいて,組合せ回路モデル上で 生成されたテストパターンを,実チップに対するテストデー

図 5 テストパターン生成の処理の流れ 組合せ回路モデル化の後, テストパターンを生成し,これを外部ピンでのパターンに編集してテストデータとして出力する。

(a) Dラッチの組合せ回路モデル

| No. | CK | D | CL | PR | q | QS |

|-----|----|---|----|----|---|----|

| 1   | 1  | 0 | Х  | 0  | Х | 0  |

| 2   | 0  | Χ | 1  | 0  | X | 0  |

| 3   | 0  | Χ | Х  | 0  | 0 | 0  |

| 4   | 1  | 1 | 0  | Х  | Х | 1  |

| 5   | 0  | Χ | 0  | 1  | Х | 1  |

| 6   | 0  | Χ | 0  | X  | 1 | 1  |

(b) Dラッチの真理値表

注:略語説明 qM(仮入力エッジ), QO(仮出力エッジ)

図 6 Dラッチの組合せ回路モデル 初期状態qを仮入力エッジqMからの入力信号とみなすことにより、Dラッチを組合せ回路として扱うことができる。

タに変換している。また、スキャン機能をテストするための テストパターンも生成している。

テストパターン生成プログラムの特徴をまとめると、以下 のとおりである。

- (1) フリップフロップを含めた組合せ回路モデル化 これにより、クロック系回路を含めたユーザー設計論理の すべてに対してテストパターンが作成できる。

- (2) 3種のテストパターン生成アルゴリズムの併用 各アルゴリズムの持つ欠点を互いに補いあうことにより、 どのような論理データに対しても、高い故障検出能力を持つ テストパターンを生成できる。

<sup>※7)</sup> トライステート素子, 双方向バスなどのサポート, およびフリップフロップの組合せ回路モデルへの対応など。

図7 アルゴリズムの併用による未検出故障の削減 各手法の弱点を互いに補いあうことにより、最終の未検出故障数を削減している。

## 5 適用状況

以上に述べたテスト設計自動化システムを用いた自動診断機能は、CMOSゲートアレーHG62Bシリーズ<sup>7)</sup>に適用されて以来、HG62Eシリーズでも効果を発揮している。**表1**の適用実績に示すとおり、HG62Eシリーズでの自動診断機能は、10 kゲート以上では100%適用されており、ユーザーのテスト設計のTAT(Turn Around Time)を大幅に短縮している。また、10 kゲート以下の場合でも50%以上に適用されている。

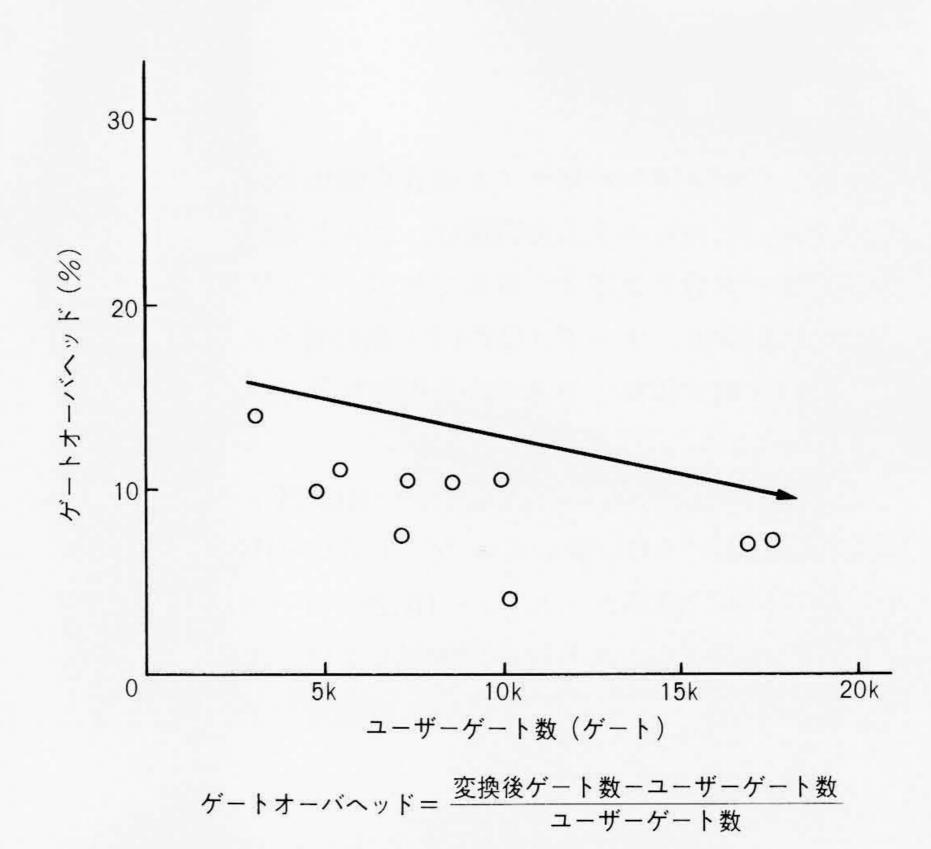

HG62Eシリーズでのテスト設計自動化システムの適用結果 を図8および図9に示す。ゲートオーバヘッドについては, ユーザーゲート数に関して減少傾向がみられる。これは回路

表 I HG62Eシリーズでの自動診断機能の適用実績 大規模回路では、100%自動診断機能が適用されている。

| ベース<br>チップ | ゲート数   | パッド数 | 適用率  | ユーザーTAT  |  |  |  |

|------------|--------|------|------|----------|--|--|--|

| E43        | 4,309  | 100  | F00/ | 6 週→0.3週 |  |  |  |

| E58        | 5,821  | 118  | 50%  |          |  |  |  |

| E75        | 7,488  | 138  | 000/ | 13週→0.4週 |  |  |  |

| E101       | 10,076 | 162  | 90%  |          |  |  |  |

| E130       | 13,015 | 190  |      | 35週→0.5週 |  |  |  |

| E182       | 18,176 | 230  | 100% |          |  |  |  |

| E240       | 24,020 | 272  |      |          |  |  |  |

注:パッド数はチップ上の最大値を示す。

ユーザーTAT (Turn Around Time) はユーザーでのテストパターン設計のTAT

図8 テスト設計自動化システムの適用結果(その1) ゲートオーバヘッドは、ゲート数に関して減少傾向がみられる。

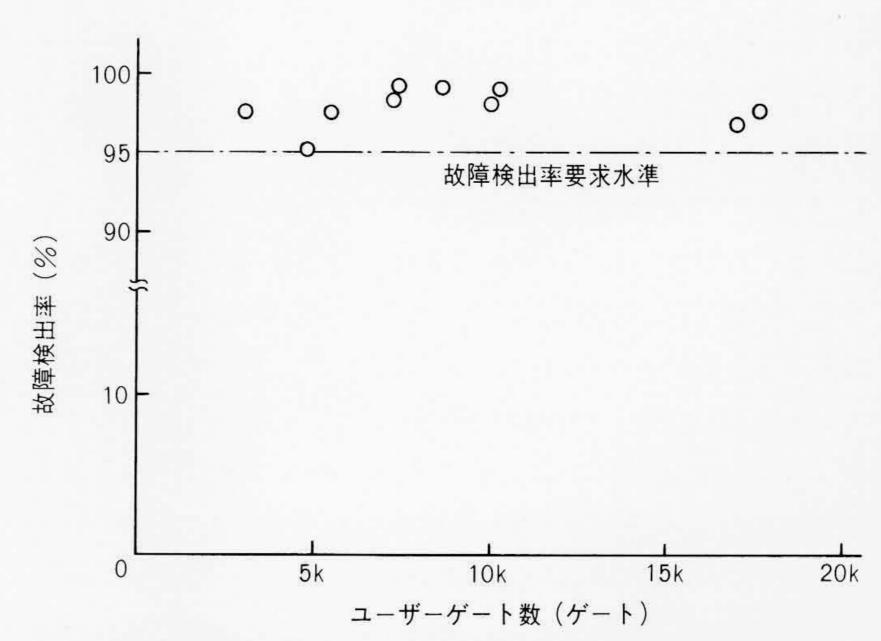

図 9 テスト設計自動化システムの適用結果(その 2) 故障検出 率はすべて要求水準(95%)をクリアしている。

の大規模化とともにフリップフロップの比率が減少すること、およびフリップフロップに含まれるオーバヘッドを除くと、 回路が大規模化してもそれほどオーバヘッドが増えないことが原因と考えられる。また、故障検出率については、すべてのデータで95%以上となっており、テストパターンの人手追加作成を必要としない基準を達成している。なお、故障検出率に多少のばらつきがみられるのは、冗長故障\*\*8)数の大小によるものと考えられる。

<sup>※8)</sup> 冗長回路が存在するため、故障が存在しても論理動作にその 影響が現れないもの。

## 6 結 言

以上、ゲートアレー用テスト設計自動化システムについて述べたが、このシステムの特徴は、テスト容易化設計からテストパターン設計までを一貫してサポートしていることにある。これにより、トータルQTATと高品質テストパターンの作成という両立困難と考えられる課題をクリアすることが可能となった。

本システムは、CMOSゲートアレーHG62Eシリーズで実用 化されており、フリーチャネル ゲートアレーHG62Sシリーズ およびHi-BiCMOSゲートアレーHG29シリーズに対しても適 用される。また、セルベースICに対しては、ユーザーの設計 するカスタム論理部への本システムの適用を予定している。

#### 参考文献

- 1) T. W. Williams, et al.: Design for Testability A Survey, IEEE Trans. Comput., C-31, 1, 2~15 (Jan., 1981)

- 2) S. Funatsu, et al.: Test Generation Systems in Japan, Proceedings of 12th DA Conference, 114~122 (June, 1975)

- 3) E. B. Eichelberger, et al.: A Logic Design Structure for LSI Testability, Proceedings of 14th DA Conference, 462~468 (June, 1977)

- 4) S. Kuboki, et al.: A 4K CMOS Gate Array with Automatically Generated Test Circuits, IEEE J. Solid-State Circuits, SC-20, 5, 1018~1024(Oct., 1985)

- 5) J. P. Roth: Diagnosis of Automata Failures: A Calculus and a Method, IBM J. Res. Dev., 10, 278~291 (July, 1966)

- 6) H. Fujiwara, et al.: On the Acceleration of Test Generation Algorithm, IEEE Trans. Comput., C-32, 12, 1137~1144(Dec., 1983)

- 7) 道下,外:自動診断機能付きCMOSゲートアレイ「HG62Bシリーズ」,日立評論,**68**,7,573~576(昭61-7)