# ASIC用開発支援システム

# Development Support System for ASIC Microcomputer

製品の差異化のため、顧客ごとに仕様の異なるマイクロコンピュータへの要求が一段と強まってきている。このような顧客専用デバイスに対しても、プログラムおよび論理回路デバッグを効率よく行える開発ツール(エミュレータ)が必要不可欠である。また、エミュレータは短納期、顧客開発期間の短縮に効果のあるものでなければならない。

これらの要求にこたえるため、今回開発したエミュレータは、顧客ごとに異なる周辺機能を、機能モジュール単位で用意したデバイスを追加、交換することによって実現する。この結果、1台のエミュレータ装置で、各種顧客要求仕様に対応でき、また顧客への早期提供を可能とした。

石川泰代\* Yasushiro Ishikawa 本間和彦\* Kazuhiko Homma 石原孝治\* Kôji Ishihara 増田 訓\* Satoshi Masuda

## 1 緒 言

マイクロコンピュータ(以下、マイコンと略す。)は、家電品をはじめ各種産業機器制御に至るまで幅広く用いられている。マイコンを使用した製品では、これを動作させるプログラムを開発しなければならないが、このプログラム開発支援ツールとしてコンパイラ、エディタ、リンカ、シミュレータなどのソフトウェアツールのほかに、ハードウェアツールとしてエミュレータ(日立製作所ではASE: Adaptive System Evaluatorと呼称する。)がある。またASEには、プログラム開発支援ツールとして、プログラムデバッグを容易にする機能のほかに、顧客製品の論理回路デバッグを効率よく行えることも要求される。

最近では、製品の差異化のため、顧客ごとに仕様の異なるマイコンへの要求が一段と強まっている。このような顧客要求にこたえるため、日立製作所ではHD64180をCPUコアとしたASIC(Application Specific IC)マイコンを用意している。このASICユーザーへの開発支援システムの提供も必要不可欠になっているい。このような状況下で提供するASEに特に要求されるのは、いかに汎(はん)用性のあるASEにするかということである。

本稿では、ASIC用ASEの設計方針、ハードウェア構成と動作およびソフトウェア構成と動作について紹介する。

### 2 設計方針

CPU搭載形のASICで、顧客のシステム開発にはASEが必要 不可欠である。顧客ごとに異なるデバイス仕様に対するASE の開発では、同一のCPUコアを持つデバイスならば、同一のASEで顧客に提供することを前提とした。

この背景として、システム開発ではソフトウェアの生産性が重視され、CPUコアを同一としてその周辺機能を拡充していく品種展開形が多く、ソフトウェアの継承性が重要となっている。したがって、デバイスのちょっとした品種展開でも、同じASEでソフトウェア開発ができれば、その生産性の向上はもちろんのこと、顧客の開発投資も低減できる。

また、顧客の開発工程を考えた場合、ASEは製品デバイスができる以前に提供することが理想であり、特にASICでは提供までのTAT(Turn Around Time)が重要になってくる。

これらの背景を基に、ASIC用ASEは下記を条件として開発する必要がある。

- (1) CPUコアが同一ならば同一のASEとすることを前提にCPUコア部を共通化し、ASEに標準搭載する。

- (2) CPU周辺機能〔タイマ, ASCI(Asynchronous Serial Communication Interface)など〕はそれぞれにチップ化し、 顧客の選択によってASEに搭載できることとする。

- (3) カスタム論理に対応するため、ゲートアレーを載せる領域をASEに確保する。

- (4) デバイス仕様として、デバイス内部のメモリ空間、内部 I/Oアドレスの設定が任意にできること。

- (5) 製品デバイスの各種パッケージ、ピン配置に対応できること。

今回は64180をCPUコアとしたASIC用ASEを開発した。そ

<sup>\*</sup> 日立製作所 半導体設計開発センタ

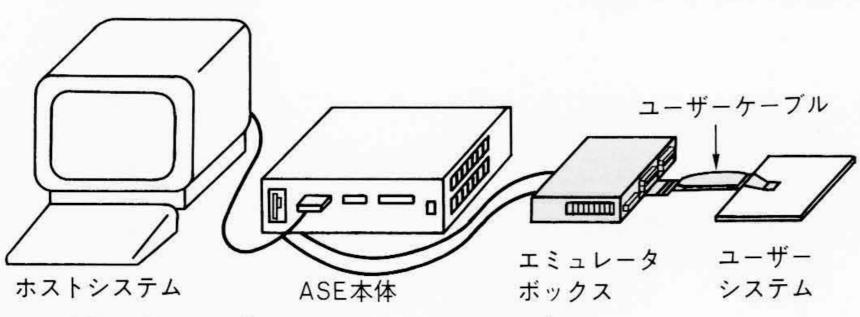

のシステム構成を**図1**に示す。64180ASIC用ASEは,ASE本体とエミュレータボックス部とで構成する。ASE本体はホストシステムとのインタフェースおよびエミュレーション情報のモニタを行う。このASE本体は,エミュレータボックスを交換すれば既存の64180シリーズマイコンのASE<sup>2)</sup>としても使用することができる。したがって,64180シリーズの汎用マイ

注:略語説明 ASE (Adaptive System Evaluator)

図 I 64180ASIC用ASEシステム構成 64180ASIC(Application Specific IC)用ASEの顧客デバッグ時でのシステム構成を示す。ASEは、ASE本体とエミュレータボックスから構成される。

表 I 64180ASIC用ASEの仕様 64180ASIC用ASEの機能, 仕様の一 覧表を示す。

| 機能                         | <b>仕</b> 様                                                                                                                                                                                                    |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| サポートクロック(動 作 周 波 数)        | ASE内部クロック:6.144 MHz<br>外部クロック:0.5~6.144 MHz                                                                                                                                                                   |

| デバイス情報設定機能                 | ASEの起動時にデバイス情報の設定・登録 <ul><li>●内蔵メモリのアドレス設定 (ROM/RAM)</li><li>●内蔵I/Oレジスタのアドレス設定</li><li>●モード設定 (シングルモード・マルチチップモード)</li></ul>                                                                                   |

| 貸し出しメモリ                    | <ul><li>●標準装備:64 kバイト</li><li>●オプション:256 kバイトメモリボード(2 枚まで実装可)</li></ul>                                                                                                                                       |

| ブ レ ー ク                    | <ul><li>●ハードウェアブレーク(2か所)</li><li>●ソフトウェアブレーク(256か所)</li><li>●シーケンシャルブレーク</li></ul>                                                                                                                            |

| リアルタイムトレース                 | 2048サイクル                                                                                                                                                                                                      |

| 主な他の機能                     | <ul> <li>●メモリ内容の逆アセンブル機能</li> <li>●ラインアセンブル機能</li> <li>●シンボリックデバッグ</li> <li>●実行時間の測定</li> <li>●メモリ内容,レジスタ内容の表示,設定,変更</li> <li>●メモリ内容の転送(ユーザーメモリー貸出しメモリ)</li> <li>●カバレジ機能(CO)</li> <li>●特定データの検索,変更</li> </ul> |

| ASE本体インタフェース               | <ul><li>■コンソールインタフェース<br/>(RS-232C)</li><li>●ホストシステムインタフェース<br/>(RS-232C)</li><li>●プリンタインタフェース<br/>(セントロニクス仕様)</li></ul>                                                                                      |

| 3.5インチフロッピーディスクドライバ        |                                                                                                                                                                                                               |

| ユーザーインタフェース<br>(サポートパッケージ) | QFP100, QFP136<br>(パッケージの品ぞろえ予定)                                                                                                                                                                              |

注:略語説明 QFP(Quad Flat Package)

コンからASICへの移行性がある。エミュレータボックスはユーザーシステムと接続し、デバイスのエミュレーションを行う。

また、本ASEの機能仕様を表1に示す。

# 3 ハードウェア設計

#### 3.1 ASIC用ASEの実現方法

CPU搭載形のASICでは、デバイス周辺機能、パッケージ、ピン配置、内蔵メモリ、レジスタのアドレス割り付けなどが顧客ごとに異なる。それらの異なる仕様に対して、ASEでのサポート方法を以下に記述する。

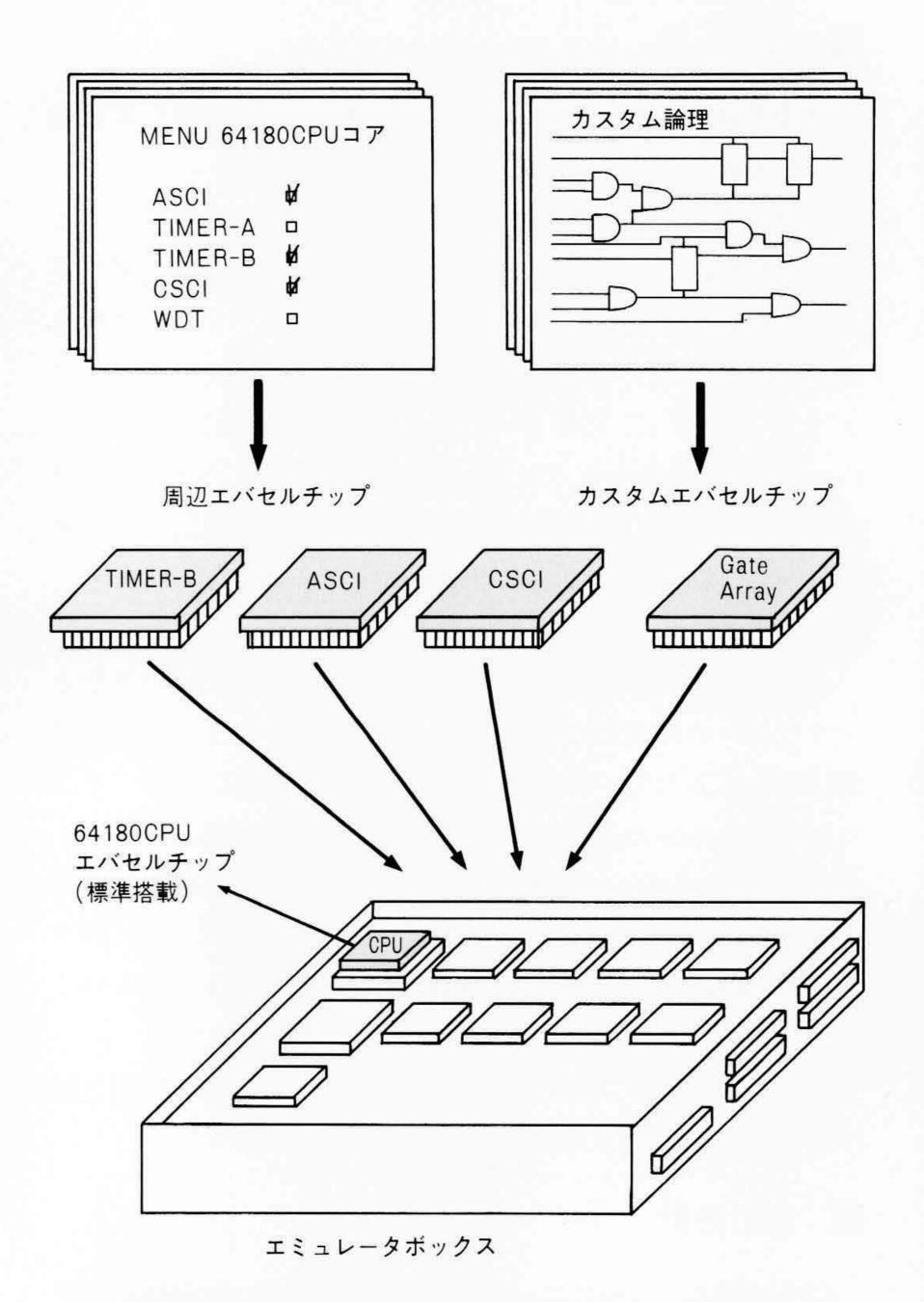

図2に示すように、64180ASIC用ASEでは、CPUコアとバスマスタ系〔DMAC(Direct Memory Access Controller)、リフレッシュコントローラなど〕を1チップ化し(CPUエバセルチップ)、ASEに標準搭載することによって共通化を図った。

注:略語説明 ASCI (Asynchronous Serial Communication Interface)

CSCI (Clocked Serial Communication Interface)

WDT (Watchdog Timer)

図2 エバセルチップ方式ASE ASIC用ASEの方式として、デバイスの機能を分割、チップ化してASEに搭載するエバセルチップ方式を採用した。顧客がメニューから選択したエバセルチップを搭載する。

また、周辺機能モジュールはそれぞれにチップ化し(周辺エバセルチップ)、そのチップのラインアップをする。また、ASE上にはソケットを準備し、顧客の選択により機能モジュールを実装可能とした。カスタム論理に関しては、ゲートアレー(カスタムエバセルチップ)を実装することで実現させている。

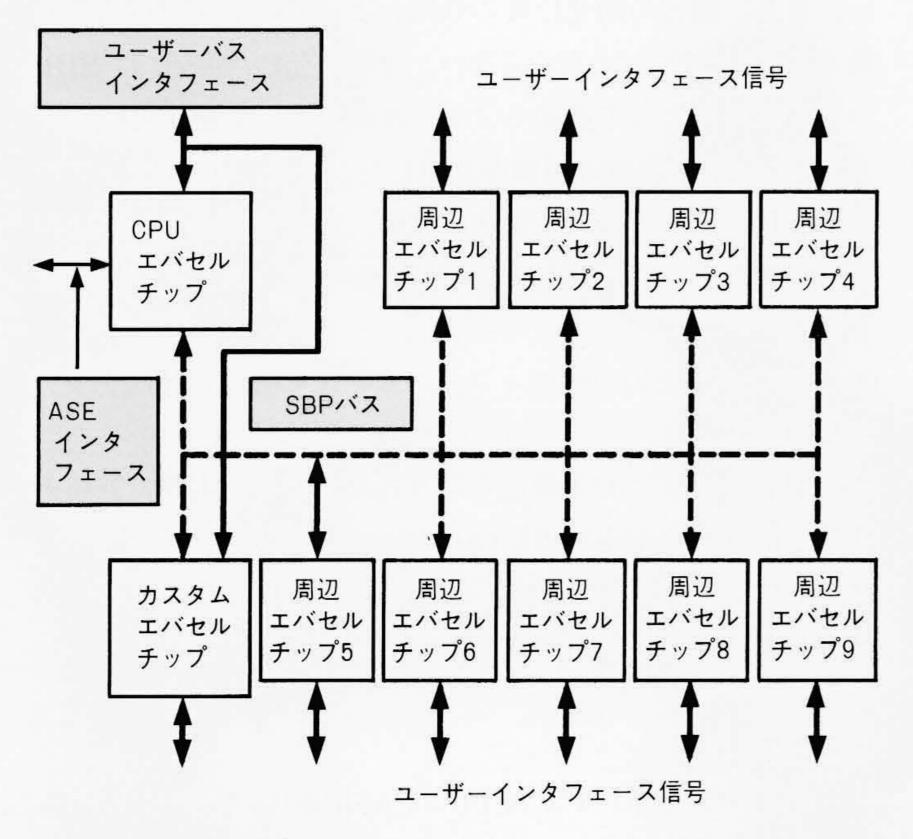

エミュレータボックス内のエバセルチップの構成を図3に示す。この図のようにCPUエバセルチップはASEを共通化させるために、そのインタフェース仕様(信号)を標準化する必要があり、インタフェース方式は下記の3バス構成とした。

- (1) ASE制御回路とインタフェースをとるバス

- (2) 周辺エバセルチップとインタフェースをとるバス

- (3) ユーザーシステムとインタフェースをとるバス

この3バス構成にすることによって各インタフェースを独立させ、それぞれのバスを容易に標準化した。ASEとのインタフェースバスは、デバッグ情報として必要な信号を取り出すとともに、エミュレーションを制御する信号を持っている。

顧客が選択する周辺エバセルチップとのインタフェースは、デバイス内部で使用するSBP³)(Silicon Back Plane)バスをASE基板上に布線することで実現した。また、周辺エバセルチップの実装は、パッケージの統一、ピン配置の固定化により、ソケットへの挿入を可能とした。すなわち、ASEでのSBPバスの採用は、顧客ごとに異なる周辺機能も周辺エバセルの追加交換だけで実現し、顧客仕様に合ったエバセルを容易に提供できることになる。カスタムエバセルチップには、SBP

注:略語説明 SBP (Sillicon Back Plane)

図3 エミュレータボックス内のエバセルチップ構成 ASIC用ASE のエミュレータボックス内のエバセルチップ構成を示す。主にCPUエバセルチップ, 周辺エバセルチップ, カスタムエバセルチップとのSBPバスを介してのインタフェースを示す。

表 2 エバセルチップの仕様 ASEに搭載される各エバセルチップの 仕様一覧表を示す。機能とインタフェース信号パッケージの分類である。

| チップ種類                    | 機能概略                                                                          | ユーザーインタ<br>フェース                                                             | パッケージ                    |

|--------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------|

| CPUエバセル<br>チップ<br>(標準装備) | 64180CPUコア<br>MMU<br>DMAC<br>リフレッシュコン<br>トローラ<br>WAITコントローラ<br>割り込みコントロ<br>ーラ | アドレスバス:<br>20本<br>データバス:8本<br>制御信号:18本<br>割り込み入力:<br>16本<br>DMAC制御信号:<br>8本 | PGA240<br>I 個            |

| 周辺エバセルチップ                | ユーザーが選択<br>例<br>タイマ<br>ASCI<br>CSCI                                           | ユーザーインタ<br>フェース<br>信号: Max.24本/<br> 個                                       | PGA135<br>ソケット 9 個<br>装備 |

| カスタムエバセルチップ              | ユーザーのカスタ<br>ム論理                                                               | ユーザーインタフェース<br>信号:Max.64本                                                   | PGA240<br>ソケット I 個<br>準備 |

注: 略語説明

PGA (Pin grid Array)

MMU (Memory Management Unit)

DMAC (Direct Memory Access Controller)

ASCI (Asynchronous Serial Communication Interface)

CSCI (Clocked Serial Communication Interface)

バスとユーザーバスが接続され、ユーザーの選択でバスを使い分けることができる。以上、3種類のエバセルチップの仕様を表2にまとめる。

#### 3.2 ユーザーシステムとの接続

ASIC展開では、デバイスのパッケージも顧客ごとに異なってくる。したがって、ASEでのユーザーシステムとの接続も、パッケージごとに準備する必要がある。

そこでASIC用ASEでは、パッケージ品種ごとにユーザーシステムとの接続をとるユーザーケーブルを準備する。また、ユーザーケーブルとエミュレータボックスとの接続は選択性をもたせ、パッケージのピン配置に合わせることができるように、リード線をエミュレータボックスのコネクタに差し込む方式とした。

エミュレータボックスのコネクタには、CPUエバセルチップからのユーザーバス、各周辺エバセルチップからのインタフェース信号(最大24本×9個)、カスタムエバセルチップからのインタフェース信号(最大64本)を用意している。

# 3.3 メモリとI/O空間の割り付け

ユーザーには、シングルチップでメモリをデバイスに内蔵させる仕様もある。デバイス内蔵メモリのサポートはASE内部にSRAM(Static RAM)を設け、顧客の仕様によってそのアドレスと容量を任意に割り付けることができるようにした。ASE内部に用意しているSRAMは、内蔵ROM(Read Only

Memory) 用に64 kバイト,内蔵RAM用に64 kバイトまで備えている。EEPROM (Electrically Erasable and Programmable ROM) に関しては,ASE内部回路で擬似的に設けることが不可能なため,実チップと同一な周辺エバセルチップとして供給することとした。

一方,周辺機能のI/Oレジスタアドレスは,その機能モジュールによって異なるため,I/OレジスタのアクセスはI/O空間のアドレス20~FF(16進数)の領域で任意に割り付けができるようにした。

## 4 ソフトウェア設計

64180CPUをコアとしたASEは、64180のシリーズ展開に同期し、64180R<sub>0</sub>、 $R_1$ 、Z、X、Sと開発し、今回新たにASIC用 ASEを開発した。ASE制御用ソフトウェアは、64180系CPUの展開に同期して機能向上を行ってきた。今回のASIC用ソフトウェアは、このソフトウェアをベースに、ASIC用機能を取り込み開発した。

機能としては、ユーザープログラムの実行、ブレーク、トレースをメインとし、シングルステップ実行、メモリ・レジスタの表示変更、アセンブル・逆アセンブル、ホストシステムとのプログラム転送、カバレジトレース、シンボリックデバッグ機能などを持っている。ASIC用機能は、このなかの周辺機能情報の設定・変更コマンドである。

#### 4.1 周辺機能情報の設定・表示

## 4.1.1 コマンド機能

ASIC用ASEでは、ASE起動時、内部メモリ構成、MMU (Memory Management Unit)、DMAC、リフレッシュコントローラ、ASCIなどをユーザーが設定できるようにする。設定できる内容を以下に述べる。

- (1) MPU(Micro Processing Unit)モード シングルチップモード,拡張モードを選択する。

- (2) 内蔵メモリ

内蔵させるROM, RAM, EEPROMのアドレス範囲を指定する。

#### (3) DMAC

ASEは4チャネル分のDMACを内蔵しており、その使用の 要否とDMAC内蔵のアドレスマップを設定する。

- (4) リフレッシュコントローラ

- リフレッシュコントローラ使用の要否と内蔵のアドレスマップを設定する。

- (5) I/Oポート

8ビット単位で3ポートまで選択する。また,内蔵のアドレスマップを設定する。

(6) 周辺エバセルチップ

タイマ, ASCI, CSCI(Clocked Serial Communication Interface) などの周辺エバセルチップを用意してあり、ユーザ

ーがASEに自由に実装できる。この場合、実装した周辺エバセルチップの内蔵のアドレスマップを設定する。

以上がコマンドで設定する情報であり、この設定によりユーザーが目的とするASICチップと同じ機能をASEで構築でき、デバッグ可能となる。

これら情報は設定後も自由に変更可能であり、設定情報は ASEホストシステムへの表示も可能である。

また、これら情報はASE本体のシステムディスクに書き込んでいるため、一度設定した情報は再設定されるまで保持できる。

## 4.1.2 可変機能のサポート

ユーザー指定によって変化する周辺機能のエミュレーションをサポートするために、論理としては周辺機能の各種組み合わせに対応できるように作成してある。そして、変化する周辺機能情報をテーブルとし、各コマンドはこのテーブルを参照しながら不当な入力をチェックし、不要な情報の表示を禁止している。例えば、実装メモリ範囲を越えるアドレス入力があるとエラーとし、DMAを使用していない場合は、トレース情報からその部分を削除して表示することを行っている。以上、ソフトウェアとしては周辺機能情報の設定・表示コマンドを設けることにより、ASIC用ASEを実現している。

# 5 結 言

ASIC用ASEの設定方針、ハードウェア構成と動作、ソフトウェア構成と動作について述べた。ASEは開発支援ツールであり、実際の製品デバイス完成以前に提供しなければならない。また、顧客の開発投資の低減および開発期間の短縮に効果のあるものでなければならない。今回開発したASEは、SBPバスの採用によって機能モジュールの追加、交換が可能な方式とし、これら当初の目標を達成した。今後、ASICチップの高機能化、高性能化が予想されるが、ASEも製品チップに同期して機能、性能の向上を図らねばならないが、この対応策として、

- (1) CPUコアと周辺機能モジュールを取り込んだ評価チップ 搭載のASE

- (2) 製品チップにASE機能を取り込んでおき、実際の製品チップを搭載したASE(ASE On Silicon)が考えられる。また、ソフトウェアツールとして、より高速動作可能なシミュレータも必要になってくると考える。

#### 参考文献

- 日経マイクロデバイス: CPUコアASIC時代が幕開け、No.43、 60~65(平1-1)

- 2) 日立製作所データシート:日立マイクロコンピュータサポート システム, 163~197(平1-2)

- 3) 小林,外:セルベースIC「HG52シリーズ」,日立評論,71,12,1223~1230(平1-12)