# エレクトロニクス

半導体分野でのトピックスは、日立製作所の総力をあげて開発してきた、マルチメディアの世界を担う新型RISCマイコン "Super H RISC engine™—SHシリーズ"の商品化に成功したことである。この新型マイコンの周辺に用いられる画像用メモリや、アナログ回路を搭載可能としたセルベースICをラインアップにそろえた。これらのチップセットは、パーソナル携帯機器、アミューズメント、自動車用ナビゲーション機器など広い用途に用いることができる。

ディスプレイデバイスでは、超薄型のワイドカラーブラウン管や省電力を特徴とするカラーディスプレイ管に加えて、TFT (薄膜トランジスタ)と液晶を一体化した、ノート型パソコン用のカラー液晶モジュールを製品化した。

電子デバイス製造装置では、日立製作所の特徴技術である電子線技術を発展させて、高スループットの電子ビーム描画装置や、世界で初めてミクロな深穴を観察できる装置「ミラクルアイ™」を製品化した。

# マルチメディア対応画像用メモリの充実

マルチメディアのさまざまな画像処理に対応するため、シンクロナスメモリ、フレームメモリ、ビデオRAMの高速品を製品化し、画像用メモリを充実させた。

今後成長が期待されるマルチメディア分野では、画像処理がますます重要になり、大型、高性能化する画像表示や画像圧縮技術に対応可能な、高速でコストパフォーマンスの良いメモリへの要求が強くなっている。こうした顧客の要求に対応するため、画像用メモリ製品系列の拡充を図っている。

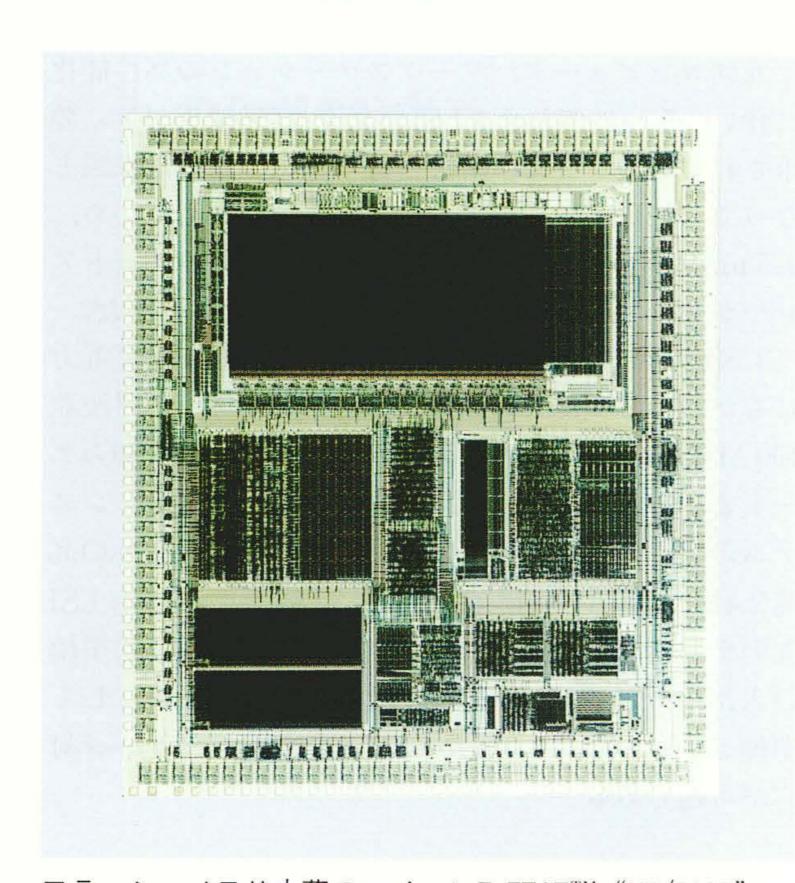

#### (1) シンクロナスメモリ

最新の0.8 µm/0.5 µmプロセスを使用し、パイプライン回路方式によってメモリ制御を行い、高データスループットを図ったシンクロナスDRAMを実現した。2 M品は比較的小型の画像処理に、4 M品は今後主流となるミッドレンジの画像処理に、また16 M品は大容量で高速な画像処理にそれぞれ適している。チップサイズはVRAMに比較して対メモリ容量比で小さくでき、電源電圧が3.3 Vのため低消費電力となったことにより、コストパフォーマンスの良い製品となった。

8 MSGRAMはシンクロナスDRAMにブロックライトとI/Oマスク機能を付加し、描画性能の向上を図っ

たものである。また、ビット構成は×32のため転送レートが大きくなっている。

#### (2) フレームメモリ

2.5 Mフレームメモリは、READ/WRITE非同期の 大容量FIFOであり、テレビ、VTRばかりでなく、さま ざまな画像処理でのバッファメモリとして使用でき る。マルチデータパス方式によってメモリ制御を行 い、高速サイクルを実現した。

#### (3) ビデオRAM(VRAM)

最新の0.8 µmプロセスとハイパーページ機能によって高速サイクルを実現している。ビデオRAMはデュアルポートのため、描画と表示が同時にできるので使いやすく、今後とも多くの画像処理に使用できる。

画像処理のアプリケーションは、今後さらに進展し、高度化していくことが予想されるので、これに対応していくためには、例えば100 MHz以上の高速動作が必要となる。今後この点に着目し、画像用メモリの展開を図っていく考えである。

画像用メモリ

| メモリ方式     | 品 種       | 構成                                              | 電源電圧  | サイクルタイム           | パッケージ         |

|-----------|-----------|-------------------------------------------------|-------|-------------------|---------------|

| ビデオRAM    | 2 MVRAM   | 256 k× 8 / 128 k× 16                            | 5.0 V | tPC = 30/35  ns   | SOJ/TSOP/SSOP |

| フレームメモリ   | 2.5 Mフレーム | 330 k× 8                                        | 5.0 V | tCC = 20/25 ns    | TSOP          |

| シンクロナスメモリ | 2 MSDRAM  | $64\mathrm{k}	imes 16	imes 2$ bank              | 3.3 V | tCK = 15/17.5  ns | TSOP          |

|           | 4 MSDRAM  | 128 k $\times$ 16 $\times$ 2 bank               | 3.3 V | tCK = 15/17.5  ns | TSOP          |

|           | 8 MSGRAM  | 128 k $	imes$ 32 $	imes$ 2 bank                 | 3.3 V | tCK = 10/12 ns    | QFP           |

|           | 16 MSDRAM | $512  \text{k} \times 16 \times 2  \text{bank}$ | 3.3 V | tCK=10/12 ns      | TSOP          |

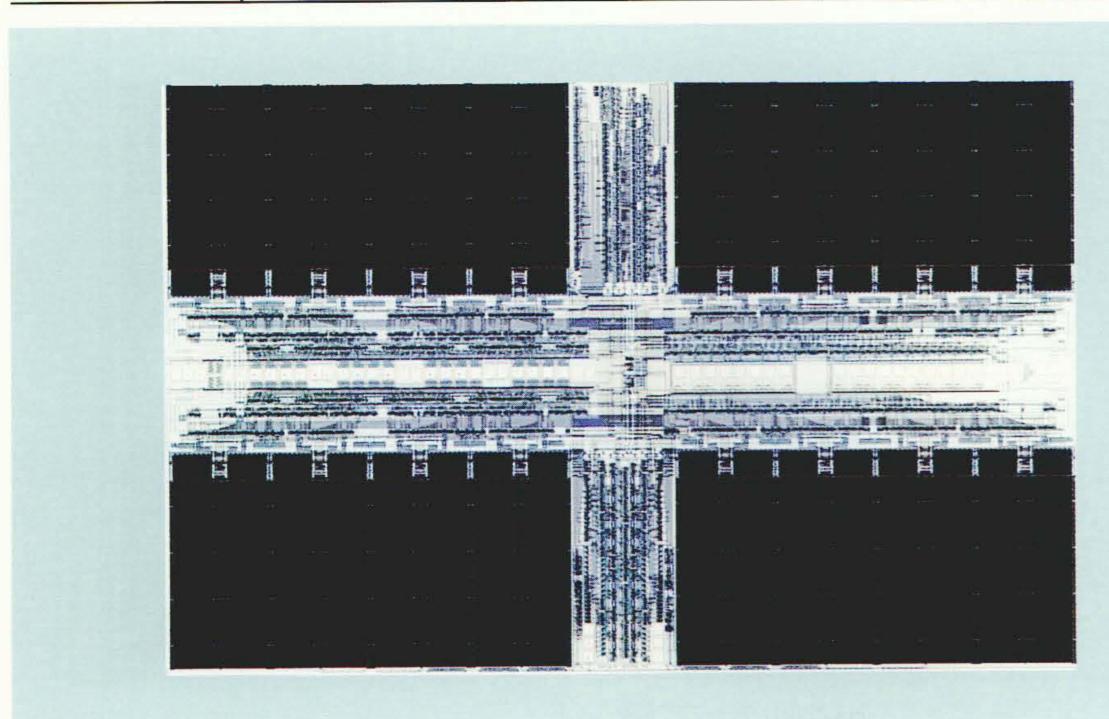

4 Mシンクロナス DRAMのチップ

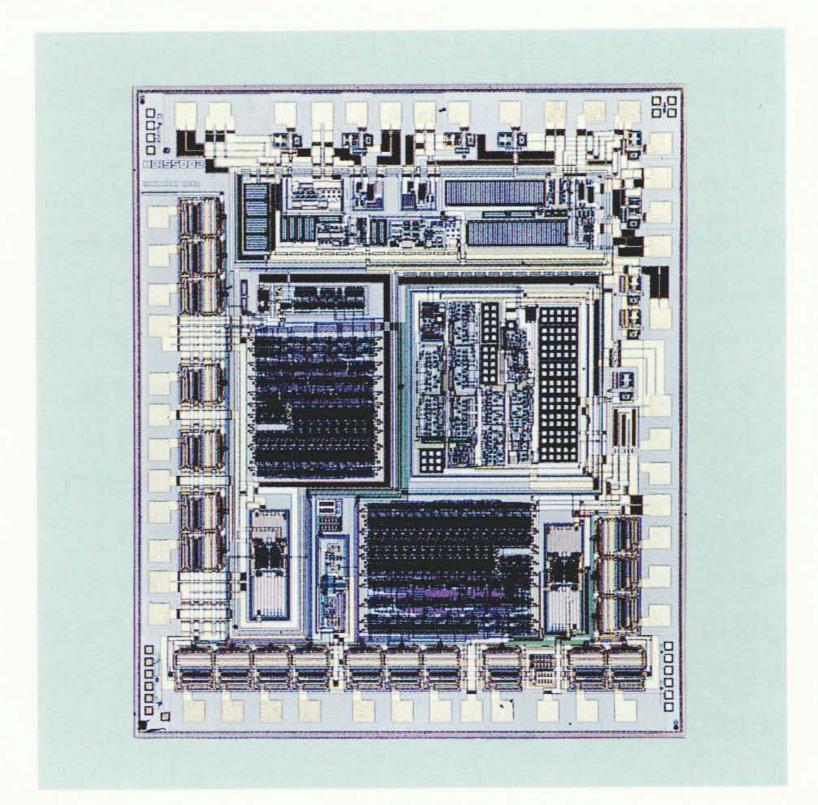

# 移動体通信受信用ガリウム・ひ素IC

自動車電話など移動体端末の小型化・高性能化に対応するため、整合回路外付けタイプで、0.1~2 GHzで動作可能な受信用ガリウム・ひ素ICを開発し、量産している。

自動車電話に代表される移動体通信機の高周波回路は1~2 GHzで動作し、その性能がセットの性能を左右する。携帯電話の普及に伴って端末の小型化、高性能化とともに通話および待ち受け時間確保のため、低消費電力化の動向にある。

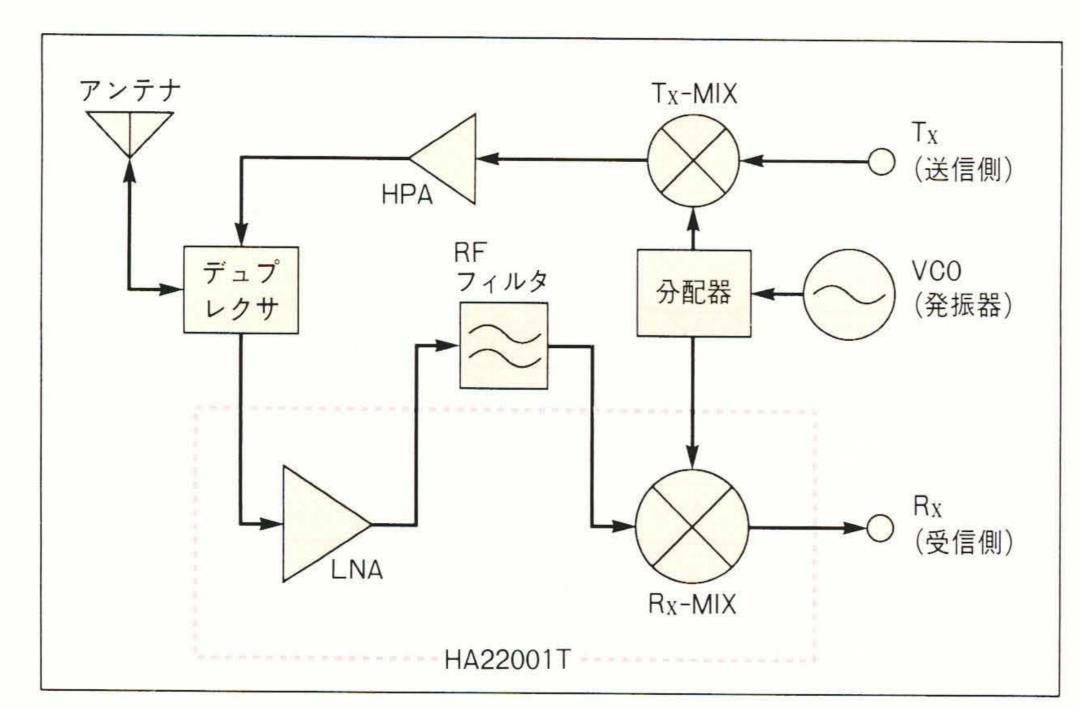

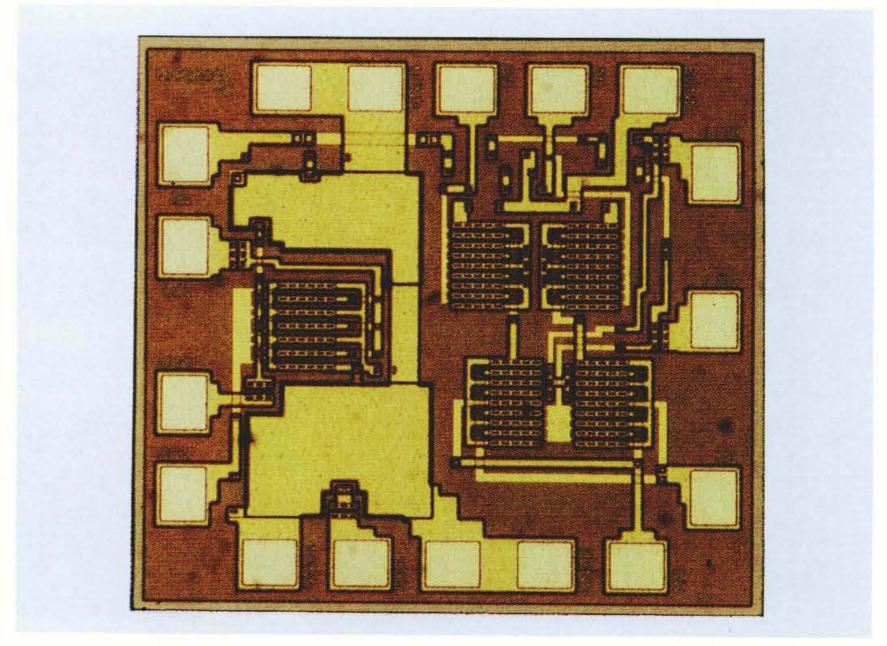

このような要求にこたえるため、低雑音増幅器 (LNA)と受信用ミクサ(Rx-MIX)を1チップに集積した5 V動作移動体通信受信用ガリウム・ひ素IC "HA22001T"を開発し、量産中である。

ガリウム・ひ素FET (Field Effect Transistor) は周波数特性,雑音特性,ひずみ特性に優れ,高周波増幅回路,周波数変換回路に最適なデバイスである。あわせて信号漏洩(えい)特性を考慮した回路構成を採用し,低電流で特性を損なわないように回路定数の最適化を

行った。

LNAでは低雑音化重視の内蔵バイアス回路の最適化を行った。消費電流2.4 mA,960 MHzで雑音指数は1.7 dB,電力利得は16 dBを実現した。

Rx-MIXはひずみ性能とアイソレーション特性を重視し、IC化に適したダブルバランス型ミクサを採用した。消費電流5.4 mA、960 MHzで変換利得10 dB、雑音指数 7 dB、三次相互変調ひずみ55 dBを実現した。パッケージは薄型(1.1 mm)でピンピッチ0.65 mmの小型面実装タイプ "TSSOP14"を採用し、機器の小型化に対応している。

このICは整合回路外付けタイプであり、これを変更することにより、144 MHz帯の用途から2 GHzの周波数まで動作が可能である。

注:略語説明 LNA(Low Noise Amplifier) Rx-MIX(Receiver Mixer) Tx-MIX(Transmitter Mixer) VCO(Voltage Controlled Oscillator) HPA(High Power Amplifier)

移動体通信高周波部システムブロック図

外形

HA22001チップ外観

# 64 MビットDRAMの開発

#### 最先端の0.3μmプロセスを適用して、低電圧で高速な64 MビットDRAMを開発した。

近年、DRAMは、搭載される機器の多様化、高機能化および低消費電力化が進む中で、高集積、高速および低電圧化の要求がますます強まっている。こうした顧客の要求にこたえるために、低電圧動作で高速な64 MビットDRAMを開発した。

最先端0.3 μm微細加工CMOSプロセスを用い、メモリセルは 4 MビットDRAMで業界初の実用化に成功したSTC(Stacked Capacitor Cell)をベースに、さらに改良を加えた。

電源電圧は3.3 V,入出力インタフェースは低振幅で高速のLVTTLとし、アクセスタイム60 nsを実現し、高速CPUのメインメモリ、画像用メモリなどへの高速化対応を可能にした。また、システムのデータバス幅に対応した幅広いビット構成展開(×4,×8,×16ビット構成)を図るとともに、多様なパッケージ展開(SOJ、TSOP)が可能である。

64 Mビット DRAM

| 項目      | 内 容<br>0.3 μm CMOS<br>× 4 /× 8 /× 16                                       |  |  |

|---------|----------------------------------------------------------------------------|--|--|

| プロセス    |                                                                            |  |  |

| ビット構成   |                                                                            |  |  |

| パッケージ   | × 4 /× 8 : SOJ, TSOP II<br>32ピン 500ミル<br>× 16 : SOJ, TSOP II<br>50ピン 500ミル |  |  |

| 機能      | 高速ページ                                                                      |  |  |

| アクセス時間  | 60/70 ns                                                                   |  |  |

| インタフェース | LV-TTL                                                                     |  |  |

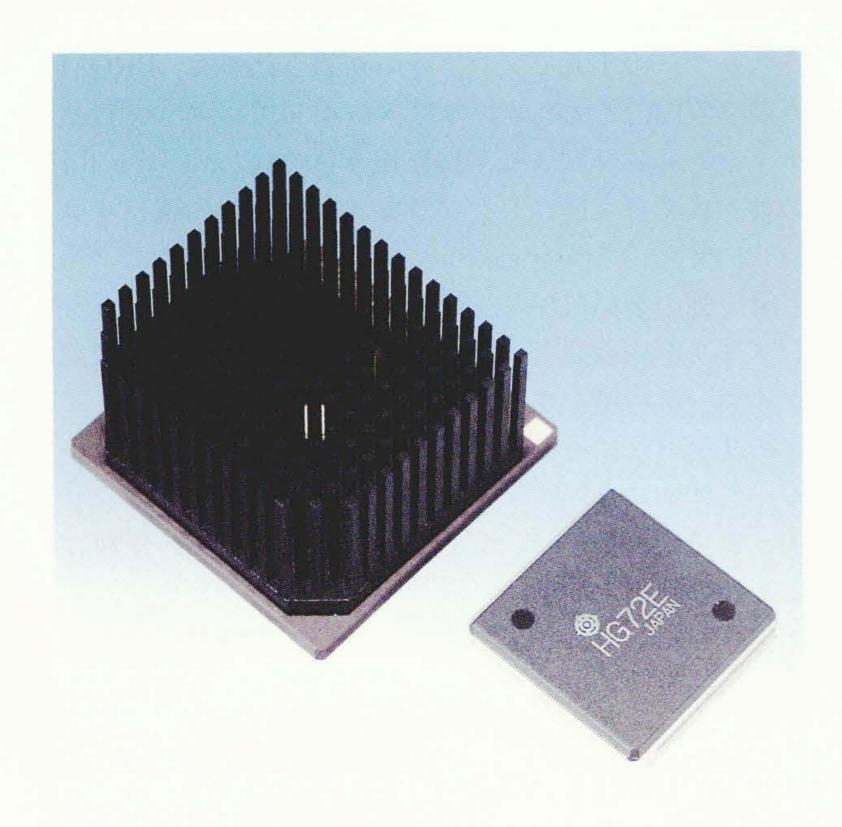

## 超高速動作CMOSゲートアレー

先端0.5μmプロセスを用いて,100 MHzの高速動作が可能な,最大50万ゲートのCMOSゲートアレーを製品化した。

HG72G/Eシリーズ

並列コンピュータ、ワークステーションの高性能化に伴い、それに使われるLSIの高速・高集積化が強く要求されている。また、消費電力の低減も重要な課題となってきている。このようなニーズにこたえるため、0.5 μmプロセスを用い、3.3 V動作のCMOSゲートアレーシリーズ「HG72G/Eシリーズ」を製品化した。

3.3 Vの低電圧動作のため、従来の40%の消費電力にもかかわらず、ゲート速度200 ps、クロック周波数100 MHzの高速動作が可能である。また、最大50万ゲートまでの大規模LSIが設計可能である。さらに、システムの高速化に対応するため、サイクル時間4 nsの高速RAMや100 MHz動作のPLLも搭載できる。他にLSI間のデータ伝送速度を高速化するため最新の低振幅の入出力インタフェース(GTL)もライブラリとして準備している。また、最大600ピンまでのパッケージ対応が可能である。

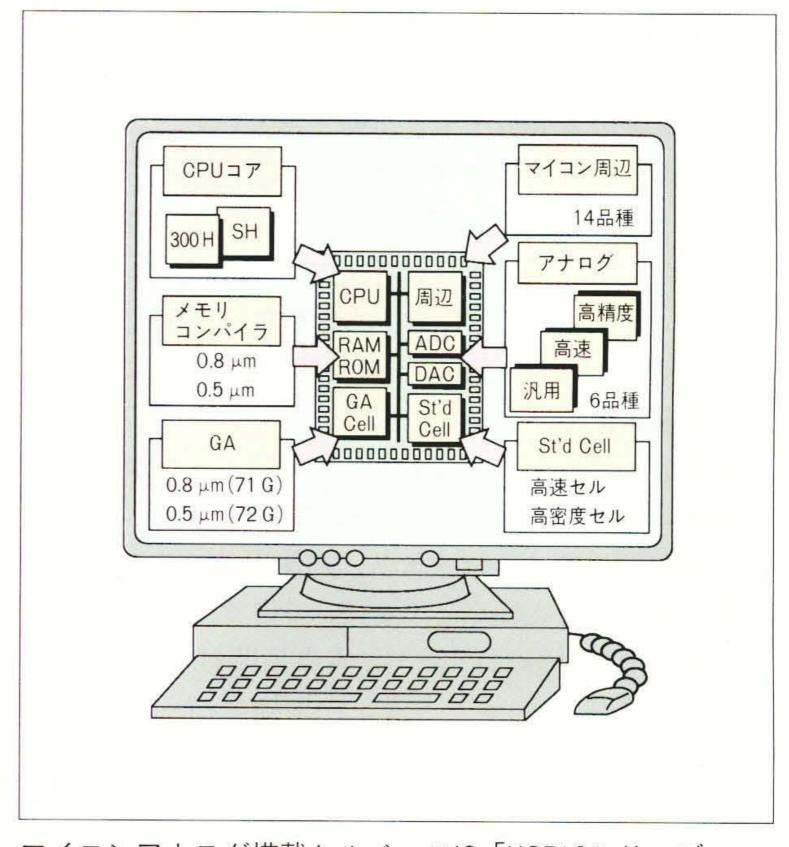

## システムオンチップを容易に実現するセルベースIC

高性能16ビットマイコンH8/300HシリーズのCPUコア、AD・DAコンバータなどを搭載できるセルベースIC「HG71Cシリーズ」を製品化した。

移動体電話のような小型機器のためのシステムオンチップ化を実現するために、高性能16ビットマイコンH8/300HシリーズのCPUコア、高性能AD・DA変換器、サイズ可変のROM・RAMコンパイラ、高密度・高速タイプのスタンダードセルなどを0.8 μm CMOS用にライブラリ化した。これらのライブラリを自由に組み合わせることにより、カスタムマイコンまたはマイコン、アナログ搭載のセルベースICが実現できる。

一方、このようなセルベースICを短期間で実現するために、カスタムマイコンに搭載するモジュールの組み合わせを最適化するためのマイコンコンパイラ、マイコンモジュール・ユーザー回路のテスト設計の自動化、および設計仕損を低減するための高精度シミュレーション技術などを実現した。これらを、エンジニアリングワークステーション上に搭載したASIC設計ツールで可能とし、マイコンとアナログを含むセルベースICをワークステーション上で一貫設計できるようにした。

マイコンアナログ搭載セルベースIC「HG71Cシリーズ」

## フラッシュメモリ内蔵のマイコン

オンボードでの内蔵プログラムおよびデータの書き換えニーズに対応したフラッシュメモリ内蔵のマイコンを開発した。現在、シリーズの展開を進めている。

フラッシュメモリ内蔵のマイコンF-ZTAT™ "H8/538F"

ユーザーの手元でプログラムが書き込める, PROM 内蔵のZTAT®マイコンのフィールドプログラマビリティをさらに発展させ、機器組み込み後(オンボード) の書き換えを可能にしたフラッシュメモリ内蔵マイコン "F-ZTAT"™ (Flexible-ZTAT)を開発した。

第一弾の製品"H8/538F"は、60 kバイトのフラッシュメモリを内蔵した産業、OA分野向けであり、高機能タイマーを特徴とする。開発は4 Mビットフラッシュメモリをベースとし、マイコン用に最適化を図っている。具体的には、

- (1) 容量128バイトから8kバイトのブロック分割に よる使い勝手の向上

- (2) 内部昇圧回路による低電圧動作(2.7 V動作)の実現

- (3) 他のロジック、アナログモジュールとの整合などがあげられる。

H8/538Fに続き、H8/3434F(32 kバイト)、H8/3048 F(128 kバイト)とF-ZTAT™ファミリーの拡充を図っている。今後さらにSHシリーズへの展開も計画している。

# Bi-CMOS技術による高速アナログ・ディジタル混在LSI

微細化されたBi-CMOS技術を使ってハードディスク用信号処理LSI,移動体通信用PLLシンセサイザICを製品化した。

Bi-CMOS技術を用いて、高速、高精度なアナログ回路をディジタルチップへ搭載し、製品化を行ってきた。今回、より微細化された0.7 μmBi-CMOS製品を2系列開発し量産に入った。

- (1) ハードディスク用高速信号処理LSI 転送レート90 Mビット/sを実現 内部最高動クロック=140 MHz 最大アナログ周波数=135 MHz

- (2) 移動体無線用PLLシンセサイザIC 最高動作周波数=1.8 GHz 消費電力=18 mW

このほかにもBi-CMOS適用製品としてD-MOSオンチップパワーICなどがあり、低電力、高速化、さらには小型化のためのオールインワンチップの技術を持って、顧客のニーズにこたえていく。

高速アナログ・ディジタル混在LSI

# 高耐圧・大電流ゲートターンオフサイリスタ

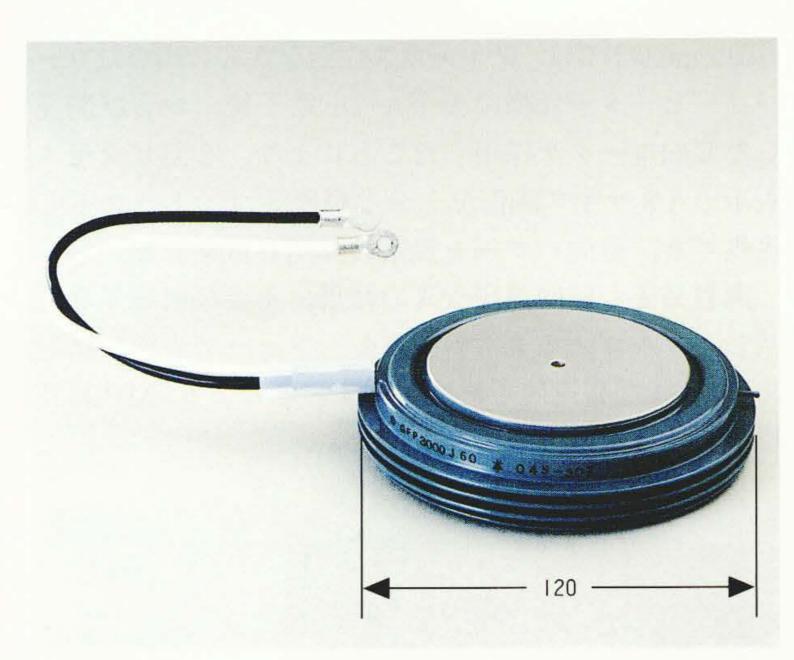

耐電圧6 kV, 可制御電流3 kAのGTOを開発した。ユニットのエミッタ幅を微細化することにより、スナバコンデンサ容量3 μFで3 kA遮断を達成した。

開発した 6 kV 3 kA GTO

電力系統の安定度向上のため、高機能を持つ大容量自励式変換器のニーズが高まっている。これには高耐圧大電流で低損失のGTO(ゲートターンオフサイリスタ)が最適である。このため、耐電圧 6 kV、可制御電流3 kAのGTOを開発した。

GTOは短冊状のユニットが多数個並列に配置されたパターンを持つ。このユニットのエミッタ幅を微細化したことにより、電流遮断耐量を向上させた。その結果、スナバコンデンサ容量 3 µF (従来比50%)で3kAの電流遮断を達成し、スナバ損失の低減を可能にした。さらにシリコンウェーハと熱緩衝板を合金化しないパッケージング技術を確立し、従来の合金型GTOと同等の信頼性を確保した。それとともに、ウェーハ内の不純物濃度分布を改善することによってGTOの電力損失を低減し、高耐圧大容量化に伴う損失の増加を抑えることができた。

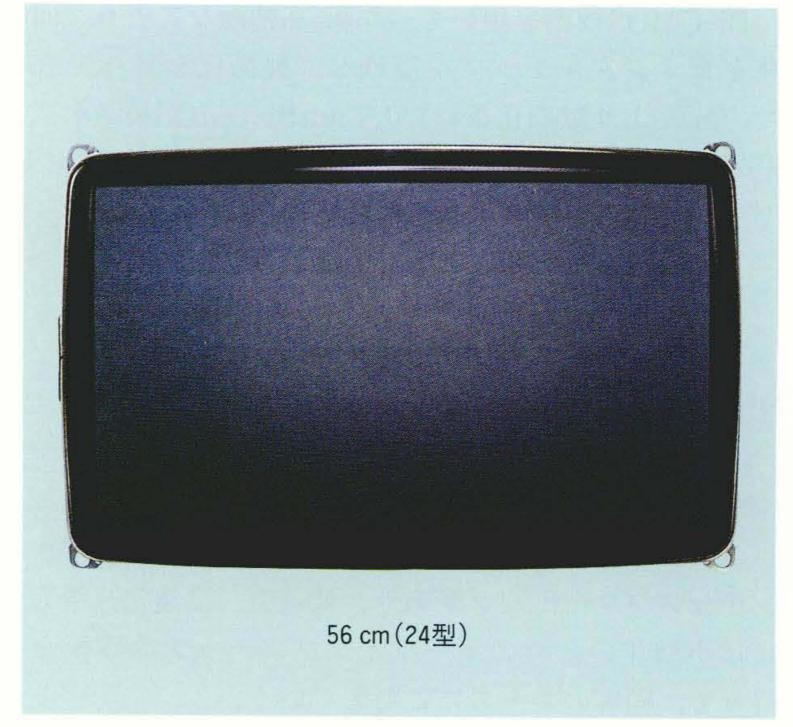

## 56 cm(24型)ワイドカラーブラウン管

パーソナルユースを目的としたワイドカラーテレビ用として,低価格で高性能な56 cm(24型)ワイドカラーブラウン管を開発した。

近年のカラーテレビはワイドテレビが主流になりつつあるが、高価格のため一般家庭には完全に普及しきれていないのが現状である。今回、従来のカラーブラウン管と同等の性能を低価格で実現し、76 cm、66 cmのシリーズ化として56 cmワイドカラーブラウン管を製品化した。

パネルはフラットフェース曲面を採用し、コントラストの向上と黒の再現性を良くするため、ダークティントパネルを採用した。低価格というコンセプトに対応してシャドウマスクは通常の鉄板(アルミキルド材)を使用した。課題のドーミング特性は、高次バリアブルピッチシャドウマスク、および低偏向角ファンネルを採用したことによって解決した。また、バルブ全長を最大424.2 mmとして、テレビセットの奥行きを45 cm(家具の平均的な奥行き)以下に設計することを可能とした。

ワイドカラーブラウン管

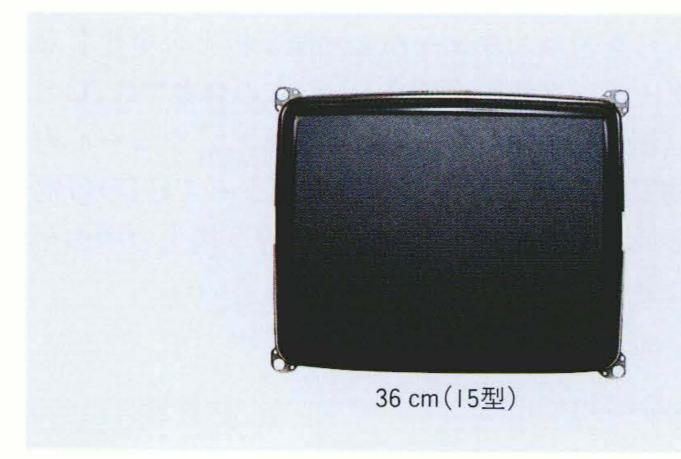

# 省電力対応の高画質カラーディスプレイ管

パソコンやワークステーションの低消費電力化に対応した高画質36 cm(15型),および51 cm(21型)のカラーディスプレイ管を開発した。

ディスプレイ用モニタの高画質化に加え,低消費電力化の必要性が高まってきている。この要求にこたえるため,ヒーターパワーを従来の約50%に低減した低消費電力化対応のCDT(カラーディスプレイ管)を開発した。

36 cmCDTでは、開発したNEAT (Narrow Elliptical Aperture Technology) 電子銃の採用により、画質性能を改善した細ネック化を実現し、偏向パワーを従来の約70%にまで低減した。

51 cmCDTでは、フォーカス性能をさらに高めたローパワーヒーター仕様のA-EA-DF電子銃、および開発した偏向ヨークを採用したことにより、2 Mピクセル表示のA 3 サイズ画面を十分な輝度とコントラストで提供でき、偏向パワーを従来の90%に低減した。

両製品とも偏向感度改善の結果,不要輻射磁界を低減し,エルゴノミクスの観点からフェース表面に反射防止,および帯電防止処理を施すことにより,MPR-II 規格に適合するものとした。

51 cm (21型)

カラーディスプレイ管

## 26万色, 10.4型TFT液晶モジュール

ノート型パソコンに搭載可能な外形で,対角26 cmの大画面,26万色同時表示,3 W以下の低消費電力タイプの TFT液晶モジュールを開発した。

TFT液晶モジュールは、薄型、軽量、低消費電力という特長を生かして、携帯に便利なノート型パソコンへの適用が急速に広まっている。

今回, さらに性能向上を図り, 大画面, 26万色同時表示, 低消費電力のTFT液晶モジュールを開発した。 主な特徴は次のとおりである。

- (1) ノート型パソコンに搭載できるように、外形寸法 を横264(実効252)×縦180×厚さ10(mm)とした。

- (2) 画面対角寸法を26 cm(10.4型)に大画面化した。

- (3) バッテリ動作で長時間使用できるように、消費電力を3W以下に低減した。

- (4) 26万色同時表示が可能なので、マルチメディアにも対応でき、自然な画質が得られる。

- (5) 5 V単一電源で動作できるので、システムへの実 装が容易である。

26万色, 10.4型TFT液晶モジュール

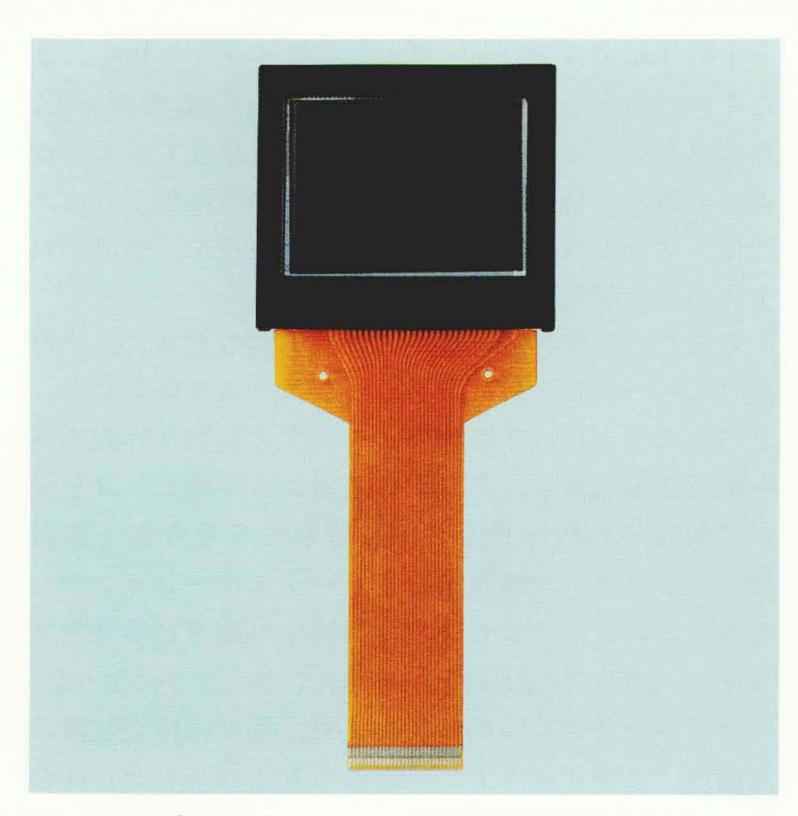

## 1.4型,34万ドットpoly-SiTFT液晶モジュール

半導体とTFT技術を応用し、小型・高精細で駆動ドライバを内蔵することを特徴とする"poly-SiTFT"を開発した。

poly-SiTFT液晶モジュール

将来のマルチメディア機器の情報表示用ディスプレイ、またはバーチャルリアリティ技術に必須のヘッドマウントディスプレイの表示素子として、小型で高精細な映像表示素子の実現が望まれている。

今回、このような用途に最適な対角1.4型(3.6 cm)で、34万ドットの高精細映像を表示することができるpoly-SiTFTを開発した。poly-SiTFTは半導体の回路集積化技術と微細加工技術を利用し、これとTFT液晶技術を融合することにより、小型高精細ディスプレイを実現するものである。主な特長は次のとおりである。

(1) 横720×縦480ドットの高精細画面, (2) NTSC方式の自然画をそのまま表示するフルカラー表示, (3) 駆動ドライバを内蔵するとともにインタレース走査機能を付加して周辺回路を簡略化, (4) 光学設計が容易,

(5) 重さ5グラムの軽量パッケージを採用

## 電子デバイス製造装置

半導体メモリは16 Mビットの量産が本格化し、64 Mビットの時代が到来しつつある。一方、液晶デバイスは生産性の向上が課題であり、これにこたえて各種製造・評価・検査装置を取りそろえている。

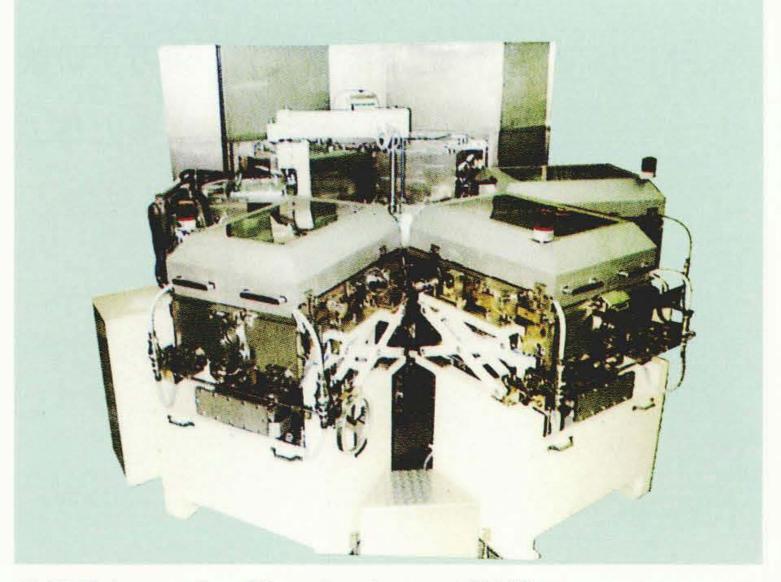

### 新型マイクロ波プラズマエッチング装置

64メガ以降のデバイスに対応する、新型マイクロ波プラズマエッチング装置「M-500シリーズ」を開発した。この装置はマルチチャンバ方式を採用しており、多層膜の連続エッチングが新たに可能となった。エッチングチャンバには、マイクロ波のプラズマ転換効率を増大させた導波管と、アルミニウム製のリアクタを開発して搭載した。このため、従来の2倍のイオン電流をウェーハ面上で均一に得ることが可能となり、エッチングプロセスの基本性能を向上させた。

システム的には、(1) ウェーハオリフラ・センタリングユニット、ダミーウェーハ専用カセットを標準装備したローダの採用、(2) 従来比 3 倍の高速排気特性、(3) 静電吸着・クランプレス電極の採用、(4) 高速ハンドリング機構の採用、(5) 高性能 2 軸真空ロボットの採用など、従来にない優れた機能を持っている。

エッチング性能はもちろんのこと、低発塵化、高信 頼性および高スループット化をさらに一歩進めて実現 可能とした、FA、CIM対応の量産装置である。

新型マイクロ波プラズマエッチング装置「M-500シリーズ」

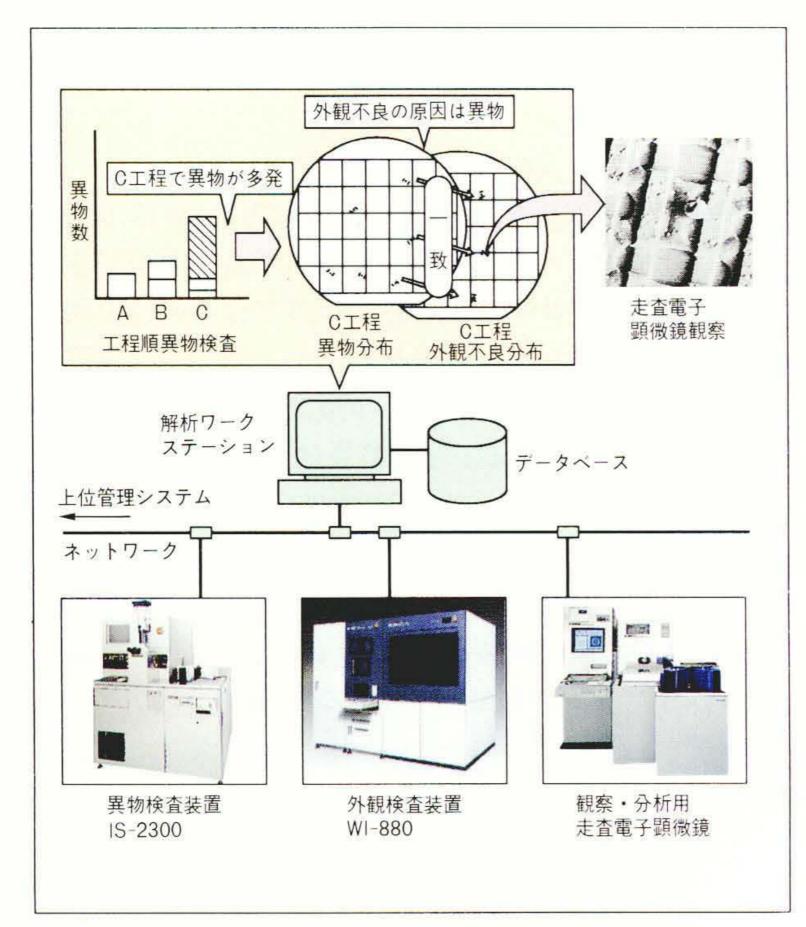

#### ウェーハ異物・外観統合解析システム

ウェーハ異物・外観統合解析システムの構成

半導体産業は微細化・製品化のサイクルが短く、またそれに対応した設備投資も膨大である。したがって、新製品をいかに早く、高歩留りで安定量産できるかが重要である。特にサブミクロン以下の微細加工では、設備、プロセスからの異物や外観の不良が、製品不良全体の約8割を占めている。

そのため、異物と外観不良低減を図るために、半導体ウェーハ異物・外観統合解析システムを開発した。このシステムは、半導体ウェーハ上の異物や外観不良を検査する装置と、それらの装置から座標データを受けて異物や外観不良を詳細に観察する走査電子顕微鏡、およびデータ解析を行うワークステーションからなる。このシステムにより、異物や外観不良の発生プロセス、設備の特定、対策が早期にできるようになった。

クォータミクロンの時代に入り、個々の検査装置の 高精度、高速化とともに、それらを組み合わせた統合 解析システムの役割がますます大きくなる。

今後も新たなシステムの開発に取り組んでいく考え である。

### 電子ビーム描画装置

電子ビーム描画装置"HL-800D"は、一括図形描画、連続移動描画などの新しい技術を導入することにより、 高精度と高スループットの両立を実現したものである。

一括図形描画は、繰り返し用いられる図形をマスクからウェーハ上に転写描画する技術である。また、描画時に試料台を常時移動させる連続移動描画により、描画時間の短縮を図っている。これらの技術導入により、0.3 μmデバイス用ウェーハを20枚/hのスループットで描画する能力を持ち、先端デバイス、ASICなどの開発から生産までの広範囲にわたって適用できる。

電子ビーム描画装置 "HL-800D"

## 高スループット縦型拡散CVD装置

最新の高スループット縦型拡散CVD装置 "VER-TEX-III(F)" を開発した。

この装置の特長は、(1)全自動化対応の設計、(2)シミュレーションに基づいたロングヒータ採用による均熱長の増加、(3)ウェーハチャージのピッチの縮小、(4)ウェーハの移載動作とカセット搬送動作の同時実行による搬送時間の短縮などである。

以上の技術により、1バッチの処理枚数を従来の100 枚から150枚(8インチ)に増加し、かつウェーハ移載時間を23分から14分に短縮した。

(国際電気株式会社)

## 高コストパフォーマンスアッシング装置

半導体用設備の投資が肥大化するなか,半導体製造装置で性能,価格,ランニングコストなどあらゆる面でコストパフォーマンスの向上が要求されている。

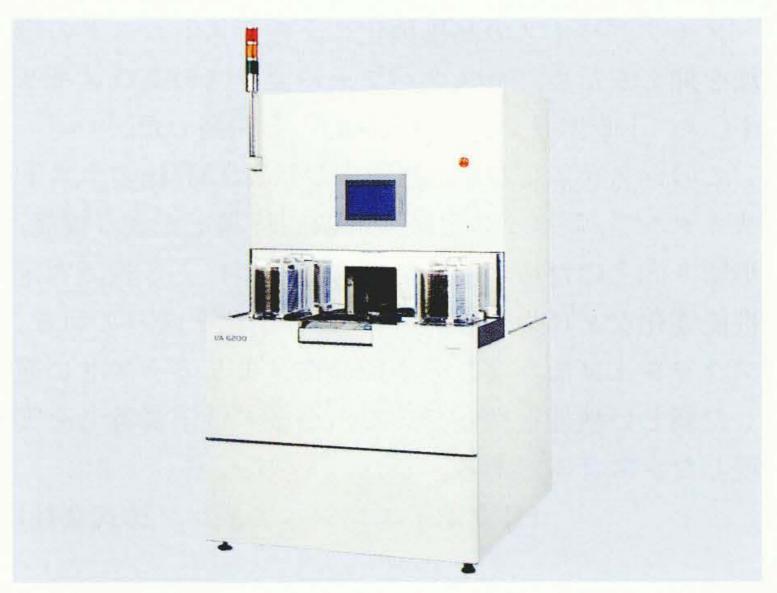

そのため,64 MDRAM以降のデバイスに適合した 枚葉式アッシング装置"UA-6200"を開発した。特長 は次のとおりである。

- (1) 高性能: スループット=60枚/h,

- $\nu$ ート=2  $\mu$ m/min,均一性=±7%

- (2) 低汚染:ウェーハ裏面付着異物数=100個以下

- (3) 低ダメージ:チャージアップなし

- (4) 低ランニングコスト:当社比55%に低減

アッシング装置 "UA-6200"

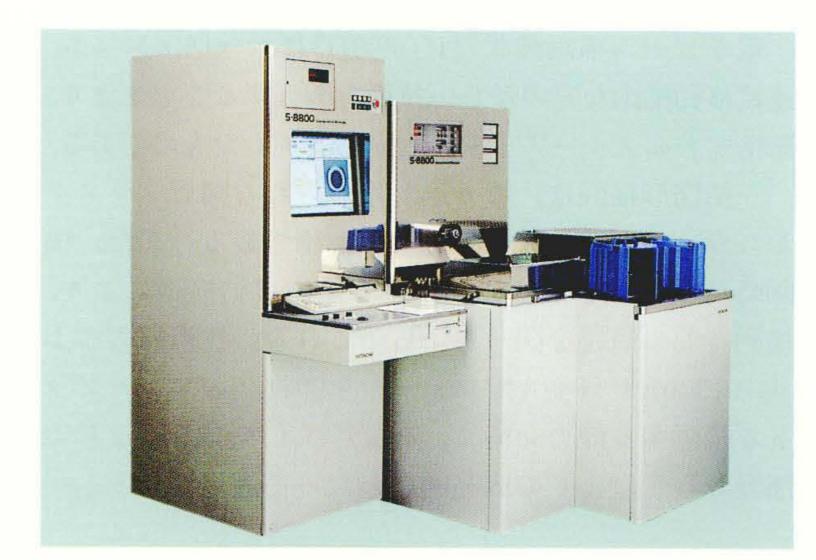

### 高分解能電子線測長装置

半導体プロセスでの微細加工パターンの形状観察, 寸法計測によるプロセス管理装置として電子線測長装置「S-8000シリーズ」を開発した。

この装置の特長は、(1) 2次電子分解能が 5 nm、(2) 測長再現性が0.005 μm (3 σ)、(3) スループットが20ウェーハ/h(連続モード)、(4) グラフィカルユーザーインタフェースカラーモニタ画面による操作性の向上、(5) パターン認識による自動測定機能の向上などである。この装置は、従来機種S-6000Hシリーズと比較して約 2 倍のスループットが得られる。

高分解能電子線測長装置「S-8000シリーズ」

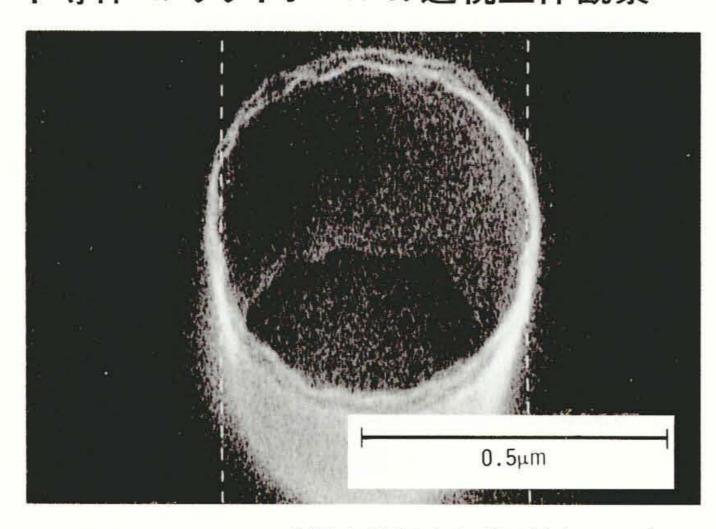

### 半導体コンタクトホールの透視立体観察

コンタクトホールの透視立体観察例(傾斜角:10°) (この観察だけで寸法,異物,形状などの管理が可能)

多数の複雑な工程からなる半導体プロセスでは,一つの工程の加工不良が完成デバイスの致命的な不良になる。そこで,各工程でデバイスの加工状況を詳細に観察して次の工程に進めている。

ミラクルアイ "HM-2000" は、物質を透過する能力の高い200 kVの高エネルギー電子を用いた走査電子顕微鏡であり、これによってこれまで不可能であったコンタクトホールの透視立体観察ができる。ホールの加工状況を三次元的に管理できることから、最先端デバイスの開発や量産プロセスでの歩留り改善に役立つものと期待できる。

#### ウェーハテスト工程におけるメモリICテストシステム

メモリデバイスの高集積化によるテストコストの増加を抑えるため、コストパフォーマンスの高いメモリICテストシステム"HA5060Q"を開発した。

このシステムでは60 MHzまたは120 MHzのテストサイクルで、デバイスを最大32個同時測定できる機能、歩留り向上のための同時処理方式採用による救済判定機能強化などにより、高スループット化を図っている。フラッシュメモリなどの不揮発性メモリのテストに適した新しい機能を持っている、小型・低消費電力を実現したシステムである。

(日立電子エンジニアリング株式会社)

メモリICテストシステム"HA5060Q"

### ウェーハ昇温脱離ガス分析装置

半導体デバイスの高集積化に伴い,ウェーハの表面 解析が重要になっている。そのため,高感度な昇温脱 離ガス分析装置を開発した。

この装置は、大気圧イオン化質量分析装置とガス脱離装置で構成し、ウェーハは800  $^{\circ}$   $^{\circ}$   $^{\circ}$  まで加熱することができる。また、半導体プロセスでの洗浄評価、各種薄膜評価およびエッチング処理の評価などに適用でき、極微量水分、有機物およびハロゲン物質の分析ができる。ウェーハサイズは8 インチまで対応可能で、片面分離測定ができる。

(日立東京エレクトロニクス株式会社)

ウェーハ昇温脱離ガス分析装置

### 大型LCD用プロキシミティ露光装置

大型LCD用プロキシミティ露光装置 "LE-4050A"

LCD(液晶ディスプレイ)は薄型軽量・低消費電力で、カラーテレビやOA機器用のディスプレイとして利用されている。このLCDパネルの製造装置として、プロキシミティー括露光方式の露光装置"LE-4050A"を開発した。

パネルサイズ最大400×500 mm²まで一括露光可能なミラー光学系,パネルサイズの全自動切換,クリーンロボットによるパネル搬送,パネルに対し完全非接触なプリアライメント,4点でギャップを検出し回帰平面を利用したギャップ制御,パソコンによる対話形式の操作などの特長を持っている。

(日立電子エンジニアリング株式会社)

## 液晶用クラスター型スパッタリング装置

TFT (Thin Film Transistor)液晶ディスプレイ用 大型ガラス基板に、透明導電膜や金属膜を均一に成膜 できるクラスター式スパッタリング装置を開発した。

従来の装置が基板搬送トレイを使用したインライン方式であるのに対し、ガラス基板をトレイレスの枚葉方式としている。専用カソードにより、大型基板でも優れた膜特性と、高速搬送機構による高スループット化を実現し、稼動率および生産性の高い装置とした。

主な特長は、(1) 基板サイズ:最大380×480(mm) 対応、(2) 装置設置面積の省スペース化、(3) 大面積用日立カソードによる優れた膜性能、(4) 生産性を高める高速タクト化である。

液晶用クラスター型スパッタリング装置