# システムオンチップ。実現に向けたテスティング技術の取組み

Testing Methods of the System-on-a-Chip

足立寛之

Hiro

井上文仁

Fum

難波正昭

Mase

Hiroyuki Adachi Fumihito Inoue Masaaki Nanba Noboru Yamaguchi

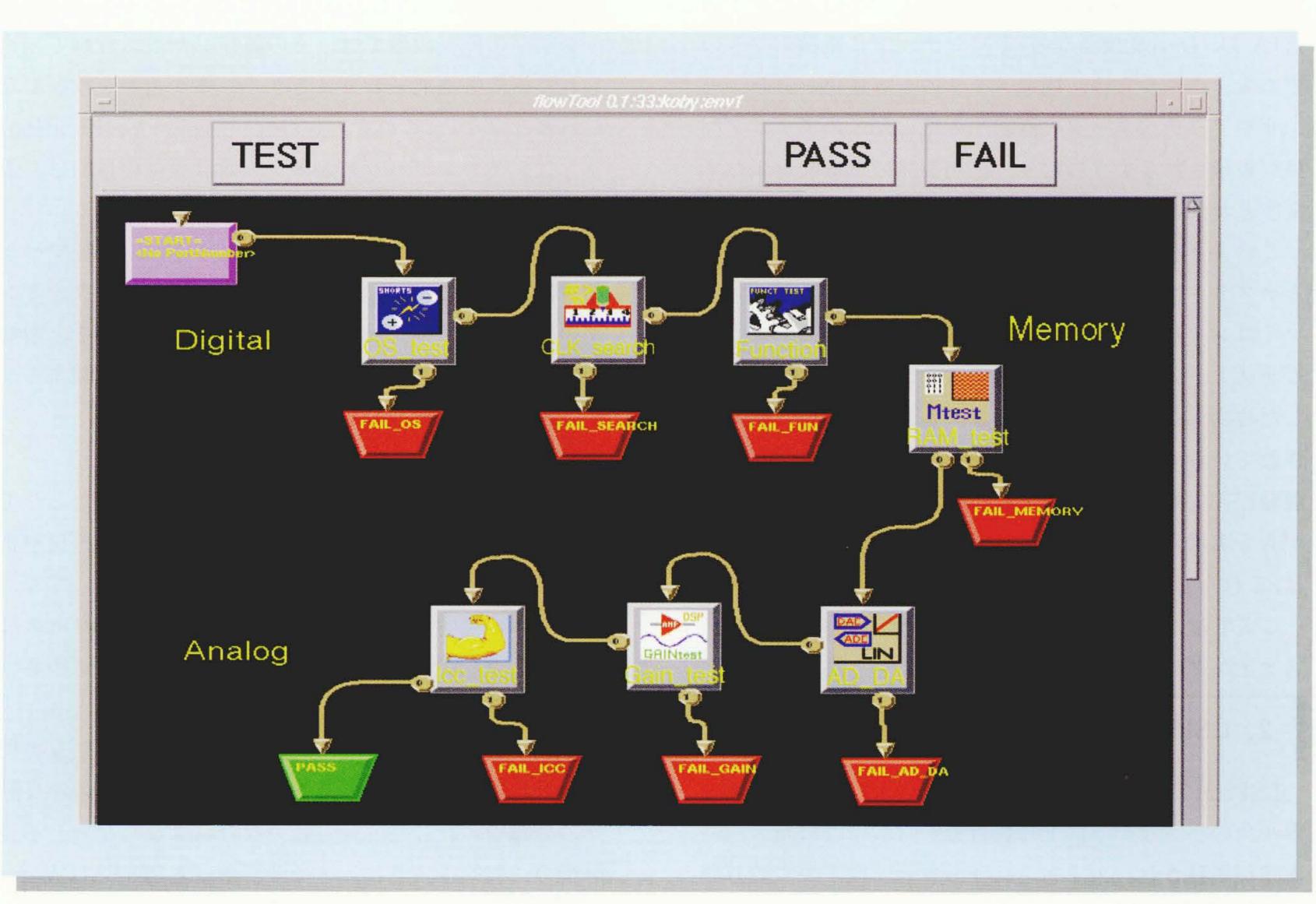

#### オブジェクト指向によるシステムLSIテストプログラムの例

各ボックスはテストの一まとまりを表し、矢印はテストの順序を示す。このような設計をテスタ上で行うには、テスタアーキテクチャの革新だけでなく、テスタ言語のオブジェクト指向化が不可欠である。

マイクロプロセッサ、メモリ、アナログ回路などを混載した将来の高機能・高性能なシステムLSIでは、設計手法がそうであるように、テスティング手法でも構成要素ごとに開発された知的資産〔IP(Intellectual Property)〕を有効に活用しようとする方向に進んでいる。

上に示す画面は、これから将来にかけてのシステム LSIのテストプログラムの一例である。ここで、ボックス はテストの一まとまりを表し、矢印はテストの順序を示 す。各ブロックは階層化しており、例えば、メモリのボ ックスはDC(直流)テストやマーチング パターン テス トなどの下位のボックスで構成する。これらのボックスは、システムLSIの構成要素に対応して作成し、IPとして扱う。

このようなテスト設計をテスタ上で自由自在に行えるようにするには、テスタアーキテクチャの革新だけでなく、テスタ言語のオブジェクト指向化が不可欠である。 さらに、各構成要素ごとに独立性の高い設計手法を導入することにより、テストの標準化とライブラリ化を推進しなければならないと考える。

# 1. はじめに

ディープサブミクロン時代への突入とともに、半導体製品は、高集積化と多機能化の行き着く所、すなわち「システムLSI (System-on-a-Chip)」へと向かっている。システムLSIは現在のところ、半導体応用製品の主要な機能を果たすディジタル部〔マイコン(マイクロコンピュータ)、ロジック、およびメモリ部分〕と一部のアナログ回路(A-D、D-A変換器など)をワンチップに集積したものである。これからは、内蔵メモリの大容量化が進み、センサやアクチュエータに直結するほとんどのアナログ回路が集積されるようになり、応用製品の全機能を果たす文字どおりのシステムLSIになると予想する。

このようなシステムLSIに対して、全体を網羅、統括するテスティング技術はまだ確立されていない。しかし、マイコン・ロジック回路に対するテスト、メモリに対するテスト、アナログ回路に対するテストはおのおの独立した技術として確立されており、さらに、すでに商品化されているメモリ内蔵マイコンやアナログ・ディジタル混載LSIに対するテスト技術は、種々の問題をはらみながらも実用に供されている。システムLSIのテスト技術は、これらの技術をつなぎあわせるところから出発する。ここでは、従来技術を概観する中から、システムLSIテスティング技術の実用化上の課題について述べる。

## 2. LSIテスティングの現状

LSIと言えば、よく知られているように、(1)数ミリメートル角の小さなチップ上に数百万から数千万に及ぶ回路素子が集積され、(2)それらのチップは、数千から数万個(1ロット)が同時にバッチ方式で製造される。これらの特徴により、以下の3分野のLSIテスティング技術が形成されている。

# 2.1 選別テスト

「歩留り」という用語で代表されるように、LSIは、製造されたものすべてが必ずしも良品ではない。数千から数万個の単位で同時に製造されるLSIチップは、その全数がテストにかけられ、良品が選別され、不良品は除去される。LSIテスティングではこれを「選別テスト」と呼び、ウェーハ工程の最後に行うテストを「プローブテスト」、パッケージング完了後の製品出荷前に行うテストを「最終選別テスト」と言う。

選別テストは、量産工程内で全数に対して必ず行われ、 顧客に対する品質を直接保証するものである。一方で、 選別テストの工程はLSIの製造コストの一部を形成する。ここでの保証品質とテストコストは、相反する一面を持っている。テストに十分の時間をかければ、品質はそれだけ向上する。しかし、テスト時間の増大は、テストコストつまり製品価格上昇に跳ね返る。どうすれば品質を落とさずにテスト時間の短縮とテストコストの縮減を図ることができるかが、選別テストの技術的課題である。

#### 2.2 設計検証

新製品の開発段階では、その試作品が設計仕様で定められた機能と性能どおりにできているか否かを検証しなければならない。これを、設計検証(Design Verification)またはシリコンデバッグと言う。設計検証の目的は、設計工程での不具合、つまり設計バグの除去である。

最近のLSIの機能・性能の高度化に伴い、検証すべき項目数が膨大になってきており、また、微妙なタイミングの検証など、検証内容も高難度化してきている。増加の一途をたどる設計検証の作業工数をいかに削減するかが、その大きな技術課題である。

#### 2.3 不良解析

設計検証が済み、選別テストで良品を得ていたとして も、歩留りが低ければ、その原因究明のために不良解析 を行う。また、顧客から返品された不良品についても、 不良原因の究明を行う。これらの不良は製造プロセスに 起因することが多いが、設計での動作マージンが小さい ことによることもしばしばある。

不良解析の難しさは、不良動作がどのチップでも再現するとは限らないことである。解析は、不良品の不良動作の分類や、統計処理から始めなければならない。不良解析の一般的手法では、メモリでやっとWFBM(Wafer Fail Bit Map)が実用的に利用され始めたばかりで、マイコンなどのロジックLSIでは、まだ確立された手法はない。このような不良解析技術は、選別テストや設計検証のテスティング技術の範囲を越え、新しい分野を形成しつつある。

# 3. LSIとテスタ

#### 3.1 テスタの分化と再融合

テスティングを行う装置をテスタと言い,しばしばATE(Automatic Test Equipment)と略称される。テスタは,テスティングに必要な各種の計測器群と,それを制御するためのコンピュータによって構成され,LSIのテスト項目に応じて計測器の制御フローをプログラムできるようになっている。

| 表 1 | テス | トの構成とテスタ | 機種別守備範囲 |  |

|-----|----|----------|---------|--|

|     |    |          |         |  |

選別テストや設計検証では、製品のデータシートに記載されている電気的仕様をすべてチェックする必要がある。

| 分 類       | 項目                              | 内                                                                           | 容          | ロジック<br>テスタ | メモリ<br>テスタ | リニア<br>テスタ |

|-----------|---------------------------------|-----------------------------------------------------------------------------|------------|-------------|------------|------------|

| DC<br>テスト | オープン・ショート                       | 端子周りの断線, 短絡などの致命的不良                                                         |            | 0           | 0          | 0          |

|           | 入出力端子リーク<br>電源電流                | 上記に準ずる端子周りの異常<br>静止時と動作時                                                    | 極端なものは致命不良 | 0           | 0          | 0          |

|           | 最大定格,最小動作保証                     | ストレステスト, ラッチアップ, ブレークダウン                                                    |            | 0           | 0          | 0          |

|           | DO 4+44                         | バイアス系、アナログ回路のA                                                              | C特性置き換え    |             |            | 0          |

|           | DC 特性                           | 入出力レベル,しきい値                                                                 |            | 0           | 0          |            |

|           | DC ファンクション<br>(ロジック I, 0 的故障検出) | スピードやタイミング精度を無視した真理値表的パターンテスト(静的機能)                                         |            | 0           |            | _          |

| AC<br>テスト | AC特性                            | 応用分野向け機能テスト<br>周波数-利得,位相,SN比,ひずみ率,自動利得制御など<br>実装テストのモデル化                    |            | _           |            | 0          |

|           | AC ファンクション                      | 実装をモデル化したパターンによる実周波数テスト<br>(At speed test)                                  |            | 0           | <u> </u>   | _          |

|           | タイミング<br>最大動作周波数                | ゲート遅延時間(Tpd), 立上りと立下り時間(Tr, Tf),<br>セットアップ時間, ホールド時間<br>At speed testの最大保証値 |            | 0           | 0          | _          |

| その他       | メモリパターン依存<br>メモリデータ保持           | チェックボード, マーチング, ギャロッピングほか<br>データ保持, 電圧, 時間                                  |            | 4           |            |            |

注:○(テスティング項目に最適),○(テスティング項目に適),一(テスティング項目に含まず)

テスタは、計測器群の統合化という形で生まれ、どの ようなテストも可能な汎用性が求められた。しかし、LSI の機能・性能の高度化とともに、テスタは適用製品別に それぞれ最適化され、(1) ロジックテスタ、(2) メモリテス タ, (3) リニアテスタに分化した。ロジックテスタとリニ アテスタは, 原始的な汎用テスタが分化したものであり, また、メモリテスタは、ロジックテスタから分化して専 用化したものである。

一方、これらが再融合して、アナログ・ディジタル混 載LSI用としてのアナログ ディジタル ミクスト シグ ナル テスタや、メモリ テスト パターン発生器[ALPG (Algorithmic Pattern Generator)] 付きロジックテスタ が実用化されている。さらに最近では、ディジタルテス タに本格的なリニアテスタを融合しようとする動きも始 まっている。

#### 3.2 テスティング項目とテスタ

選別テストや設計検証では、少なくとも製品のデータ シートに記載されている電気的仕様をすべてチェックす る必要がある。電気的仕様は、ロジック、メモリ、リニ ア(アナログ)の各LSIでやや異なる。テスト項目とLSIの 種類との関係を取りまとめたものを表1に示す。この表 の左半分にテスト項目を示し,右半分にそれらの項目が, (1) ロジック, (2) メモリ, (3) リニアの各テスタの守備範囲 に含まれているかどうかを◎, ○, −で示す。ここで, ◎

は、特にその中で機種の特徴が出せる項目である。

もし、これらすべての項目を1台のテスタで網羅する ことができるようなテスタが開発されれば、それを「シ ステムLSIテスタ」と呼ぶことができる。しかし現実は, システムLSIテスタの姿はまだ見えず、当面はテスト項 目別に分担して、複数のテスタで行わざるをえない。

# 4. システムLSIへの動きとテスティング技術

## 4.1 アナログ・ディジタル混載LSIのテスティング技術

システムLSIの芽生えの一つに、アナログ・ディジタ ル混載LSIがある。少なくともこの種のLSIに対しては、 リニアテスタ、あるいはロジックテスタだけでも十分な テストができなかった。そこで現れたのが、アナログデ ィジタル ミクスト シグナル テスタである。

アナログ ディジタル ミクスト シグナル テスタは, パターンメモリやドライバ、コンパレータを備え、外観 はロジックテスタに似ているが、その良品・不良品の判 定法は異なる。ロジックLSIのような「0, 1」のディジ タルな期待値比較ではなく, デバイスから出力される信 号に含まれる種々の成分(平均値, 実効値, 最大値, 最小 値,基本波,高調波,雑音成分など)をDSP(Digital Signal Processor)で高速に取り出し、それが製品仕様を満たし ているかどうかをチェックするという方法が採られて いる。

#### 4.2 アナログ・ディジタルからディジタル・アナログへ

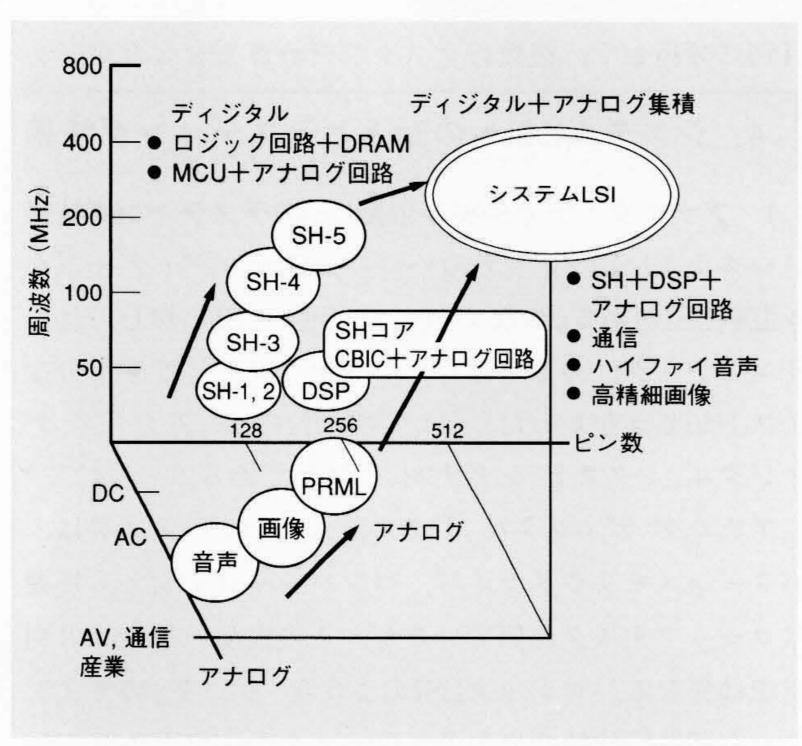

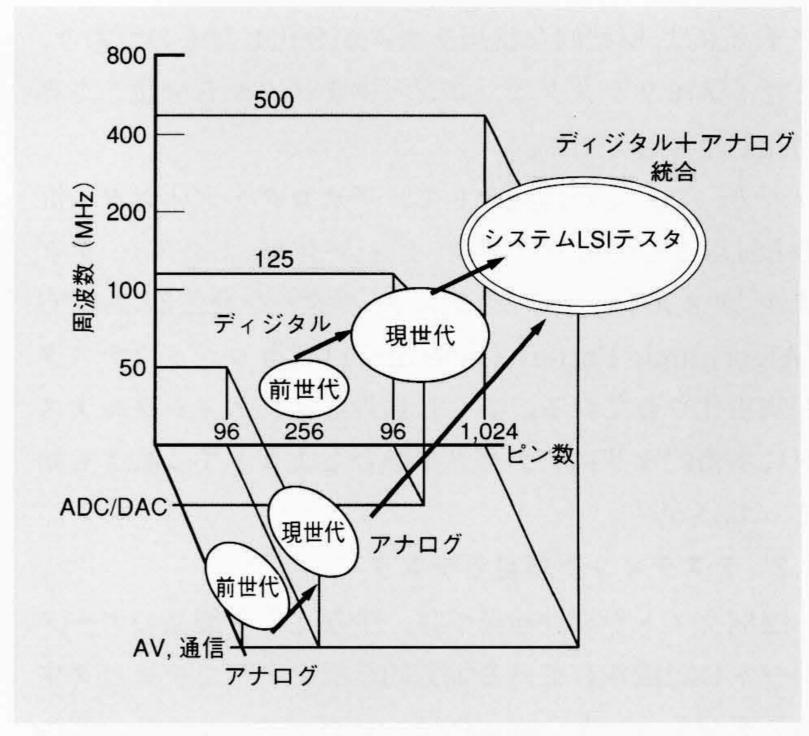

LSI製品がシステムLSIへ向かう流れと、テスタがシステムLSIテスタへ向かう流れを図1に示す。上述のアナログ・ディジタル混載LSIやアナログ ディジタル ミクスト シグナル テスタでは、これらの図で手前側の流れとして示している。一方、奥側の流れは、最近特に大きくなり始めている流れである。

SH-3からSH-4へと、制御用マイクロプロセッサやある種のASIC(Application Specific IC)では、アナログ回路が取り込まれることが多くなってきている。その特徴は、ロジックLSIにひけを取らない複雑・高度な論理的機能を持つ一方で、アナログ部にも本格的な機能・性能の回路を内蔵している点である。システムLSIに、より近づいたLSIである。

このようなLSIは大きなロジック部を持つため、従来のミックスド シグナル テスタでは十分なテストができない。そのため、現在、ロジックテスタに性能面で妥協しないアナログ機能を具備させることにより、このテストに対応しようとする流れが出始めている。

以上述べてきたように、ディジタル・アナログからシステムLSIへの流れでは、テスタの新しい融合が進行しているように見える。

(a) LSIのシステム化の流れ

#### 4.3 DRAM混載からシステムLSIへ

ロジックLSIとDRAMは、いずれも「0, 1」だけの情報を処理するディジタルLSIであるが、テスティングの面から見るとかなりの相違が見られる(表2参照)。用いるテスタも、ロジックテスタとメモリテスタというように、別々の進化を遂げている。中でも際立つDRAMでの相違点は、(1) ピン数が少ない、(2) 容量増大とともにテスト時間が増大し続けている、(3) 同時測定多数個取りの技術が確立していることである。さらに、テストパターンの作成方法にも大きな違いが見られる。

これらの相違点は、ロジックテスタとメモリテスタとの融合の大きな壁となっている。従来、ALPG付きロジックテスタはあったが、DRAMの多数個取りの技術を生かすことができないなど、多々問題があった。小容量のメモリ混載の場合は、大容量DRAMを混載することを前提にすれば、テスト時間、つまりテストコストの面で、ロジックとメモリが融合したテスタを用いるよりも、現状のロジックテスタ+メモリテスタ併用のほうが、当面は有利と判断されている。

# 5. システムLSIテスティングの今後の課題

システムLSI時代のテスティング技術の課題は、(1)製

(b) テスタの進化と統合化

#### 注:略語説明

DRAM (Dynamic Random Access Memory), MCU (Microcontroller Unit), CBIC (Cell Based IC), PRML (Partial Response Maximum Likelihood) AV (Audiovisual), ADC (Analog-to-Digital Converter), DAC (Digital-to-Analog Converter)

#### 図1 LSIのシステム化に伴うテスタの進化と統合化

ディジタルとアナログの混載によってLSIのシステム化が進み、ディジタルテスタとアナログテスタの時間精度・電圧精度の大きなギャップを埋めてシステムLSIテスタへと統合される。

#### 表 2 ロジックLSIとDRAMのテストの比較

テストコストの面では、ロジックとメモリが融合したテスタを用いるよりも、ロジックテスタとメモリテスタを併用するほうが有利で ある。

| 項目                        |            | ロジックLSI             | DRAM                                                 | DRAM混載LSI                   |  |

|---------------------------|------------|---------------------|------------------------------------------------------|-----------------------------|--|

| #U.D. *                   | テスト周波数     | 10~100 MHz,今後高速化    | 同左                                                   | 同左                          |  |

| 製品の 特徴・                   | テストパターン    | 設計シミュレーションで生成(ランダム) | テスタで演算し生成(規則的)                                       | 両方が必要                       |  |

|                           | ピン数        | 多い                  | 少ない                                                  | 多い                          |  |

| 使用テスタ                     |            | ロジックテスタ             | メモリテスタ                                               | ロジックテスタと<br>メモリテスタの併用       |  |

| テストの<br>経済性               | テスト時間      | 数秒~10 s             | 数十秒~数百秒                                              | . /EN/                      |  |

|                           | 同時測定数      | 1~2個                | 数十個~数千個                                              | → Ⅰ個当たりテスト時間は → 約5秒         |  |

|                           | Ⅰ個当たりテスト時間 | 数秒                  | 数秒                                                   | ポソ コ イシ                     |  |

| 開発におけるテストの課題<br>(不良解析の課題) |            | ・チップ設計を検証するための解析    | <ul><li>・歩留りを上げるための解析</li><li>・性能を上げるための解析</li></ul> | ・各部を切り分けた評価<br>・各部のつなぎ部分の評価 |  |

| 量産におり                     | けるテストの課題   | ・開発〜量産の立ち上げ工数ゼロ     | ・テスト時間短縮<br>・多数個取り                                   | ・経済的なテスト<br>・ASIC的な生産対応     |  |

品開発段階での設計検証・不良解析の期間・工数をいか に抑えるか、(2)量産工程でのテストの経済性をいかに確 保するかの2点に絞られる。その解決策は、テスティン グ技術の範疇(ちゅう)にとどまらず、設計技術にも影響 を及ぼさざるをえない。

#### 5.1 テストの容易化設計

マイクロプロセッサやアナログ回路, DRAMなどを混 載するシステムLSIでは、設計不良にせよ製造不良にせ よ,不良がどこにあるか,不良の原因が何かを解析する ことが従来以上に困難になってくる。これが容易にでき なければ、製品開発に手間取ることになる。

それを防止する第一の方法は、システムLSIの各構成 要素を各構成要素ごとに切り分けてテストする手段を, チップに組み込むことである。システムLSIチップは,あ るテストモードでは、単体のマイクロプロセッサチップ や裸のDRAMにすることが必要である。これは、システ ムLSIに必要な最小限のテスト容易化設計である。

テストの容易化設計は、量産工程でのテスト時間短縮 のためにも活用しなければならない。従来、チップサイ ズ増による製造コストの上昇を抑えるため、テストの容 易化設計の導入をためらう傾向があった。しかし、単体 のロジックLSIやメモリLSIでも、テストパターンの増 加、テスト時間の増加はすでに限界に達しており、テス トの容易化設計なくしては、もはやシステムLSIのテス トを行うことはできない。最近では設計ツールによるサ ポートも充実してきており、今後は、テストの容易化設 計はますます一般化していくと考える。中でも、BIST (Built-in Self-Test)をどう生かすかが、今後の最大の課

題である。

## 5.2 モジュール化設計とモジュール化テスト

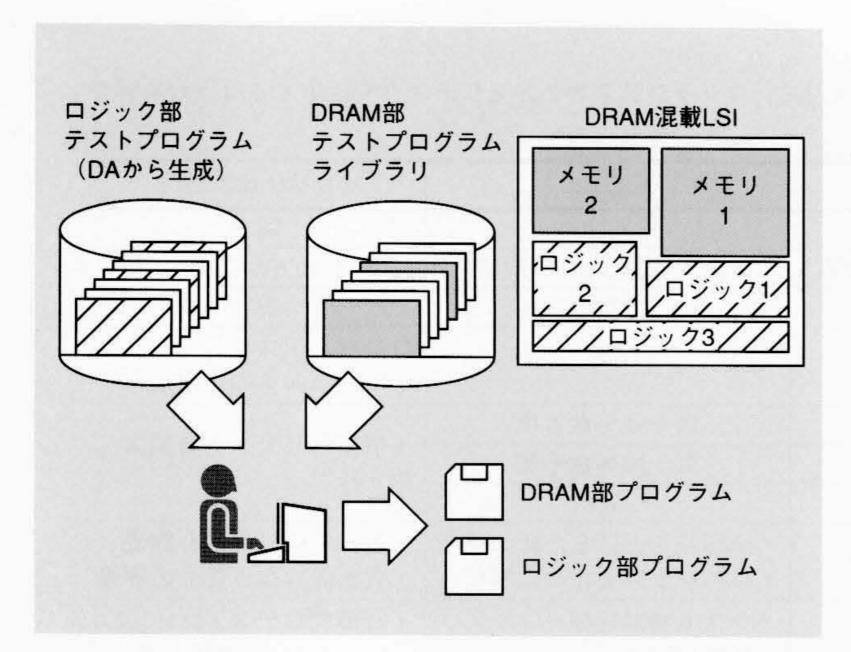

上述のように、各構成要素を相互に独立した機能とし て設計していれば(モジュール化設計),テストのモジュ ール化も可能となる。テストのモジュール化とはテスト プログラムの標準化であり、ライブラリ化である。モジ ュール化テストの例としてDRAM混載LSIのテスト法 を図2に示す。テストプログラムは、ロジック部、DRAM 部ともおのおの独立して作成する。

モジュール化設計をさらに推し進めると, 知的資産 (IP)の概念へ行き着く。システムLSIが一般化すればす るほど、設計モジュールのIP化は急速に進展すると見ら れている。これに伴い、テスト(テストプログラム)のIP 化も焦眉(び)の課題となる。

モジュール化テストが実現しても、システム全体とし ての特性,動作,品質保証をするためのテストをいかに 行うかの問題が残されている。その問題解決を目指し、 システムLSI全機能に適合するスーパーテスタ(システ ムLSIテスタ)の開発は始まっており、その製品への適用 技術も進展しつつある。

#### 5.3 テストプログラム言語の変革

テスタのハードウェアを制御し、テストを実行させる ソフトウェア環境を「テスタOS (Operating System)」と 呼んでいる。従来,テスタOSの中核言語は,BASIC, PASCAL, Cなどに準じた手続き型言語であった。しか し、テストのモジュール化にとって、手続き型言語より もオブジェクト指向言語のほうが、(1)グラフィカルなユ ーザーインタフェースを提供しやすい,(2)デバイスやモ

注: 略語説明

DA (Design Automation)

#### 図2 DRAM混載LSIのテスト方法

テストのモジュール化には、プログラムの標準化、ライブラリ化 が必要である。

ジュールの電気的特性を記述しやすいなど, 多くのメリットを持つ。

実際に、テスタ言語のオブジェクト指向化は、OSも含める形で動き始めており、SHシリーズマイコンでは、主として開発レベルでのテスティング業務で適用を開始している。33ページの画面は、その環境で作成したものである。

# 5.4 量産でのテスト経済性の確保

従来、DRAMの開発では、製造プロセスの開発と同期させ、時間をかけて設計とプロセスの検証を行い、製造装置の条件出しをしながら徐々に歩留りを上げるという手順を採ってきた。テストプログラムは手作りであり、その確定までには、上記の開発から量産までの全期間が必要であった。

しかし、システムLSIはASIC的性格が強く、開発開始から量産開始までに長期間をかけることはできない。この意味でも混載されるDRAMを標準化し、各DRAMに対応したプログラムをライブラリ化し、ロジック部と合成し、短期間でプログラムを作る技術が必要である。DRAMでこそ、モジュール設計技術やオブジェクト指向テスタ言語が強く求められている。

ロジックLSI単体、DRAM単体で考えても、LSIは高速・高集積・多ピン・パッケージ多様化と、テスティングではますます困難な課題が続出している。その中にあって、テストコストを抑える努力が地道に行われているものの、ロジックLSIとDRAMとでは、その方向にかなりの相違がある。前述したように、当面はDRAM混載の

テストでは、それぞれ専用のテスタ2台を使用するのが 最も経済的である。しかし、量産現場へのテスタ投資戦 略も考慮したトータルなテストコストでは、スーパテス タ(システムLSIテスタ)を開発して使用すべきか、ある いは、当面の2パステスト方式を進化させるべきかを十 分に検討しなければならない。

# 6. おわりに

ここでは、システムLSIのテスティングの概要について述べた。

システムLSIは、メモリ、マイコン、アナログ回路といった固定したカテゴリーの半導体ではなく、まったく新しい概念の上に作られた半導体製品である。したがって、テスティングでも従来の延長で考えては、コスト面でまったく採算が合わなくなってしまう。開発段階であれ、量産工程であれ、テストを行うという視点で考えた場合、システムLSIの設計でのテストの作り込み、具体的にはテストの容易化設計、BISTなどは最も重要である。また、テスト設備もそれに合わせてカスタマイズすることが重要であり、半導体メーカーとテスタメーカーのより緊密な情報交換が必要になってくるものと考える。

#### 執筆者紹介

**足立寛之** 1977年日立製作所入社,半導体事業部 生産技術センタ 所属 現在,マイコン・ASICのテスト技術業務に従事

井上文仁 1960年日立製作所入社,半導体事業部 生産技術センタ 所属 現在,システムLSIのテスト技術開発に従事 E-mail: inouef@cm. musashi. hitachi. co. jp

難波正昭 1976年日立製作所入社、半導体事業部 生産技術センタ 所属 現在、メモリ製品のテスト技術業務に従事 E-mail:namba@cm. musashi. hitachi. co. jp

山口 昇 1971年日立製作所入社,半導体事業部 生産技術センタ 所属 現在,設計のテスト技術サポート業務に従事 電子情報通信学会会員,IEEE会員 E-mail:yamaguch@cm.musashi.hitachi.co.jp