# シリコン半導体デバイスの展望

R&D Prospects of Si ULSI Devices

久本大 Dai Hisamoto 杉井信之 Nobuyuki Sugii 鳥居和功 Kazuyoshi Torii 龍崎大介 Daisuke Ryuzaki 島明生 Akio Shima

注:略語説明ほか DRAM( Dynamic Random Access Memory ), MPU( Micro Processing Unit ), ハーフピッチ( 配線パターンピッチの ½ )

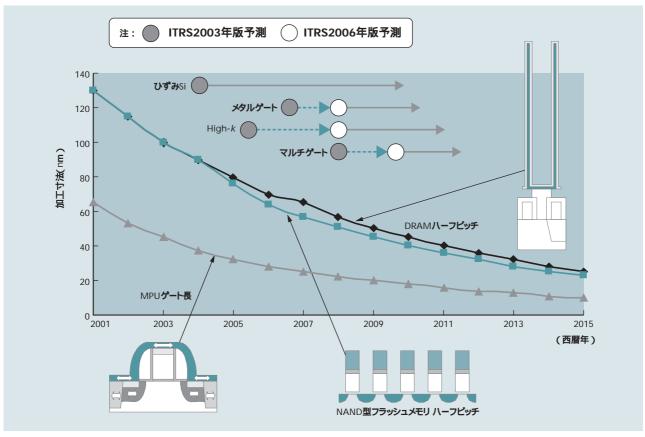

#### 図1 微細加工技術の国際半導体技術ロードマップ(ITRS)

MPUのゲートは,シュリンク技術を用いることで,総合的な加工技術水準を示すハーフピッチの値に比べ,小さな加工サイズを実現している。また,2005年から,微細加工技術の牽(けん)別役が,これまでのDRAMから,NAND型フラッシュメモリに置き換わった。

21世紀になり、従来のスケーリングによるCMOS高性能化を維持するため、テクノロジーブースタの導入が提案されてから4年が経過し、2世代を超えるデバイス開発が行われてきた。この間、微細加工はNAND型フラッシュメモリによって牽引され、ロードマップ予測を上回る速度で推移してきた。

しかし,ブースタとして期待された技術のうち,ひずみを除くと実用化の域に達せず,予定された時点での導入はなされていない。

そこで、半導体デバイス製造装置開発の指針となるシリコン半導体デバイスの研究開発について、これらブースタ技術を軸に2007年現在の状況をまとめ、その将来の方向性について検討する。

## 1.はじめに

40年以上にわたり、急速な成長を続けてきた半導体産業は、今世紀に入り性能向上の指針が大きく変わり始めてきている。そこで、2007年現在のCMOS( Complementary Metal Oxide Semiconductor )を中心としたULSI( Ultra-Large Scale Integration )プロセス・デバイスの研究開発状況についてレビューを行う。2003年に作成されたITRS( International Technology Roadmap for Semiconductor )では、性能向上を維持し続けるには、新たなトランジスタの性能向上法であるテクノロジーブースタが必要になることが示されていた。時期については、2006年以降、順次導入されることが期待されていたが、これらブースタ技術の開発状況を点検する( 図1参照 )。

14

ここでは、ブースタとして挙げられた(1 アルチゲート構造、(2 )いずみチャネル、(3 )High-k(高誘電率)、(4 )メタルゲートに関する近年の研究開発の進展について紹介する。(3)(4)はゲートスタックとしてまとめて記す。さらに、これらの開発状況を踏まえたITRSの2005年版から2006年版への見直しの中で最も大きく性能向上に寄与する項目として注目された、浅接合技術について述べ、最後に、トランジスタに代わり、ULSIの性能を決める主役となってきている配線技術の進展について述べる。

## 2.マルチゲートMOSFET

マルチゲートMOSFET( Metal-Oxide-Semiconductor Field-Effect Transistor )は,複数のゲートからの電界効果によってチャネル制御をすることで,低不純物濃度のチャネルのリーク電流を抑えるものである。高濃度チャネルによる移動度劣化やGIDI( Gate Induced Drain Leakage を回避できるため,性能向上のブースタとして期待されている。さまざまなデバイス構造が考えられてきたが,現在,日立製作所の提案したフインチャネルを用いたもの( DELTA( Fully Depleted Lean-Channel Transistor ) , FinFET , omega - FET などに集約されつつある。フィンチャネルデバイスの動向としては,リソグラフィーおよびドライエッチング技術の進歩により稠(ちゅう)密なピッチのフィンが形成され,実効駆動力の向上が実証されたこと,バルク基板を用いたフィン形成が盛んになってきたこと,しきい値ばらつきの抑制が示されたことが挙げられる。

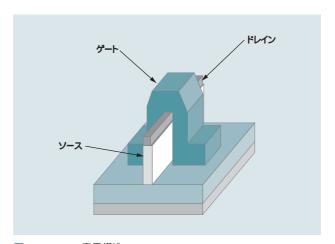

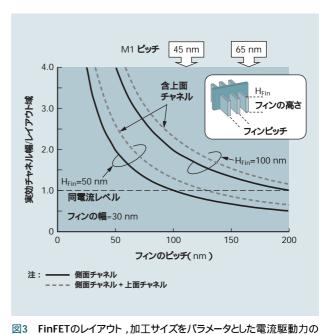

代表的なFinFETの素子構造を図2に示す。薄膜状に切り出したフィンをチャネルとするため、電流駆動力を決めるチャネル幅はフィンの高さで決まる。そのため、駆動力を向上させるには、微細幅のフィンを狭いピッチの中で多数並列配置する必要がある。図3は、加工寸法とピッチをパラメータに、従来プレーナ型に対する駆動力比を示したものである。65~45 nmノードの加工が実現するようになり、同じレイアウト面積でプレーナ型MOSを超えるFinFETが報告されるようになった。)。

FinFETは, 当初, SOI( Silicon on Insulator )の膜厚によってフィンの高さを制御するためSOI基板を用いて形成した<sup>3</sup>)。しかし, 近年ではバルク基板でもフィンの形成が盛んに行われている<sup>6</sup>)。これは, CMP( Chemical Mechanical Polishing )技術が習熟してきたことにより, 深さ方向の制御について実績が積まれてきたからと考えられる。

バルクMOSFETのスケーリング限界として、しきい値ばらつきが注目されている。これは、加工寸法ばらつきを抑えても、不純物の統計的ゆらぎにより、ばらつきが大きくなることが予測されるためである?)。

この不純物ばらつきについては、

図2 FinFETの素子構造 マルチゲートを実現するFinFETのデバイス構造を示す。

図3 FINFETのレイア・ファー・加工リイスをパラメータとした電流駆動力の 比較 同じレイアウト面積でプレーナ型MOSを超えるFinFETが報告されるようになっている。

Vth

$$\frac{t_{ox}N_A^{1/4}}{\sqrt{L_aW_a}}$$

と表される $^8$ ?。 $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$ .  $^8$

## 3. ひずみ応力効果

本誌86巻7号(2004年7月号)において,ひずみ制御技術の現状を報告した。ひずみ制御技術とは,MOSFETのチャネルを形成するSi結晶に種々の方法で応力を加えることで結晶変形(ひずみ)を起こして,伝導キャリア(電子または正孔)の移動度を向上させるものである。現世代のCMOSでは微細化のみによる性能向上が困難になっており,そこでの性能向上の切り札になるとの期待が大きい。ここ2~3年のCMOSデバイスプロセスの学会発表の半数以上が,何らかの形でひずみ制御技術を取り入れたものである,と言っても過言ではない。

現在,主流のひずみ印加技術は,製造プロセスを制御することで達成する,いわゆる外部応力技術である。ゲート電極の上部に引っ張り,ないしは圧縮応力を持つSiN膜を形成する方法や,ソースドレイン部分を掘り込み,ここにSiGeないしはSiCを選択エピタキシャル成長させる方法が重点的に検討されている。以前は盛んに研究されていたSiGeを含む基板を用いたひずみ制御技術は,基板コストや結晶欠陥の懸念などで敬遠されており,唯一SSOK Strained Silicon on Insulator と呼ばれるタイプの基板だけが現在でも実用化候補と考えられており,SOI基板メーカーから市販されている。以下に,外部応力技術における加工技術の重要性について述べる。

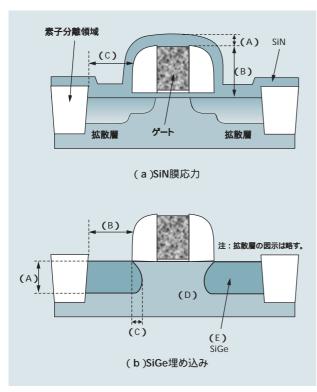

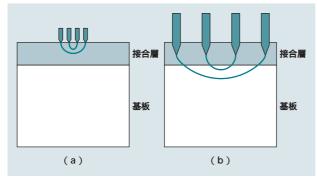

外部応力技術においては、図4に示すように加工寸法その ものが、応力の大きさ、すなわちデバイスの性能向上度に密

図4 外部応力技術において、応力の大きさに影響する寸法 (a)においての(A)はSiNの膜厚、(B)はゲート電極の高さ、(C)はゲート電極 から素子分離領域までの距離を示す。(b)においての(A)はSi基板の掘り込み 深さ、(B)は掘り込み領域の幅、(C)はアンダーカットの大きさ、(D)は掘り込んだ 領域の局率、(E)はエピタキシャル成長させたSiGe層の膜厚と組成を示す。

接に関係している。SiNの膜応力を用いた場合には,SiNの 膜厚(A),ゲート電極の高さ(B),ゲート電極から素子分離領 域までの距離 C )のすべての寸法がひずみの大きさに影響す ることが指摘されている。SiGeを埋め込むタイプにおいても、Si 基板の掘り込み深さ(A)と,掘り込み領域の幅(B),アンダー カットの大きさ(C),掘り込んだ領域の局率(D),エピタキシャ ル成長させたSiGe層の膜厚と組成(E)がひずみの大きさに影 響する。特にSi基板の掘り込み工程においては、エッチングス トッパー膜などの使用が不可能なために,装置性能に完全に 依存せざるを得ない。最近の微細CMOSでは、本誌88巻3号 (2006年3月号)に示したように,素子特性のばらつき増大が 大きな課題となっており、ひずみ制御技術を適用することに よって特性ばらつきが増大するようでは、その技術を採用する ことが難しい。このように、ひずみ制御技術と特性ばらつきの 低減を両立するためには,上記各部の寸法形状の評価技術 や制御技術を確立することが不可欠である。前述したテクノ ロジーブースタの候補の中で,唯一実用レベルにこぎ着けた 技術が外部応力によるひずみ制御技術である。しかしながら、 適用製品は一部メーカーの高性能MPU( Micro Processing Unit )のみにとどまった状態で約3年が経過している。この理 由は、性能ばらつきを吸収できるだけのレンジを持ったMPUの ような大規模製品だけが現時点ではひずみ制御技術のメリッ トを享受できる状態にあるからと考えられる。低電力製品も含 めた、より多様な製品に適用していくために、加工技術の高 度化が強く望まれる。

# 4.ゲートスタック

High-kによるゲート絶縁膜と、多結晶シリコンゲートに代えてメタルゲートを用いる構造は、CMOSのオフリークを下げ、オン電流を向上させるうえで、きわめて有効なため、実用が最も期待されてきたテクノロジーブースタである。しかし、導入時期の見通しが後回しにされ続けてきた。ここでは、これまで検討されてきた材料の経緯を俯瞰(ふかん)する。

High-k材料の選択にあたっては、まず二元系酸化物の熱的安定性が検討され $^{9}$ )、次に、熱力学的安定性の検討によって絞られた候補のうちから、誘電率、パンドギャップ $^{10}$ を基に、候補がさらに絞り込まれた。誘電率10以上で、パンドギャップが5 eV以上を基準として、 $Sc_2O_3$ 、 $Y_2O_3$ 、EuO、 $La_2O_3$ 、 $Gd_2O_3$ 、 $Ho_2O_3$ 、 $Er_2O_3$ 、 $Tm_2O_3$ 、 $Lu_2O_3$ 、 $ZrO_2$ 、 $HfO_2$  、 $Al_2O_3$ の12種類が候補材料として選ばれた。これらの材料のうち希土類元素は吸湿性が大きいことから、属酸化物( $ZrO_2$ 、 $HfO_2$ )と属酸化物( $ZrO_2$ 、 $ZrO_3$ )が検討の中心になった。実際の薄膜作製と熱安定性の評価が進められた結果、 $ZrO_2$ は900 程度でシリサイドを形成することが明らかになった。一方、 $ZrO_2$ は1000 程度まではシリサイド化を起こさないが、結晶化温度

16

|     | 1A | 2A    | 3B | 4B       | 5B    | 6B     | 7B       |       | 8             |     | 1B          | 2B    | 3A   | 4A | 5 <b>A</b> | 6A | 7A | N  |

|-----|----|-------|----|----------|-------|--------|----------|-------|---------------|-----|-------------|-------|------|----|------------|----|----|----|

| 1   | Н  |       |    |          |       |        |          |       |               |     |             |       |      |    |            |    |    | Не |

| 2   | M  | Be    |    |          |       |        |          |       |               |     |             |       | В    | С  | N          | 0  | F  | Ne |

| 3   | Na | Mg    |    |          |       |        |          |       |               |     |             |       | AI   | Si | Р          | S  | CI | Ar |

| 4   | К  | Ca    | Sc | M        | ٧     | Cr     | Mn       | Fe    | Со            | Ni  | Cu          | Zn    | Ga   | Ge | As         | Se | Br | Kr |

| 5   | Rb | Sr    | Υ  | Zr       | Nb    | Мо     | Tc       | Ru    | Rh            | Pd  | Ag          | Cd    | In   | Sn | Sb         | Те | -1 | Xe |

| 6   | Cs | Ba    | L  | Hf       | Та    | W      | Re       | Os    | lr            | Pt  | Au          | Hg    | TI   | Pb | Bi         | Ро | At | Rn |

| 7   | Fr | Ra    | Α  |          |       |        |          |       |               |     |             |       |      |    |            |    |    |    |

|     |    |       |    | •        |       |        |          |       |               |     |             |       |      |    |            |    |    |    |

|     |    | L     | La | Ce       | Pr    | Иф     | Pm       | Sm    | Eu            | Gd  | Tb          | Dy    | Но   | Er | Tm         | Ур | Lu |    |

|     |    | Α     | Ac | Th       | Pa    | U      | Np       | Pu    | Am            | Cm  | Bk          | Cf    | Es   | Fm | Md         | No | Lw |    |

| : 💙 | 放射 | 性元素   | Х  | 常温で固     | 体でない  | ,または , | 1,000 K以 | 下で融解  | ,分解 ,蒸        | 発 × | Si <b>L</b> | りも酸化さ | れやすい |    |            |    |    |    |

|     | 比談 | 電率10未 | 満  | <b>₹</b> | サイドを作 | ₹ X    | 70       | ドギャップ | ieV <b>未満</b> |     |             |       |      |    |            |    |    |    |

図5 High-k材料の選択

判定基準は、(1)常温において固体であること、(2)放射性物質でないこと、ソフトエラー防止)、(3)デバイス製造のための処理温度(1,000 K(727 ))において融解、蒸発、分解を起こさず、Si基板上で安定していること、(4)誘電率10以上で、パンドギャップが5 eV以上であることの四つである。

が450~600 と低いという問題があることが明らかとなった。 多結晶膜をゲート絶縁膜に使うことの弊害については議論があるが、検討の中心は、活性化アニールなどの高温プロセスを通しても非晶質状態を保つことのできるようにHfO2にAl2O3やSiO2を添加した材料に絞られた(図5参照)。

ハフニウムアルミネイト( HfAlO )膜のAl<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>組成比と誘電率はほぼ線形の関係にあり、Hf組成30%程度で15程度の誘電率が得られ、1,050 程度の熱処理に耐えられる<sup>11)</sup>。 Al<sub>2</sub>O<sub>3</sub>とHfO<sub>2</sub>の交互積層によって作製可能であることから、ALD( Atomic Layer Deposition:原子層気相成長法 )で形成されることが多い。

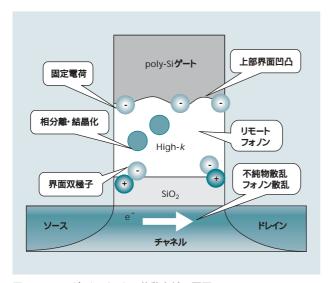

図6 High-kゲートスタックの移動度低下要因 High-k膜に起因する移動度低下要因があることを示す。

一方 ,ハフニウムシリケイト( HfSiO )は ,ALDに適したSi材料がなくMOCVD( Metal-Organic Chemical Vapor Deposition )法で形成されることが多かったが ,前駆体の開発により ,ALDによる製膜も可能となっている。

材料の絞り込み後, High-kゲート絶縁膜にとって, 移動度の低下としきい値の制御が課題であることが明らかになった。そこで, 日立グループにおいては, High-k膜に起因する移動度低下要因があることを明らかにした12(図6参照)。また, この知見を受け, 界面窒素濃度精密制御技術を開発し, 移動度低下を抑制できることを示した13)。

しきい値制御の課題とは、例えばHfO₂系のゲート絶縁膜を用いるとpFETのしきい値電圧が0.5 V以上も高くなり、従来のチャネルインプラントでは補いきれなくなることである。原因についてホップス(C.Hobbs)らは系統的な実験を行い、フラットバンドシフトがHfSiONの膜厚や下地膜の膜厚によらないことから、上部界面に原因があることを示した¹⁴'。白石ら¹⁵〉は、HfSiON膜中での酸素欠損の発生とそれに伴うpoly-Si側への電子の移動により、上部界面に双極子が形成されることがフラットバンドシフトの主な原因であることを示した。日立グループでは、この現象を逆に利用して、低電力版トランジスタのオン電流を増やす方法を提案している¹⁵〉。

ロジック用では45 nmノード以降,EOT( Equivalent Oxide Thickness ) < 1 nmがターゲットになったことで,誘電率が高い La<sub>2</sub>O<sub>3</sub>をAl<sub>2</sub>O<sub>3</sub>に添加したランタンアルミネイトが検討され始めている<sup>17</sup>)。

また, poly-Si電極の空乏化による反転側容量の増加(0.3

~0.4 nm )が無視できなくなるため、High-k膜は空乏化のないメタルゲートとセットで導入されるとの見方が大勢となった。しかし、nFET、pFETに別々のメタルを用いるデュアルメタルゲートを採用すると工程が複雑になり、コストが大幅に増大してしまう。この課題に対して、株式会社ルネサステクノロジからは、pFETのみをpoly-Si/TiN積層のメタルゲートとし、nFETはリンドープpoly-Siとすることでゲート空乏化を最小限に抑えつつプロセスコストの増大を抑える方法が提案されている<sup>18</sup>。n、pともにメタルゲートにする方法としては、ゲートをすべてシリサイドで置き換えてしまうフルシリサイドゲート(FUSI:Fully Silicided)が検討の中心になっている。シリサイドの組成や、不純物の偏析効果によってn、pに適した仕事関数を得ようという研究が活発になっている<sup>19</sup>。

また,最近,「一般化された電荷中性点」と酸素空孔モデルの組み合わせにより,金属/Hf系High-k絶縁膜界面の有効仕事関数を記述する理論が提案されており<sup>200</sup>,メタルゲート電極とHigh-k絶縁膜の組み合わせによるゲートスタックの設計指針も得られつつある。

#### 5. 拡散層形成技術

High-k導入の見送りによってゲート絶縁膜の縮小が止まったことから,性能向上を維持するために,これに代わるテクノロジーブースタとして拡散層形成技術が着目されている。浅接合化により,実効チャネル長を大きくすることで短チャネル効果を抑制できること,また,拡散層の抵抗低減により,駆動力向上が期待できるためである。極浅接合形成技術として活性化や不純物注入技術の詳細と,それらの評価技術について以下に述べる。

#### 5.1 アニール技術

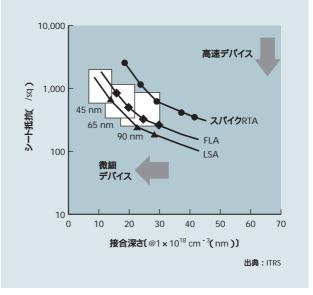

45 nmノードを境に、拡散層形成において新しい技術が導入されようとしている。これは、図7のITRSに示されているようなCMOSのS/D(Source/Drain)拡散層領域に要求される低抵抗極浅接合を実現することが、従来技術であるスパイクランプアニール(スパイクRTA(Rapid Thermal Anneal))+イオン注入の組み合わせでは困難となってきているからである。アニール処理に求められる条件は「高温」、「極短時間」であり、LSA(Laser Spike Anneal)\*・、FLA(Flash Lamp Anneal)\*・といった1,200~1,350 の高温、μs~msの極短時間で加熱するサブミリ秒アニール技術が有力視されている。トランジスタのしきい値電圧は実効的なチャネル長Len・に比例するため、微細化とともにばらつきは増大する。さらに、トランジスタの遅延時間は拡散層とゲート電極のオーバーラップ容量に強く依存し、Lenのばらつきが直接影響するようになる。サブミリ秒アニール技術はデバイス縦方向の微細化、すなわち浅接合化だけでなく、

注:略語説明 RTA( Rapid Thermal Anneal ) ,FLA( Flash Lamp Anneal ) LSA( Laser Spike Anneal )

図7 LSI世代ごとに必要とされる拡散層のシート抵抗と接合深さとの 関係

45 nmノード以降,拡散層形成において新しい技術の導入が考えられている。

S/D拡散層の横方向ばらつきによるLefのばらつきも制御するも のとして期待されている。最終的なプロセスモジュールは現状 のスパイクRTAをこれら新規アニール技術で単純に置き換え ることである。しかし45 nmノード拡散層に関してはサブミリ秒 アニールだけで形成するのは90,65 nmなど旧世代のデバイ スから拡散層周りの不純物プロファイルが大きく変わり,再構 築が必要なためデバイス開発期間が長くなる。そこで、(1) Halo条件微調整およびインジウム(In),アンチモン(Sb)といっ た重元素の適用,および,(2)S/D拡散層への炭素(C),室 素(N),フッ素(F)といった2次ドーパントの適用による横方向 拡散抑制などの短チャネル効果抑制技術の進展とともに,ス パイクRTA+LSA ,またはスパイクRTA+フラッシュというスパイ クRTAの延命技術が主流となりつつある。この場合は、デバ イス性能向上は微細化というより,高温極短時間LSAまたはフ ラッシュ熱処理によるゲート電極,拡散層不純物の活性化率 向上で達成されている。

#### 5.2 不純物注入技術

極浅拡散層形成のためのイオン注入エネルギーは,質量の軽いP型不純物であるボロン(B)では0.5 keV以下になるところまできている。注入エネルギーの低エネルギー化にはビーム電流の低下による生産性の低下,エネルギー減速モードの適用よるエネルギーコンタミネーションの問題がある。そこでBF2のような質量の重い分子イオン注入を用い実効的に注入エネルギーを高くする手法がとられている。さらに発展させたものとしてデカボラン(B10H14),オクタデカボラン(B16H22)<sup>33</sup>を注入イオンとして用いるクラスターイオン注入技術が挙げられる。この技

術のメリットは加速エネルギーを上げ、ビーム電流を下げても従来と同等の注入量が得られるため、生産性が向上することと、ビーム角度拡(ひろ)がりを抑制できることである。このイオンビームの角度拡がりは上記トランジスタ特性のばらつきに直接影響を与えるものであり、極浅接合化とともに抑制すべき重要なパラメータである。

#### 5.3 評価技術

拡散層の評価は,主に抵抗値測定と深さ方向濃度プロファイル評価に分けられる。

前者には四端子探針接触による拡がり抵抗測定技術が用いられてきたが、拡散層の極浅接合化に伴い、探針が突き抜けて正確な測定は困難になりつつある。そこでHgプローブを用いた非接触測定技術<sup>24)</sup>、あるいはμmスケールの探針を用い接触面積および突き抜け深さを浅くした測定技術(図8参照 )<sup>5)</sup>などが開発されつつあり、45 nm量産工場におけるインライン評価に適用されてくると思われる。

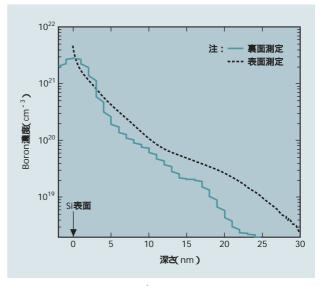

後者に関して言えば、従来技術であるSIMS(Secondary Ion Mass Spectrometry: 二次イオン質量分析法 )による深さ方向の 一次元的な濃度プロファイルの評価だけでは不十分になりつ つある。これは,極浅接合化に伴い不純物がSi最表面に近 づくにつれ、SIMS測定における一次元素のノックオンによって 測定すべき表面近傍での濃度プロファイルがひずんでしまうた め,正確な測定が不可能であること,およびデバイス構造に 則した二次元的濃度プロファイルが要求されることなどの理由 による。SIMSに関しては表面の影響を受けなくするため ウェーハ裏面からの測定が活発になってきている(図9参照)。 また,原子間力顕微鏡(AFM:Atomic Force Microscope と拡 がり抵抗測定技術を組み合わせ,デバイス断面構造の二次 元濃度プロファイルを観察する技術SSRM(Scanning Spread Resistance Microscopy:走査型拡がり抵抗顕微鏡 光研究され ている27)。ただこれら手法はいずれも高度な加工技術を必要 とするものであり、今後さらに簡便な方法の開発が求められる。

図8 四端子探針による極浅接合測定模式図

四端子探針による極浅接合測定の $\mu$ mスケールを(a)に、 $\mu$ mスケールを(b)にそれぞれ示す。同じ接合を測定しても、プローブが大きく間隔が広いと下地層の影響を受け、抵抗値の正確な測定ができなくなる。

#### 6.LSI配線技術の動向

これまでに述べたMOSFET技術は、LSI性能を決定する基本要素であるが、一方でMOSFETを相互に接続するための配線技術の重要性も急速に増している。90 nm世代以降のロジック系LSIでは、全体の信号遅延や消費電力の約半分が配線に起因すると言われている<sup>28</sup>。これら信号遅延や消費電力を抑制するには配線抵抗や配線間容量を低減することが必須であり、材料・プロセス両面からのアプローチが期待されている。ここではロジック系とメモリ系について、おのおのの開発状況を述べる。

#### 6.1 ロジック系デバイスの配線技術

配線抵抗の低減については、配線金属を従来のアルミニウム(Al)から低抵抗の銅(Cu)に変更する革新が $250 \sim 180$  nm世代でなされた29)。以来Cu配線はロジック系LSIに標準的な技術となった。45 nm世代以降のCu配線で予想される大きな課題は、寸法縮小に伴って顕著になるEM(Electro Migration)やSIV(Stress Induced Voiding)が導通不良を引き起こすことをいかに抑えるかである。解決策は幾つかあるが、中でもCuに少量の異種金属(Mn,Mg,Ni,Al,Agなど)を添加するCu合金はプロセスを大きく変更せずに配線を長寿命化できる技術として期待されている300)。

線間容量の低減については ,Low-k 低誘電率 )絶縁膜を配線間に配置すればよい。Low-k絶縁膜の導入はCu配線よりもや遅れて本格化し , $180 \sim 65$  nm世代で従来の酸化シリコンk SiO2 )膜 比誘電率k=4.1 )に代わってLow-k絶縁膜 比誘電率k=2.7  $\sim$  3.7 )が採用された。今後も世代ごとにk値を下げる必要があり ,45 nm世代以降は現在のLow-k絶縁膜を多孔質化したポーラスLow-k絶縁膜 k< 2.5 )が主流になること

図9 Boron極浅接合のSIMSプロファイル

表面測定では、一次元素のノックオンにより表面近傍での濃度プロファイルがひずんで測定される。

注:略語説明 ken(Effective k-value)

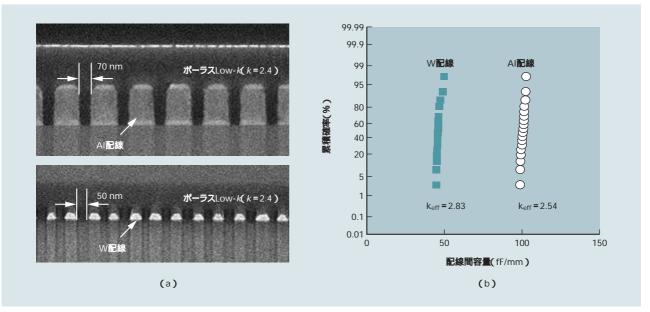

図10 ポーラスLow-k絶縁膜を用いたAI, W配線の断面(a)と, 配線間容量の累積確率分布(b)

50 nm世代以降の加工寸法を持つA(、アルミニウム)配線およびW( タングステン)配線を塗布型ポーラスLow-k絶縁膜 k=2.4 で埋め込んだ。従来のSiO:絶縁膜を使用した場合に比べて30%以上低い配線容量を実現できる。

が予想される。このような多孔質化は、Low-k絶縁膜の各種プロセス耐性や絶縁信頼性<sup>31)</sup>を大幅に低下させる。特に機械強度の低下は深刻で、Low-k絶縁膜に大きな物理的ストレスが加わるCMP( Chemical Mechanical Polishing )平坦(たん) 化工程やパッケージング工程で膜の剥(は)がれやクラックが発生する。このため、ポーラスLow-k絶縁膜を高強度化する材料設計<sup>32)</sup>のほか、紫外( UV )光や電子線( EB )を用いた膜の改質技術<sup>33)</sup>が積極的に提案されている。

#### 6.2 メモリ系デバイスの配線技術

コスト競争力が重視されるDRAMやフラッシュメモリなどのメモリ系デバイスでは ,高価なCu/Low-A配線プロセスの導入は見送られてきた。安価なAl/SiO2配線を延命しようとする動きは現在でも根強いが ,50 nm世代前後を境にして技術的限界が見えてくると予想される<sup>34</sup>。

第一の限界はAI配線の加工限界である。AIをドライエッチング加工する際の残渣(さ)は微細化とともに発生頻度が高くなり、歩留り低下の大きな要因となる。そこで一部のDRAM製品では、ドライエッチング残渣の心配がなく、微細化が容易なCu配線がすでに採用されている。今後コスト面の懸念さえ払拭(ふっしょく)されれば、Cu配線化が一気に加速する可能性も否定できない。

第二の限界はSiO:絶縁膜による埋め込み特性と配線間容量の限界である。ますます配線間のギャップが狭間隔かつ高アスペクトになるため、従来のプラズマを利用したSiO:成膜法

では埋め込むことができなくなるほか、配線間容量の増大も許容できなくなる。この問題を解決するために、日立製作所は日立化成工業株式会社と共同で高い埋め込み特性を持つ塗布型のポーラスLow-k絶縁膜(k=2.4)を開発した35(図10参照)。開発したLow-k膜は高い平坦化特性や800 に達する耐熱性もあわせ持ち、ビット線としてのタングステン(W)配線やPMD(Pre-Metal Dielectric)層などAl配線以外への適用も想定している。

#### 7.おわりに

ここでは、2007年現在のシリコン半導体デバイスの研究開発状況について、ロードマップの示すテクノロジーブースタを中心にして述べた。

これらは、性能向上を維持するため必要な技術であるが、多くのブースタ開発が予測に比べ遅れてきている。スケーリングによらない技術開発の難しさを改めて示しているように思える。

これはスケーリングの延長が困難となる今後のULSIデバイスでは、これまでのロードマップの範疇(ちゅう)を超えた、多様性が求められ、SoC(System on a Chip)に代表される多品種デバイスを集積する混載技術が重要になることを示唆しているものと考えられる。不揮発性メモリや、RF(Radio Frequency)用の受動素子、またシリコン光素子といったデバイスの混載に向けた研究開発を推進していく考えである。

#### 参考文献など

- 1) ITRS ,http://www.itrs.net/

- 2) D. Hisamoto ,et al.:IEEE Trans. Electron Devices ,vol.38 ,p.1419 (1990)

- 3) D. Hisamoto ,et al.:IEEE Trans. Electron Devices ,vol.47 ,p.2320 (2000)

- 4) F. Yang ,et al.: IEDM Tech. Dig. , p.255(2002)

- 5 ) H. Shang ,et al.: VLSI Symp. ,p.54(2006)

- 6) H. Kawasaki ,et al.: VLSI Symp. ,p.70(2006)

- 7) J. Bhavnagarwala ,et al.:IEEE J. Solid-State Circuits ,vol.36 ,p.658 (2001)

- 8) P. A. Stolk ,et al.:IEEE Trans. Electron Devices ,vol.45 ,p.1960 (1998)

- 9) J. Hubbard ,et al.: J. Mat. Res. ,11 ,p.2757(1996)

- 10) W. Peacocket, et al.: J. Appl. Phys., 92, p.4712(2002)

- 11) T. Kawahara ,et al.:Mat. Res. Soc. Symp. ,Proc. ,745 ,p.155 (2003)

- 12 ) S. Saito ,et al.: J. Appl. Phys. ,vol.98 ,p.113706(2005)

- 13) K. Torii, et al.: IEEE Trans. Electron Devices, vol.53, p.323(2006)

- 14) C. C. Hobbs ,et al.:IEEE Trans. Electron Devices ,vol.51 ,p.971

- 15 ) K. Shiraishi, et al.: VLSI Symp., p.108(2004)

- 16 ) Y. Shimamoto, et al.: VLSI Symp., p.132(2005)

- 17 ) M. Suzuki ,et al.:IEDM Tech. Dig. ,p.39(2005)

- 18 ) T. Hayashi ,et al.: IEDM Tech. Dig. ,p.247(2006)

- 19 ) K. Takahashi ,et al.:IEDM Tech. Dig. ,p.91(2004)

- 20) K. Shiraishi ,et al.:IEDM Tech. Dig. ,p.445(2005)

- 21 ) A. Shima ,et al.: VLSI Symp. ,p.174(2004)

- 22) T. Ito, et al.: Ext. Abst. of SSDM, p.182(2001)

- 23 ) D. Jacobson ,et al.: Ext. Abst. of IIT ,p.300(2000)

- 24 ) V. N. Faifer ,et al.: J. Vac. Sci. Technol. ,B24(1),p.414(2006)

- 25 ) C. L. Petersen ,et al.: Appl. Phys. Lett. ,77 ,p.3782(2000)

- 26 ) A. Shima et al.: J. Appl. Phys. Vol.89, No.6, p.3458(2001)

- 27 ) P. D. Wolf, et al.: J. Vac. Sci. Technol., B18(1), p.540(2000)

- 28 ) Y. Hayashi: Proc. IITC , p.145(2002)

- 29 ) D. Edelstein ,et al.: IEDM Tech. Dig. ,p.773(1997)

- 30 ) J. Koike ,et al.: Proc. IITC ,p.161(2006)

- 31 ) D. Ryuzaki ,et al.: IEDM Tech. Dig. ,p.949(2004)

- 32) 桜井,外:超LSI用低誘電率層間絶縁膜材料HSG-255,日立化成テクニカルレポート42号,p.49(2004)

- 33 ) T. Furusawa ,et al.: Proc. IITC ,p.45(2005)

- 34) K. Kin: IEDM Tech. Dig., p.333(2005)

- 35 ) D. Ryuzaki ,et al.: VLSI Symp. ,p.136(2006)

#### 執筆者紹介

久全 ス 1986年日立製作所入社,中央研究所 ULSI研究部 所属 現在,新構造,新材料を用いた微細MOSデバイスの研究 開発に従事 工学博士 応用物理学会会員,IEEE会員

龍崎 大介 1999年日立製作所入社,中央研究所 ULSI研究部 所属 現在,LSI用配線材料・プロセスの研究開発に従事 応用物理学会会員

杉井 信之 1988年日立製作所入社,中央研究所 ULSI研究部 所属 現在,ひずみSiを用いたMOSFETの研究開発に従事 工学博士 応用物理学会会員

島 明生 1995年日立製作所入社,中央研究所 ULSI研究部 所属 現在,Si-LSI材料・プロセスの研究開発に従事 IEEE会員,MRS会員

鳥居 和功 1988年日立製作所入社 ,中央研究所 ULSI研究部 所属現在 ,Si-LSI材料・プロセス ,および ,SiCパワーデバイスの研究開発に従事工学博士 応用物理学会会員 ,IEEE会員