#### **Featured Articles**

# イノベイティブR&Dレポート 2014

# 環境放射線による電子装置の ソフトエラー・障害対策の現状と取り組み

伊部 英史

鳥羽 忠信

新保 健一

Ibe Eishi

Toba Tadanobu

Shimbo Ken-ichi

上薗 巧

谷口 斉

Uezono Takumi

Taniguchi Hitoshi

半導体デバイスや電子装置のソフトエラー・障害の研究の歴史は、DRAMのα線ソフトエラーまでさかのぼることができる。その後、環境中性子線によるソフトエラーはSRAMで深刻化し、論理回路や車載マイコンまで拡大するとともに、新たな障害モードも頻出した。これらはソフト

エラー研究の大きなパラダイムシフトと言える。

それらの障害への対策も進展しているが、将来、さまざまな分野においてさらなる技術革新が起こるにつれ、環境放射線の影響はより深刻になっていくと考えられる。機能安全の確保のため、一層の技術開発が求められている。

#### 1. はじめに

半導体デバイスの信頼性における最大の問題の一つは、放射線起因のソフトエラー問題である。古くはパッケージに不純物として含まれる核物質から発生する $\alpha$ 線が、DRAM (Dynamic Random Access Memory) のソフトエラーの原因として大きな問題となり、 $^{232}$ Th (トリウム)をはじめ、 $\alpha$ 線を放出する不純物をパッケージ材料から低減するなど、さまざまな対策を施して1990年代初めには鎮静化した。ところが、1990年代に半導体デバイスが100nm以下まで微細化し、わずかな電荷(以下、「臨界電荷量」

と記す。)でデータが反転するようになると、銀河系中心核から飛来する高エネルギー宇宙線(陽子など)起源で、大気中の窒素・酸素の原子核と核反応を起こして発生する環境中性子線起因のソフトエラーがSRAM(Static Random Access Memory)で顕在化するようになった<sup>1)</sup>。以来、問題は論理回路に広がり、高エネルギー中性子以外の環境放射線の影響も現れるなど、複雑化の一途をたどり、将来的な予測も困難になりつつある。

$\alpha$ 線ソフトエラーの発見以来のソフトエラー研究の歴史を**表1**に示す。われわれの見解では、ソフトエラー研究は

#### 表1 ソフトエラー研究の歴史

1979年のDRAMの $\alpha$ 線ソフトエラー発生以来,環境中性子線によるSRAMのソフトエラー,ロジック回路や,車載マイコンへのソフトエラー問題の広がり,さまざまな障害モードの顕在化など,ソフトエラー研究は数多くのパラダイムシフトを経験してきた。

| 西暦年代        | パラダイムの特徴                                                                                                                                                                                                                                               | 出来事                                                                                | SRAMの<br>最小加工寸法 | SRAM集積度<br>(ビット) |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|------------------|

| 1979~1990初め | <ul><li>DRAMのα線ソフトエラーの顕在化</li><li>DRAMのα線ソフトエラー対策完了</li></ul>                                                                                                                                                                                          | ● Mayによる α 繰り ノトエフー発見(1979年)                                                       |                 | < 64 k           |

| 1990~2000   | ● SRAMの環境中性子線起因のソフトエラー率がDRAMを凌<br>駕 (りょうが) (伊部,1999年)                                                                                                                                                                                                  |                                                                                    |                 | 128 k-4 M        |

| 2000~2005   | <ul><li>SRAMのMCU問題が顕在化(伊部, 2004年)</li><li>バイポーラモードのソフトエラーモード発見(同上)</li><li>論理回路のSET問題拡大</li></ul>                                                                                                                                                      | <ul><li>・JESD89発行(2001年)</li><li>・半導体デバイス平坦化技術がBPSGからCMPに(熱中性子問題いったん鎮静化)</li></ul> | 90 nm           | 8 M              |

| 2006~2009   | ● メモリのソフトエラー問題原則的に解決 (伊部, 2006年)<br>● FFのMNT問題対策進展                                                                                                                                                                                                     | ● JESD89A発行 (2006年)<br>● AEC Q100 G (2008年)                                        | 65 nm           | 16 M             |

| 2010~       | <ul> <li>空間冗長系無力化 (DICE/TMR)</li> <li>車載マイコンの耐性基準強化</li> <li>地上の電子装置でパワー/コストイフェクティブなソフトエラー耐性向上策が最優先課題に</li> <li>高エネルギー中性子以外の環境放射線ソフトエラー問題への懸念拡大</li> <li>ISO26262発行 (2011年)</li> <li>IEC62396 (進行中)</li> <li>クラウド/エクサスケールコンピューティング/ビッデータ時代に</li> </ul> |                                                                                    | < 40 nm         | > 32 M           |

注:略語説明 DRAM (Dynamic Random Access Memory),SRAM (Static Random Access Memory),MCU (Multi-cell Upset),SET (Single Event Transient),FF (Flip-flop),MNT (Multi-node Transient),DICE (Dual Interlocked Storage Cell),TMR (Triple Modular Redundancy),JESD (JEDEC Standard),BPSG (Boron Phosphorus Silicon Glass),CMP (Chemical Mechanical Polishing),ISO (International Organization for Standardization),AEC (Automotive Electronics Council),IEC (International Electrotechnical Commission)

1979年以来、4回のパラダイムシフトを経験してきている。

1つ目はDRAMのα線ソフトエラー問題の発生から終息 までである。2つ目は高エネルギー環境中性子線起因のソ フトエラー問題のSRAMでの顕在化である。3つ目はa線 ソフトエラーではほとんど見られなかったMCU (Multicell Upset) \*\*1) の顕在化であり、特に従来では見られなかっ たバイポーラモード\*\*2)がその引き金となっている。4つ 目は、論理回路でのSET (Single Event Transient, フォー ルト) 問題の拡大が挙げられる。さらに5つ目として、現 在, 論理回路における DMR (Dual Modular Redundancy: 二重冗長系), TMR (Triple Modular Redundancy:三重冗 長系) や、FF (Flip-flop) の DICE (Dual Interlocked Storage Cell) \*\*3) など空間冗長系のMNT (Multi-node Transient) \*\*4) による無力化と、微細化に伴い、臨界電荷量が低減し、中 性子以外の環境放射線(低エネルギー中性子、ミューオン など) による影響への懸念が広がっていることや, α線起 因のソフトエラー問題が再燃していることにも注意が必要 である<sup>2), 3)</sup>。

### 2. 環境放射線による電子装置の障害のメカニズム

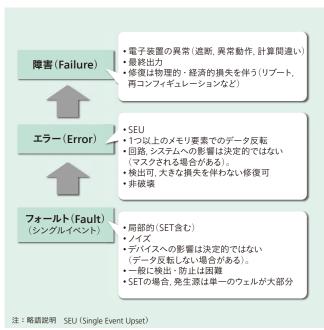

電子装置の障害は、ノイズや欠陥という形でのフォールトを起源と考えるのが一般的である(図1参照)。フォールトの一部がDRAM、SRAMやFFなどのメモリ要素に捕捉されてデータが反転すると、そのメモリ要素のエラーとなる。エラーは電子装置の最終出力まで伝搬する過程で多

#### 図1 装置障害に至る現象の階層構造

電子装置の障害は、ノイズや欠陥という形でのフォールトを起源とし、フォールトの一部がDRAM、SRAMやFFなどのメモリ要素に捕捉され、データが反転するとそのメモリ要素のエラーとなる。エラーは電子装置の最終出力まで伝搬する過程で多くのものが消失する(マスクされる)が、最終処理データに異常が発生すると障害(Failure)となる。

くのものが消失する(マスクされる)が、最終処理データに異常が発生すると障害(Failure)となる。

エラーの段階では、さまざまな手法によって予防・修復できるが、障害の段階まで至ると、物理的・経済的な損失なしには修復が困難になる。特に、安全が優先される航空・乗用車などの real-time system では人的・経済的損失につながるため、フォールトやエラーの段階で兆候を確実に捉え、障害を未然に防ぐか、損失を最小限にとどめる必要がある⁴)。このように、電子装置を使用する分野ごとにフォールト、エラー、障害の検出レベル・手法、対策の内容が異なってくるのは当然のことである。分野ごとの最近の関心対象を障害の形態とともにまとめたものを表2に示す。

放射線ソフトエラーの場合は、二次宇宙線としての中性子や陽子がデバイス材料と核反応を起こして発生するさまざまな荷電粒子や、もともと地上に飛来する電荷を持った荷電粒子[電子、陽子、ミューオン、パイ中間子、He(ヘリウム)原子核]が半導体デバイスの鋭敏な部分を通過し、電子・正孔対を発生させる現象(直接電離)に起因する(図2参照)。発生した電荷はノイズ(フォールト)の原因になるが、基本的にトランジスタ構造を納めるウェル\*5)ないしは基板内でのみ発生する。特にCMOS(Complementary Metal-oxide Semiconductor)のウェルの場合は、単一ウェル内での発生がほとんどであると考えられている30。

電荷収集モードの場合は、発生した電荷が記憶ノードを 形成する拡散層を通過し、拡散層の周りに形成される空乏 層およびその近傍に発生した電荷をファネリング\*60と呼 ばれるメカニズムによって一定量 (臨界電荷量)以上収集 すると、保持している「1」または「0」のデータが反転し、 エラーとなる。

バイポーラモードでは、発生した正孔がトリプルウェル構造のように1か所に残留しやすい構造に起きやすく、特定の部位の電位が上昇してその周辺のトランジスタをまとめて反転させる現象であり、MCU、MNTの主因の一つとなる。

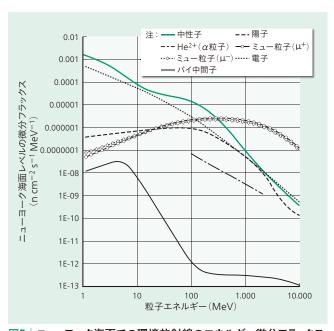

ニューヨーク海面での環境放射線のフラックスの計算値

<sup>※1)1</sup>個の粒子の半導体デバイスへの入射で複数のメモリセルのデータが同時に反転する現象。

<sup>※2)</sup> デバイスの一部の電位が高くなる現象。その範囲に含まれるセルがエラーを起 こしやすくなる。

<sup>※3)</sup> 二重冗長化FF。2つの冗長ノードの一方が反転しても復旧する。

<sup>※4)</sup>複数の論理ノードに、同時にフォールトが発生する現象。

<sup>※5)</sup> ソース、ドレイン、ゲートなどを作りこむ領域名をウェル (井戸) と称し、pMOSFET (Metal-oxide Semiconductor Field Effect Transistor) 構造とnMOSFET 構造の2種類がある。図2の例はトリプルウェル構造のnMOSFETであり,p-ウェルの周囲をn極性の半導体で取り囲む構造になる。p極性とn極性の半導体が接する部分をpn接合と呼ぶ。

<sup>※6)</sup>空乏層(pn接合)内で発生した電子・正孔対が、トランジスタがオフの状態のときの空乏層内の強い電界により、電子は拡散層へ流れ、正孔は空乏層外へ押し出された結果、もともとの空乏層の電界が外へ広がり、当初空乏層外にあった電子も拡散層へ収集する現象。漏斗になぞらえてファネリングと呼ばれる。

# 表2 産業分野ごとの環境放射線起因障害関心事象

放射線起因の装置障害の懸念は航空機,鉄道,ネットワーク,スーパーコンピュータ,車載機器,個人用電子機器などあらゆる産業分野に拡大している。

| 分野         | 機器               | 障害の原因        | 障害・問題の形態モデル                       |  |  |

|------------|------------------|--------------|-----------------------------------|--|--|

| 航空機        | X by wire        | SEU/SEL/SEFI | リブート,TMRの無力化                      |  |  |

| 鉄道         | IGBT             | SEB          | 破壞,停止                             |  |  |

| ネットワーク     | サーバ              | SEU/MCU/SEL  | データ破壊,リブート                        |  |  |

|            | ルータ              | SEU/MCU/SEL  | リブート,送信アドレス変化                     |  |  |

| イットソーク     | データセンタ           | SEU/MCU/SEL  | 冗長化による消費電力の増大                     |  |  |

|            | 電源 (DC-DC コンバータ) | SEB/SEL      | 破壞,停止                             |  |  |

| スーパーコンピュータ |                  | SDC          | 認知できない誤計算,冗長系による消費電力の増大           |  |  |

|            | Brake by wire    | SEU/MCU/SEL  | ブレーキ無反応・急停止                       |  |  |

|            | ステアリング           | SEU/MCU/SEL  | ハンドル固着・異常回転                       |  |  |

| 車載機器       | エンジン制御           | SEU/MCU/SEL  | 急加速,無反応                           |  |  |

| 平          | CAN              | SEU/MCU/SEL  | 機器間の連携ミス                          |  |  |

|            | GPUを用いた歩行者検知     | SEU/MCU/SEL  | 歩行者検知に失敗して衝突、あるいは誤検知して不必要で危険な回避動作 |  |  |

|            | IGBT             | SEB          | 破壞,停止                             |  |  |

|            | スマートフォン          | SEU/MCU      | フリーズ,メール送信先ミス,個人情報消失              |  |  |

| 個人用電子機器    | タブレットPC          | SEU/MCU      | フリーズ,メール送信先ミス,個人情報消失              |  |  |

|            | デスクトップPC         | SEU/MCU      | フリーズ,メール送信先ミス,個人情報消失              |  |  |

注:略語説明 IGBT (Insulated Gate Bipolar Transistor), DC (Direct Current), CAN (Controller Area Network), GPU (Graphics Processing Unit), PC (Personal Computer), SEL (Single Event Latch-up), SEFI (Single Event Functional Interrupt), SEB (Single Event Burnout), MCU (Micro Control Unit), SDC (Silent Data Corruption)

を図3に示す<sup>3)</sup>。微細化がさらに進展して臨界電荷量が小さくなると、ミューオン、陽子など発生電荷量は相対的に小さいが、中性子と同程度のフラックスを持つ粒子の影響

荷電粒子 n+拡散層@ Vcc 空乏層 n-ウェル 正孔 雷子 Deep n-ウェル Vcc ファネリング 空乡層 雷子 + 正孔 Deep n-ウェル  $V_{\rm cc}$ ファネリング

図2 | 荷電粒子による放射線ソフトエラーメカニズム(電荷収集モード) 中性子や陽子がデバイス材料と核反応を起こして発生するさまざまな荷電粒子や、地上にもともと飛来する電荷を持った二次宇宙線がデバイス内に電荷を発生させ、ソフトエラーの原因となる。

も現れる可能性があることを同図は示している。40 nm以下のプロセスでは,配線加工のためにボロン ( $B: \pi$ ウ素) 10を含むガスが用いられることが多く,これが配線層に高濃度で残り,低エネルギーの中性子との捕獲反応 ( $^{10}$ B+n $\rightarrow$   $^{7}$ Li+ $^{4}$ He) で発生する二次イオン  $^{7}$ Li,  $^{4}$ Heによってソフトエラーが発生することも報告されている $^{50}$ 。ワード線上一直線のMCUは99%以上隣接2ビットであるため,メモリについてはMBU (Multiple Bit Upset:同一ワードのMCU) はECC (Error Check and Correction) と 3ビット以上同一ワードのビット間隔を空けるインターリーブと

図3 | ニューヨーク海面での環境放射線のエネルギー微分フラックス 単位エネルギー幅当たりの粒子入射率を示す。中性子は、核反応によって発生した二次荷電粒子のみが装置障害の原因になるが、電子、ミュー粒子  $(\mu^+)$ 、 $\mu^-$ )、パイ中間子、 $He^{2+}$  ( $\alpha$ 粒子) は直接電離効果によって装置障害を起こしうる。陽子は、核反応と直接電離効果の両方の現象を引き起こす。

の併用によって抑制できることをわれわれが初めて明らかにした<sup>6)</sup>。一方、ロジックデバイスの場合は、同一ウェル内で同一ゲートの複数入力が配置されることがあるため、対策が極めて困難になる。特に、ソフトエラーが起きないとされてきたDICE系のFFでも2ノードが同時にエラーになる場合が多発し、微細化に伴い、耐性が劣化すると予測されている<sup>7)</sup>。

さらに、FFを駆動するクロック系や、セット/リセット系などのグローバル制御系からの環境中性子線によるノイズ起因で複数のFFがエラーになるモードも顕在化しており<sup>8)、9)</sup>、ロジックのエラー対策が急務となっている。

# 3. 装置対策の一例

ネットワークに使用されるルータも、環境中性子への対策が必要な機器の一つである。ルータにはCPU (Central Processing Unit)、DRAM、SRAM、FPGA (Field Programmable Gate Array) などさまざまなチップが1枚のボード上に実装されているが、最終的に装置の障害対策に最も効果があるボードの部位を数値シミュレーションなどで求める手法は現存しない。

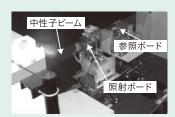

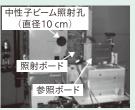

そこで、われわれは、高エネルギー加速器を用いた中性子源である東北大学のCYRIC (Cyclotron and Radioisotope Center)を利用し、ルータのボードに10 cm角に絞った中性子ビームを部位を選択して照射し、装置障害(システムダウン)に最も影響が大きい部位がSRAMチップであると特定した。これにより、高速な処理の必要のないSRAMのセルをECCで保護したDRAMで置き換え、装置全体の市場での障害率の一桁低減を達成した100。

電子装置に関するユーザーの要求は、低消費電力化、高速化、高信頼化を軸に極めて多様化しており、こうしたさまざまな要求にフレキシブルに対応できるFPGAが、極めて多くの産業分野で使用されるようになっている。しかし、FPGAの論理を構成するコンフィギュレーションメモリ(CRAM: Configuration Random Access Memory)にはソフトエラー耐性が脆(ぜい)弱な SRAM が用いられており、そこで発生したソフトエラーは装置自体の動作を変えてしまうため、対策が不可欠となる。

通常、CRAMで検出されたエラーは、別途フラッシュメモリなどに保存していたデータを用いて再構成(Reconfiguration)するが、その間は装置を止めることになり、real-time systemではTMRなどの冗長系を用いることが必須になる。冗長系を構成した場合でも、プロセッサを駆動するクロックにフォールトが発生すると全体の障害に至るため、鉄道系システムなどでは、クロック系も位相をずらすなどのさまざまな工夫が施されている⁴)。

#### 図4 RCNPでの耐中性子ソフトエラーFPGAボードの設置例

耐中性子ソフトエラーFPGA (Field Programmable Gate Array) ボードをRCNP (Research Center for Nuclear Physics) の高エネルギー中性子ビームラインに設置した状況を示す。

われわれは、CRAMの一部のみを再構成 (Partial Reconfiguration) して停止時間を短縮したり、ECCを用いて直接ソフトエラーを修復したりする技術の開発を進めている。

TMRを構成する1モジュールにソフトエラーが発生した場合、そのモジュールを再構成しなければ、二重系のまま動作するリスクを負う。そこで、障害が発生したモジュールに対し、正常な2モジュールの動作速度はそのままで、故障モジュールの再構成が終了したのち、そのモジュールの動作速度を通常より速くし、最終的に3モジュールで同期をとることで、全体の動作を止めることなくTMR動作に復帰する手法を開発した。この手法は、すでにRCNP(Research Center for Nuclear Physics)、およびCYRICでの高エネルギー中性子照射実験で検証済みである110。当該ボードをRCNPの高エネルギー(最大400 MeV)中性子ビームラインに設置した状況を図4に示す。

これらは対策の一例にすぎないが、ソフトエラー起因の 障害対策には脆弱部位(メモリ、FPGA、論理回路、クロック系、電源など)と障害メカニズムの見極めが重要である。

### 4. 環境放射線による電子装置障害の将来

ロジック回路の放射線ソフトエラーにはメモリと同様の対策が適用できず、エクサスケール $^{*7}$ のスーパーコンピュータやデータセンターでは消費電力の抑制が強く求められるため、二重系、三重系などの空間冗長系は今後採用されない方向にある $^{12),13}$ 。加えて、空間冗長系はMNTによって効果が低減するため、二重の意味で信頼性確保策としては推奨されない。

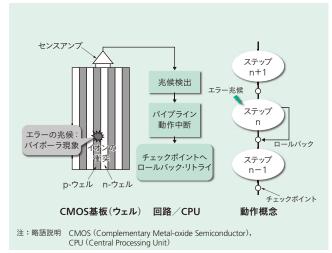

それに代わり、正しい実行結果の装置データを特定の時間間隔(チェックポイント)で保存し、エラーを検知した場合にチェックポイントに戻って(Rollback)再実行する(Replication)時間冗長系が有力視されている。

※7) 毎秒 $10^{18}$  回の命令を実行するスーパーコンピュータ。

図5 LABIR (Inter-layer Built-in Reliability) の適用例

ストライプ構造のp-ウェル, n-ウェルが並ぶCMOSデバイスにおいて, 単一ウェル内で発生したフォールトをウェル端で近接する同一極性のウェルとの電位差としてセンスアンプで検知し, 必要な場合にチェックポイントに戻り(Rollback), 再実行(Replication)する。

ロジックのエラーは検出が難しいため、エラーの兆候としてのフォールトを直接検出し、エラーとなる可能性が大きい場合は、時間冗長系による修復動作を実行する手法が注目され始めている。この手法の最初の提案となる筆者らのLABIR(Inter-layer Built-in Reliability)では、ウェル内で荷電粒子が通過したときに発生する電磁ノイズを検出し、時間冗長系で修復する<sup>14)</sup>(図5参照)。ウェルで発生する電磁ノイズは中性子照射実験で検証されており、類似の検出手法が提案されている<sup>15),16)</sup>が、二次イオンがデバ

イスを通過したときに発生する音響波を複数のSAW (Surface Acoustic Wave) デバイスで検知し、発生位置を MNTを含めて特定する手法も提案されている<sup>17)</sup>。

表1で見たように、微細化や新しいアプリケーションの 出現に伴い、シングルイベントによる障害はさまざまな形 で姿を変えてきており、その傾向は今後も続くと考えられ る。表3はさまざまな産業分野で今後の技術動向を思いつ くままに並べてみたものであるが、環境放射線によるシン グルイベントの影響は、根本的でシステマティックな対策 を講じなければ拡大する一方と思われる。

LABIRと同様の視点から、シングルイベント対策をデバイス任せにせず、回路、プロセッサ、OS (Operating System)、アプリケーションなどの電子装置を構成するすべての要素間の協調により、ディペンダビリティーを確保する試み (Cross-layer Reliability)が国際的に進展している 17/1, 18/1, 19/1 が、「協調」を実効的に機能させる仕組みを作りこむことが重要で、将来の鍵を握っていると言える。また、輸送系などの real-time system では、フォールトの位置周辺に修復の粒度を絞った「ミリ秒修復」が大きなチャレンジになる。さらに、現在身近な乗用車、スマートフォン、家庭電化製品、医療機器は、センサネットワーク、遠隔操作・診断などについて、将来まったく違った利用法に発展していく可能性が高く、それに応じて発生するであろう新しい障害モードに備える必要がある。

## 表3 | 今後の技術発展で環境放射線の影響を考慮すべき事項

将来のさらなる技術革新では、微細化、低電力化、複雑化が一層進むことが必然的であり、環境放射線の影響がより深刻になりうる。各産業分野の技術革新の 方向と、その方向で備えるべき耐環境放射線技術開発、対応すべき国際標準をまとめた。

| 産業分野       | 電子装置     | 技術開発の方向                                          | 従来の障害対策              | チャレンジ                                                             | SEE関連の国際標準                                          |  |

|------------|----------|--------------------------------------------------|----------------------|-------------------------------------------------------------------|-----------------------------------------------------|--|

| 輸送         | 航空機      | 軽量化,X-by-wire                                    | 高耐性デバイス使用, TMR       | • ミリ秒修復                                                           | IEC62396                                            |  |

|            | 鉄道       | 高速化                                              | 電源の多重化               | Digital wireless train control                                    | IEC62278, IEC62279, IEC62280, IEC62425              |  |

|            | 乗用車      | 軽量化,X-by-wire,電子化,GPU                            | デュアルコアのロックス<br>テップ動作 | ● ミリ秒修復<br>● Perfect fail-safe                                    | ISO26262,AEC-Q100-rev.G,<br>Euro NCAP rating review |  |

| 電力         | 原子力      | 廃炉                                               | -                    | • 耐放射線性ロボット, センサー                                                 | IEC61513                                            |  |

|            | 再生可能電力   | 太陽・風力・地熱・波力                                      | -                    | -                                                                 | -                                                   |  |

|            | 送電       | スマートグリッド, UHV                                    | -                    | ● SEB対策                                                           | IEC60038                                            |  |

| スーパーコンピュータ |          | 超高速化 (Exaflop), 大容量化 (100<br>ベタバイト), 低消費電力       | ECC, TMR, CRC, DMR   | ● 100%SDCの検出と修復<br>● Cross-layer Reliability/LABIR<br>● 高耐性ソフトウェア | -                                                   |  |

| ネットワーク     | データセンタ   | 大容量化 (100ペタバイト), 低消費<br>電力, クラウドコンピューティング        | ECC, TMR, CRC, DMR   | <ul><li> フォールトアウェアシステム</li><li> 障害の高速隔離</li></ul>                 | ISO27001<br>DMTF Standards                          |  |

|            | サーバ      | 仮想化, 低消費電力                                       | ECC, TMR, CRC, DMR   | Cross-layer Reliability/LABIR                                     | -                                                   |  |

|            | ルータ      | 高機能化,低消費電力                                       | ECC, TMR, CRC, DMR   | Cross-layer Reliability/LABIR                                     | _                                                   |  |

| メディア       | デスクトップPC | クラウドコンピューティング                                    | 再起動                  | • セキュリティ高度化                                                       | -                                                   |  |

|            | タブレットPC  | 軽量化,低消費電力,高速化                                    | 再起動                  | • セキュリティ高度化                                                       | -                                                   |  |

|            | スマートフォン  | <ul><li>● 高速化</li><li>● デジタル家電の遠隔操作</li></ul>    | 再起動                  | <ul><li>セキュリティ高度化</li><li>遠隔操作の安全確保</li></ul>                     | -                                                   |  |

| 家電         | ロボット     | <ul><li> 家事全般</li><li> 介護</li><li> 対話型</li></ul> | _                    | <ul><li>◆状況認識による適正動作</li><li>・複雑,安全動作</li></ul>                   | _                                                   |  |

| 医療機器       | 放射線セラピー  | •陽子,中性子による腫瘍治療                                   | -                    | -                                                                 | IEC62304                                            |  |

注:略語説明 UHV [Ultra High Voltage (1,100 kV)], ECC (Error Check and Correction), CRC (Cyclic Redundancy Check), DMR (Dual Modular Redundancy), SEE (Single Event Effect), NCAP (New Car Assessment Programme), DMTF (Distributed Management Task Force)

# 5. おわりに

電子装置の障害に関連して、IEC61508<sup>20)</sup> や、車載機器に向けたISO26262<sup>21)</sup> などの機能安全に関する国際規格が発行され、信頼性は、性能や消費電力と並んで電子装置が満たすべき基本仕様としてますます重要になっている。

半導体デバイスの微細化は今後もさらに進むことは確実と言えるため、機能安全の確保には一層のチャレンジが必要である。

#### 謝辞

本研究の実施にあたっては、CYRICでの中性子照射実験に関し、東北大学の中村名誉教授、馬場名誉教授、酒見教授より、RCNPでの中性子照射実験に関し、大阪大学の畑中教授、福田准教授より、多くのご指導とサポートを頂いた。関係各位に深く感謝の意を表する次第である。

### 参考文献

- 1) E. Ibe: Current and Future Trend on Cosmic-Ray-Neutron Induced Single Event Upset at the Ground down to 0.1-Micron-Device, The Svedberg Laboratory Workshop on Applied Physics, Uppsala, May, 3, 2001, No.1

- G. Gasiot, et al.: Alpha-Induced Multiple Cell Upsets in Standard and Radiation Hardened SRAMs Manufactured in a 65 nm CMOS Technology, TNS, 2006, Vol.53, No.6, pp. 3479-3486

- E. Ibe, et al.: Fault-based reliable design-on-upper-bound of electronic systems for terrestrial radiation including muons, electrons, protons and low energy neutrons, Int'l On-Line Testing Symposium 2012, Sitges, Spain, June 27-29, 2012, No.3.2

- 4) N. Kanekawa, et al.: Dependability in Electronic Systems-Mitigation of Hardware Failures, Soft Errors, and Electro-Magnetic Disturbances-, Springer, 2010

- S. Wen, et al.: Thermal neutron soft error rate for SRAMS in the 90NM-45NM technology range, IEEE Int'l Reliability Physics Symposium 2010, Anaheim, CA, May 2-6, 2010, No.SE5.1, pp. 1036-1039

- 6) E. Ibe, et al.: Spreading Diversity in Multi-cell Neutron-Induced Upsets with Device Scaling, 2006 CICC, San Jose, CA., September 10-13, 2006, pp. 437-444

- N. Seifert, et al.: Assessing the impact of scaling on the efficacy of spatial redundancy based mitigation schemes for terrestrial applications, IEEE Workshop on Silicon Errors in Logic - System Effects 3, Austin Texas, April 3, 4 (2007)

- 8) M. Cabanas-Holmen, et al.: Clock and Reset Transients in a 90 nm RHBD Single-Core Tilera Processor, IEEE Trans. Nucl. Sci. Vol. 56, No. 6, pp. 3505-3510 (2009)

- J. Loncaric: DOE's Exascale Initiative and Resilience, IEEE Workshop on Silicon Errors in Logic - System Effects 7, Champaign-Urbana, Illinois, March 29-30, 2011

- E. Ibe, et al.: Quantification and mitigation strategies of neutron induced softerrors in CMOS devices and components, Int'l Reliability Physics Symposium 2011, Monterey, California, April 10-14, 2011, No.3C.2

- 11) 鳥羽,外:FPGAにおける中性子ソフトエラーからの無停止復旧方式,電子情報通信学会和文論文誌(投稿中)

- 12) B. Falsafi: Reliability in the Dark Silicon Era, 17th IEEE Int'l On-Line Testing Symposium 2011, Athens, Greece, July 13-15, 2011, xvi

- E. Ibe, et al.: LABIR: Inter-LAyer Built-In Reliability for Electronic Components and Systems, IEEE Workshop on Silicon Errors in Logic - System Effects 7, Champaign-Urbana, Illinois, March 29-30, 2011

- S. A. Bota, et al.: Cross-BIC architecture for single and multiple SEU detection enhancement in SRAM memories, IEEE 16th Int'l On-Line Testing Symposium 2010, Corfu Island, Greece, July 5-7, 2010, No.7.1, pp.141-146

- 15) E. H. Neto, et al.: A built-in current sensor for high speed soft errors detection robust to process and temperature variations, Proceedings of the 20th annual conference on Integrated circuits and system design, September 03-06, 2007, pp. 190-195

- 16) G. Upasani, et al.: Achieving Zero DUE for L1 Data Caches by Adapting Acoustic Wave Detectors for Error Detection, Int'l On-Line Testing Symposium 2013, Chania, Crete, July 8-10, 2013, No.5.2

- 17) N. Carter: Cross-Layer Reliability, IEEE Workshop on Silicon Errors in Logic System Effects 6, Stanford University, March 23-24, 2010

- 18) H. Quinn: Study on Cross-Layer Reliability, IEEE Workshop on Silicon Errors in Logic System Effects 7, Champaign-Urbana, Illinois, March 29-30, 2011

- G. Psychou, et al.: Cross-layer Reliability Exploration Proposal For Body Area Networks, IEEE Workshop on Silicon Errors in Logic - System Effects 8, Champaign-Urbana, Illinois, March 27-28, 2012, No.9

- 20) 田辺:機能によって安全を確保する「機能安全」の考え方を知る, Design Wave Magazine, 2006, December, pp. 20-26

- 21) R. Mariani: Designing Safe and Available Integrated Circuits According to Functional Safety Standards, IEEE Workshop on Silicon Errors in Logic System Effects 8, Champaign-Urbana, Illinois, March 27-28, 2012, No.1.1

### 執筆者紹介

#### 伊部 英史

日立製作所 横浜研究所 生産技術研究センタ 回路システム研究部 所属

現在、環境放射線起因の電子装置障害の評価・対策研究に従事 工学博士

IEEEフェロー, IEEE学会会員

#### 鳥羽 忠信

日立製作所 横浜研究所 生産技術研究センタ 回路システム研究部 所属

現在,フォールトトレラント設計研究に従事 電子情報通信学会会員

#### 新保 健一

日立製作所 横浜研究所 生産技術研究センタ 回路システム研究部 所属

現在、情報通信装置の高信頼性設計に従事

上薗 巧

日立製作所 横浜研究所 生産技術研究センタ 回路システム研究部 所属

現在,電子装置の高信頼性設計に従事 工学博士

IEEE学会会員

谷口 斉

日立製作所 横浜研究所 生産技術研究センタ 回路システム研究部 所属

現在、パワーデバイス・LSI電源の高信頼性設計に従事