# 200kHzスイッチング電源

# 200kHz Switching Power Supplies

電子装置は、AC100V、200V、又はDC-48Vの供給を受けて、各装置で必要な電圧を筐体下部に集中実装したDC-DCコンバータで変換している。近年、装置の低電力化、小形化とあいまって低雑音化の要望が強く、このコンバータを装置回路用の電子回路パッケージと同じ実装形態を取り、装置内の機能ブロックに分散実装する手法が多用され始めた。このため、小形、軽量を目的としたDC-DCコンバータを、変換周波数200kHzのスイッチングレギュレータの回路技術と、パワーMOS FETなどの高周波部品により実用化した。標準化したDC-DCコンバータシリーズのうち、 $60W(5V\cdot 12A)$ の電源の例では、保護回路を含めて電力・体積比55W/l、出力スパイク雑音 $60mV_{pp}$ である。

山田智久\* Tomohisa Yamada 湯川直俊\* Naotoshi Yugawa 石黒秀雄\* Hideo Ishiguro

#### ■ 緒言

電子交換機などの電子装置にLSIが導入され、装置の低電力化、小形化とともに、電源の小形、軽量化が要求されている。また、装置の機能の追加や増設などに対しても、電源は容易に実装できねばならない。

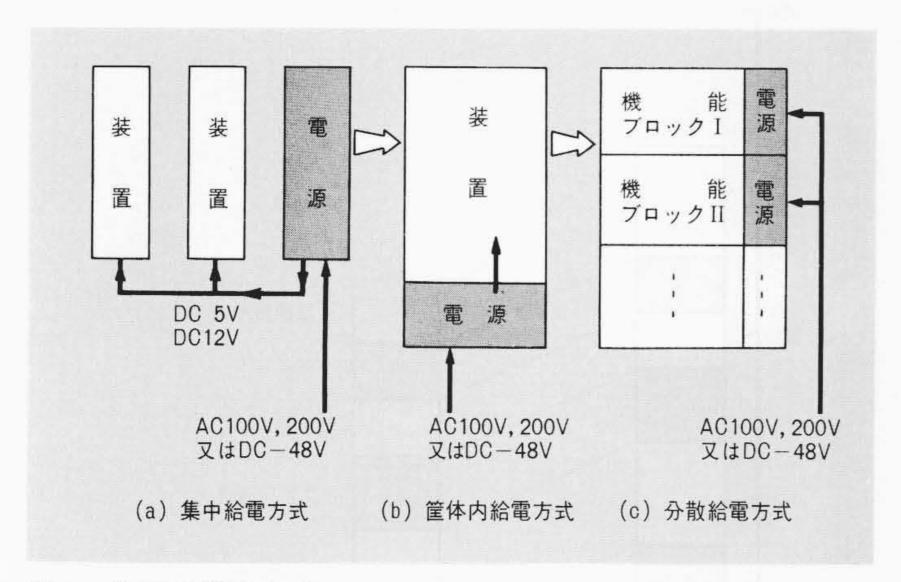

これにこたえるために、装置の機能ブロックに数十~百ワット級の電源を配置する分散給電方式が採用され始めている。この給電方式は、図1に示すように装置の機能ブロックに電源をもつもので、適当な出力容量の電源を標準化することにより、経済性、高品質が期待できる。また増設、保守性が優れ、給電設計も有利になる。

電源には、従来20~40kHzの変換周波数をもつスイッチングレギュレータが用いられたが、パワーMOS FET(Metal Oxide Semiconductor電界効果トランジスタ)などの高周波スイッチング部品が入手可能になり、より高速なスイッチングレギュレータの実現性が出てきた。この論文は、これらの高周波部品の採用により、変換周波数を200kHzまで高めたスイッチングレギュレータの実用化結果について述べるものである。

# 2 特長と構成

変換周波数を200kHzに上げることにより、小形、軽量化を 実現した。また、高速化により問題になる雑音と熱損失の増加を、部品選択と回路技術により低減した。

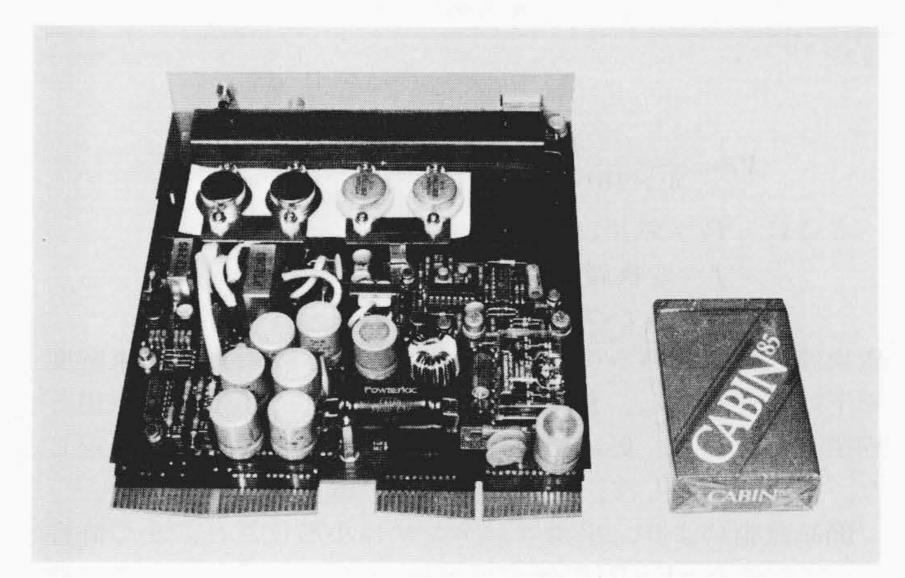

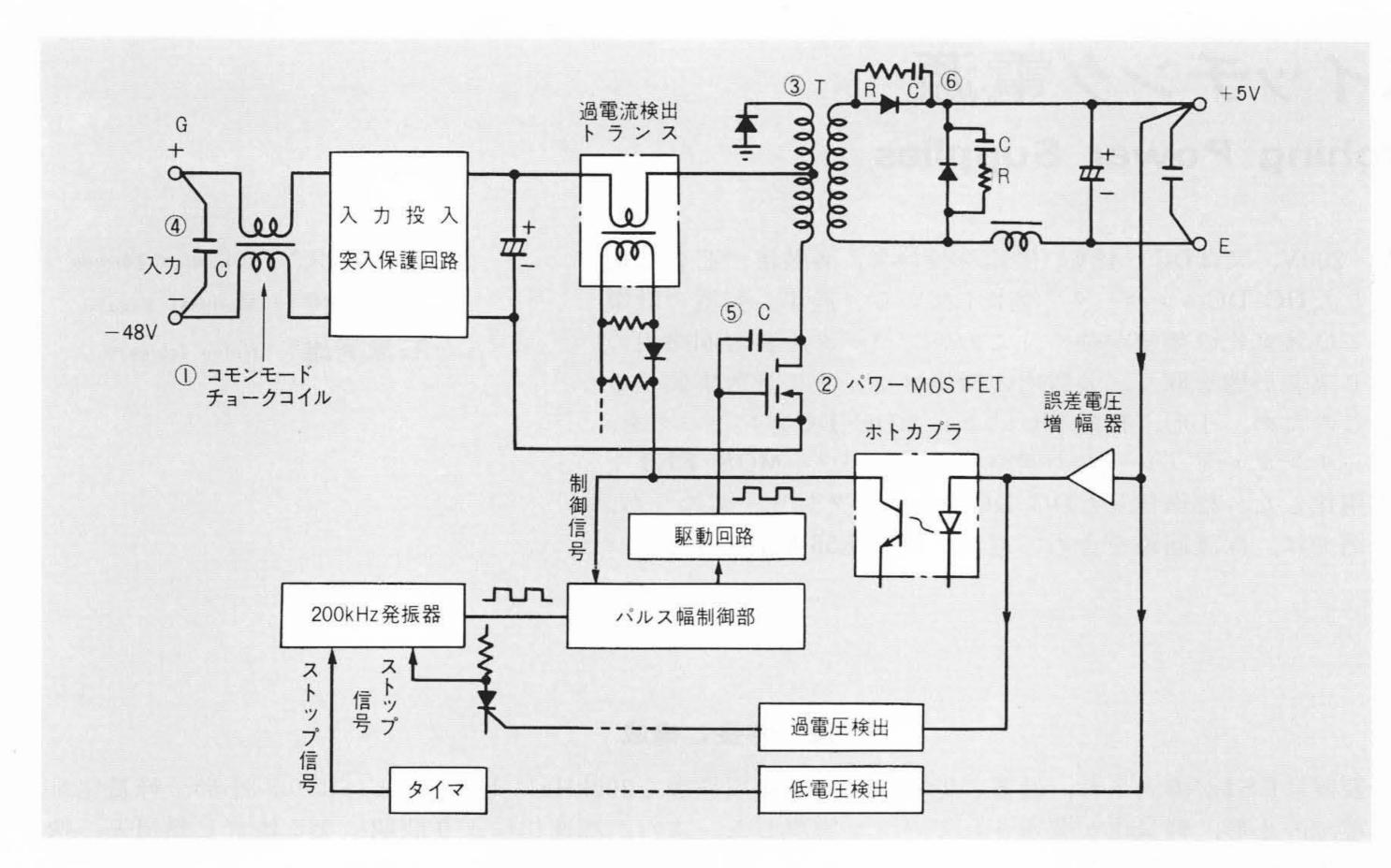

これらの特長をもつスイッチングレギュレータの外観を**図2**に示す。この電源はプラグイン構造のプリント板に**、図3**に示すスイッチングレギュレータ回路と,出力過不足電圧監視などの保護回路を搭載している。

主な仕様と標準化した電源の種類を表1に示す。

#### 図 高周波,小形化の検討

### 3.1 電気部品の小形化

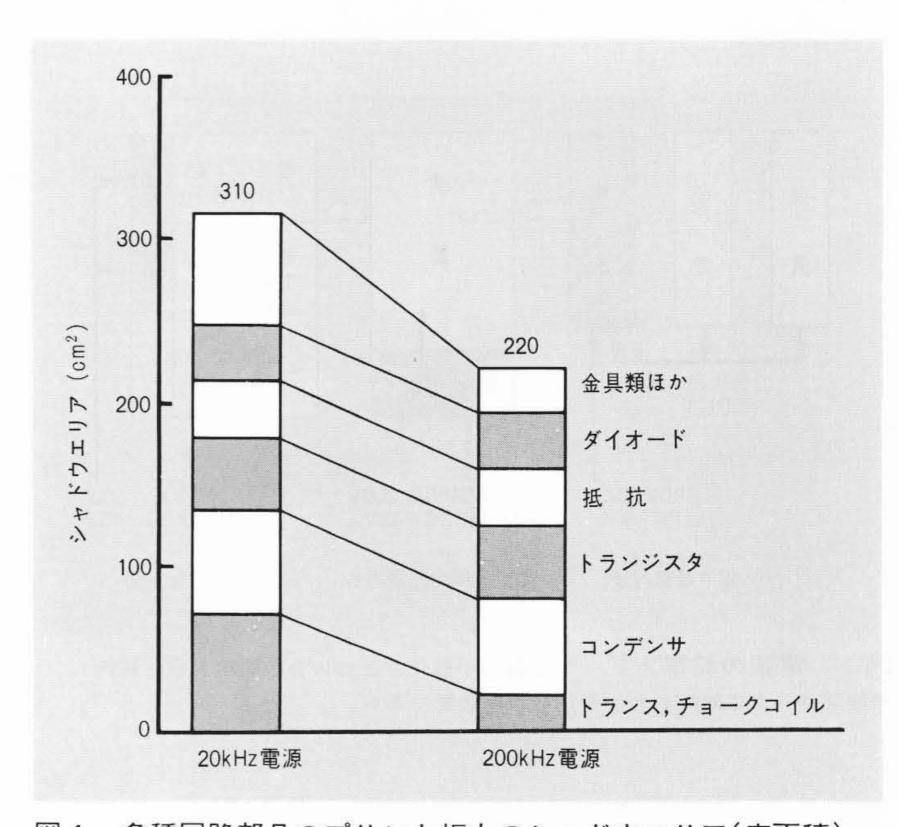

各部品のシャドウエリア(床面積)を**図4**に示す。左側の20 kHz電源はトランス、チョークコイル及びコンデンサのシャドウエリアが大であるため、これらの部品を小形化する必要がある。

トランス及びチョークコイルを小形化するには、次式に示すように変換周波数を高めることが必要である。すなわち、コアの体積Veは次の実験式から求められる。

図 | 電源の給電方式 装置の小形化とともに分散給電方式に移行し、機能ブロックに対応した小形化電源が必要である。

図 2 電源の外観 放熱板兼シールド板を外してある5V・12A,60W電源であり、薄形構造であることが分かる。プラグイン構造のプリント基板に200 kHzコンバータと各種保護機能を内蔵している。

<sup>\*</sup> 日立製作所戸塚工場

注:略語説明

G(グラウンド)

T(トランス)

C(コンデンサ)

R(抵抗)

E(アース)

パワー MOS FET(パワー

Metal Oxide

Semiconductor

電界効果トランジスタ)

図3 回路構成 回路 形式は、パルス幅制御方式 I石フォワードコンバータ であり、保護回路を内蔵す る。本図中の①~⑥は雑音 対策を配慮した部品(表2 参照)である。

表 I 200kHzスイッチング電源の種類と仕様 保護機能をもった各種の電源がある。

| 項目            | 8                  | 仕                                   | 様                        |                     |

|---------------|--------------------|-------------------------------------|--------------------------|---------------------|

| 周囲条件, 品質      | ● 温                |                                     | C −48V, ±<br>O∼40°C, I5∼ |                     |

| <b>売がたの様数</b> | 60W                |                                     | 100W                     |                     |

| 電源の種類         | 5V · 12A           | 12V • 5A                            | 24V · 2.5A               | 5V · 20A            |

| 寸    法        | 200                | 0×260×26(m                          | ım)                      | 200×260×<br>40(mm)  |

| 重量            |                    | 0.83kg                              |                          | 1.3kg               |

| 出 力 変 動       | ± 3                | %(含, リッ                             | プル電圧±0.                  | 5%)                 |

| スパイク雑音電圧      | 60mV <sub>pp</sub> | $100 \text{mV}_{pp}$                | 200mV <sub>pp</sub>      | I00mV <sub>pp</sub> |

| 保護機能          | ● 出<br>● 入         | 力過電流保護<br>力過電圧,但<br>力突入電流防<br>線挿抜可能 | 電圧監視                     |                     |

$$Ve = \frac{P_L}{4 \times 10^{-13} \times f \times B^2} \text{ (cm}^3)$$

ここに  $P_L$ =鉄損( $\mathbf{W}$ )

f =変換周波数(Hz)

B=コアの動作磁束密度(G)

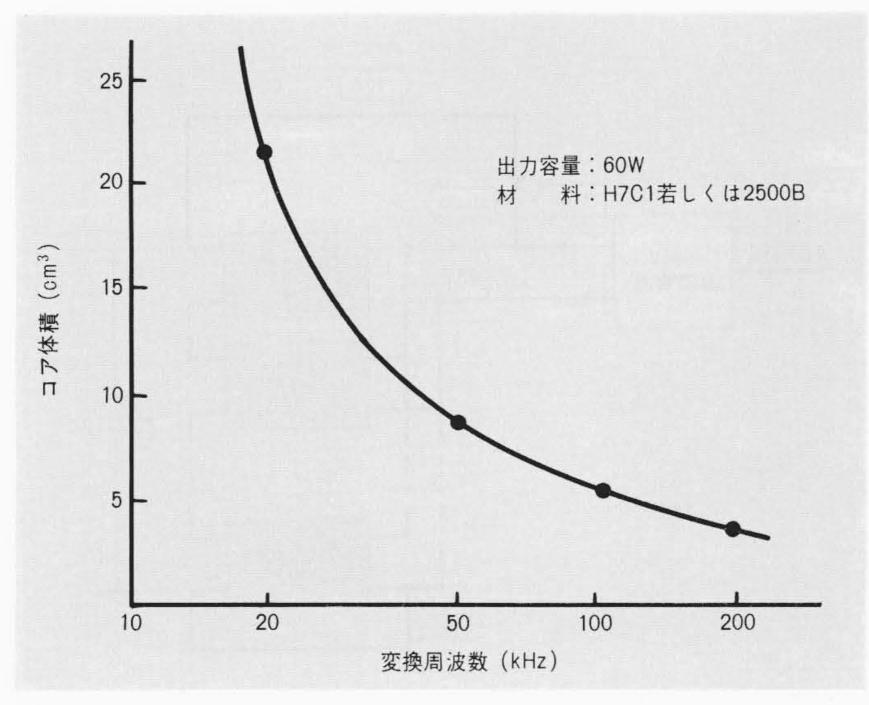

変換周波数を高めるに伴って鉄損も増加するため、磁束密度を下げて使用した。また、温度上昇を少なくするため鉄損と銅損のバランス、更に出力容量などを考慮して体積を決定した。実用化例として、60W電源のコア体積を図5に示す。

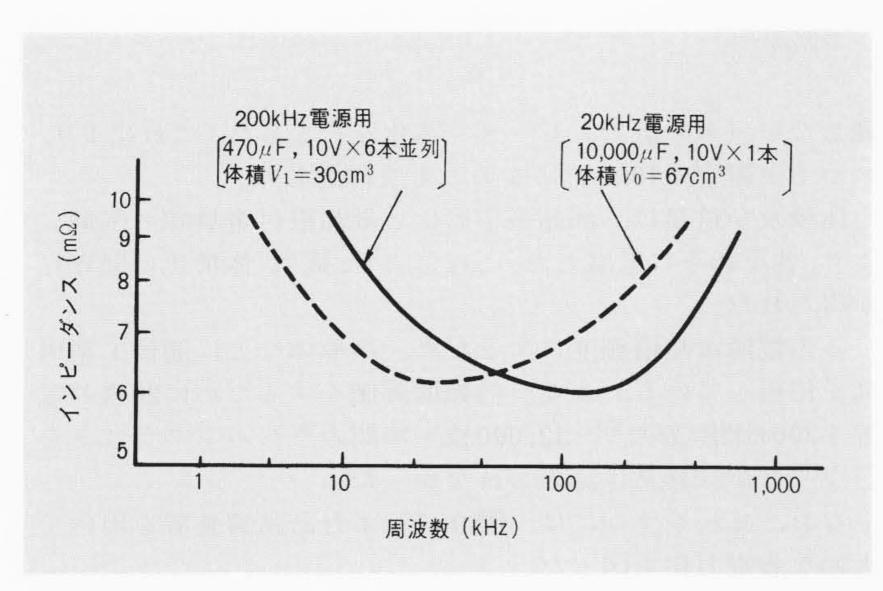

部品技術により、平滑コンデンサは小形化され、かつ許容リップル電流とESR(等価直列抵抗)も向上してきた。この結果、 $470\mu F$ の小形アルミ電解コンデンサ 6 個で、出力リップル電圧値を満足している。このときのインピーダンス特性、及び体積は $\mathbf{2}$   $\mathbf{6}$  に示すように改善される。平滑コンデンサの設定ポイントは、容量によるインピーダンス $\frac{1}{\omega c}$ よりも $\mathbf{ESR}$ が支配的なため、 $\mathbf{200kHz}$ に高周波化した割には大容量が必要で

ある。

また, 部品の小形化に伴い, 取付金具類などの寸法も低下 した。

以上の結果, 200kHz化により部品のシャドウエリアは, 図4の右側に示すように,約30%減少した。また,部品の搭載高も約1を低減できた。

## 3.2 半導体スイッチ

主スイッチにはバイポーラトランジスタに比べ、スイッチング特性、安全動作領域とも優れているパワーMOS FET、2SK176 ①を使用した。このパワーMOS FETを使用することにより、駆動回路の簡素化、キャリアの蓄積時間の無視によるパルス幅制御応答の向上、並列接続による電流容量の増加などが図れる。

図 4 各種回路部品のプリント板上のシャドウエリア(床面積) 200kHz高速変換により、トランスの床面積がまに低減した。

図5 変換周波数によるコア体積 高周波化により、コア体積は低減する。

図 6 コンデンサのインピーダンス特性 470µF, 6本並列にしたコンデンサは, 200kHz付近でインピーダンスは最小になる。また,体積も全になる。

#### 3.3 回路の高速化

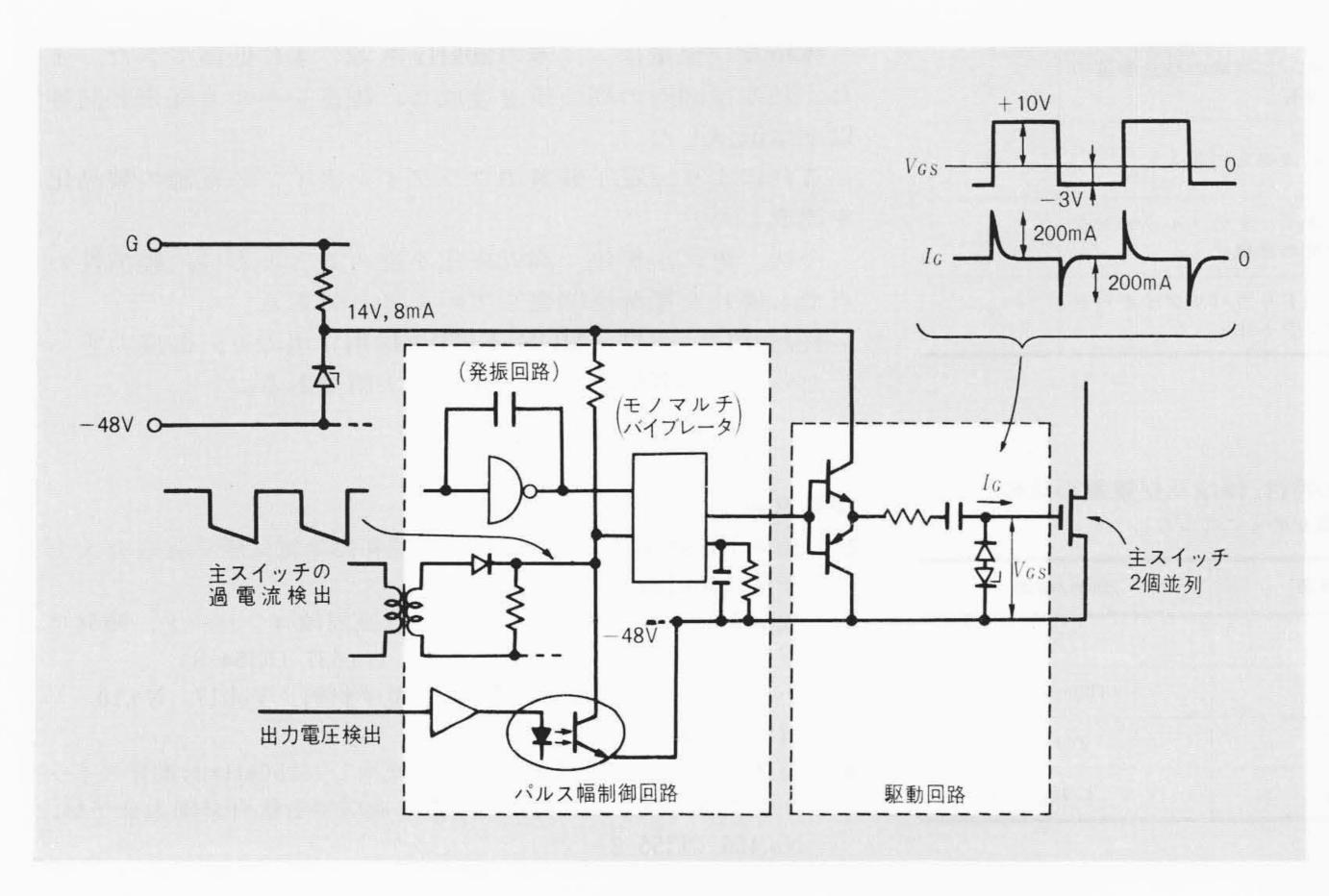

回路形式は、図3に示すようなパルス幅制御1石フォワードコンバータ方式を採用した。その回路構成を同図に示す。この回路で、高速変換に必要な主スイッチの駆動回路と出力制御回路を図7に示す。

MOS FETのゲート入力は容量だけのため、駆動電力が無視できる。しかし、容量が800pFにも達するため、駆動源インピーダンスは低インピーダンスを要求され、ゲートへの電流は100mAを必要とする。この駆動回路をCMOS(Complimentary MOS)論理ICとエミッタフォロア回路で実現している。また、MOS FETのゲート抵抗と内部容量との積分回路を考慮して、-3 Vの逆バイアスを与え、高速しゃ断を実現している。

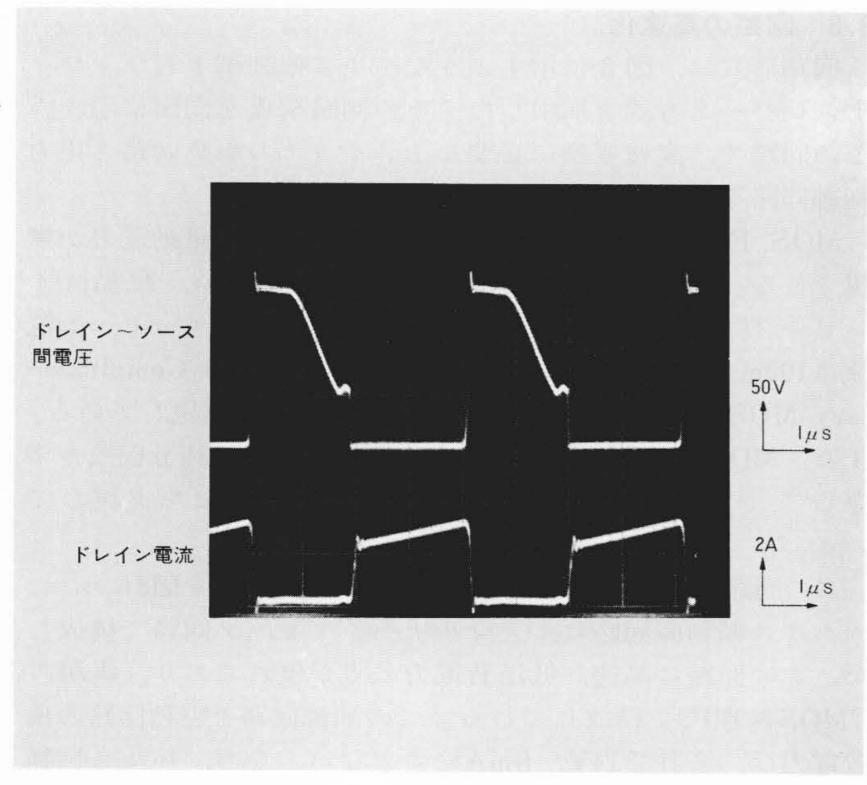

この回路で駆動した主スイッチの電圧電流波形を図8に示す。パルス幅制御回路はモノマルチバイブレータ回路で構成した。この回路は高速、低消費電力の点が優れており、汎用のCMOS論理ICで構成している。この制御回路と駆動回路の消費電力は、合計で14V、8mAにすぎない。なお、パルス幅制御機能は、過電流検出トランスの電流傾斜を利用しているため、のこぎり波状発生回路が不必要になり、回路構成が簡単になる。

#### 3.4 雑音対策

主スイッチ付近では電圧、電流の高速スイッチングによりdi/dt=3.3A/ $\mu$ s,dv/dt=5 kV/ $\mu$ sの高周波発生源が存在する。これが電源の導電雑音、輻射雑音を増加させる。このため、表2 に示す雑音対策を図った。このなかで、ソースケースのパワーMOS FET、2SK176 $\oplus$ Eを使用することは、主スイッチの電位変動が放熱板を通して、回路内部へ雑音を与えるのを低減する効果がある。また、ミラー効果用コンデンサにより、主スイッチのスイッチング速度を制御し、雑音を制限した。

# 4 特性

この200kHz電源と変換周波数20kHzの電源の比較結果を**表3**に示す。効率、雑音とも従来の性能を上回り、体積、重量はほぼ半減した。

注:略語説明 Vas(ゲートソース間電圧) Ia(ゲート電流)

図7 駆動回路と出力制御回路の回路構成 パワーMOS FETを高速にスイッチングさせる駆動回路とCMOS論理ICを使用した出力制御回路であり、簡素な回路構成となっている。

図 8 主スイッチの電圧,電流波形 電流しゃ断が速くて,200kHzに対して十分余裕がある。

総合効率は、高周波部品の採用と制御回路の消費電力の低減化により、定格出力時には80%を達成した。これにより、電力損失は最大15Wに低減でき、装置実装条件下では、自然空冷で使用可能となる。

出力に生ずるスパイク雑音は $60mV_{pp}$ であるから、論理回路 用電源として十分使用できる値である。更に雑音を少なくす る用途に対しては、部品配置を立体化し、配線の最短化と徹

表 2 採用した高周波雑音の対策法 低雑音化のためには、部品、回路どちらも対策を施す必要がある。

| 区分    | 対 策 法                  | 理由                     | 図3との対応 |

|-------|------------------------|------------------------|--------|

| 部品    | コモンモードチョークの<br>挿入      | 入出力間コモンモード電流<br>の除去    | ①      |

|       | ソースケースのパワー<br>MOS FET  | 放熱板の電位変動の低減化           | 2      |

| пр пп | 疎結合トランス                | 一次~二次間の結合容量の<br>低減化    | 3      |

|       | デップマイカ, セラミッ<br>クコンデンサ | 高周波雑音の除去               | 4      |

|       | ミラー効果用コンデンサ            | 主スイッチのスイッチング<br>速度の適量化 | (5)    |

| 回 路   | ダイオードに抵抗, コン<br>デンサ接続  | ハードリカバリダイオード<br>のソフト化  | 6      |

表3 200kHz電源と20kHz電源の特性,体積及び重量の比較高周波化による特長として、体積と重量が約分になった。

| 項     | 目    | 200kHz電源           | 20kHz電源              |

|-------|------|--------------------|----------------------|

| 効     | 李    | 80%                | 77%                  |

| 出力スパー | イク雑音 | 60mV <sub>pp</sub> | I 00mV <sub>pp</sub> |

| 体     | 積    | 1.11               | 2.31                 |

| 重     | 量    | 0.83kg             | 1. <b>4</b> kg       |

注:5V·I2A論理回路用電源

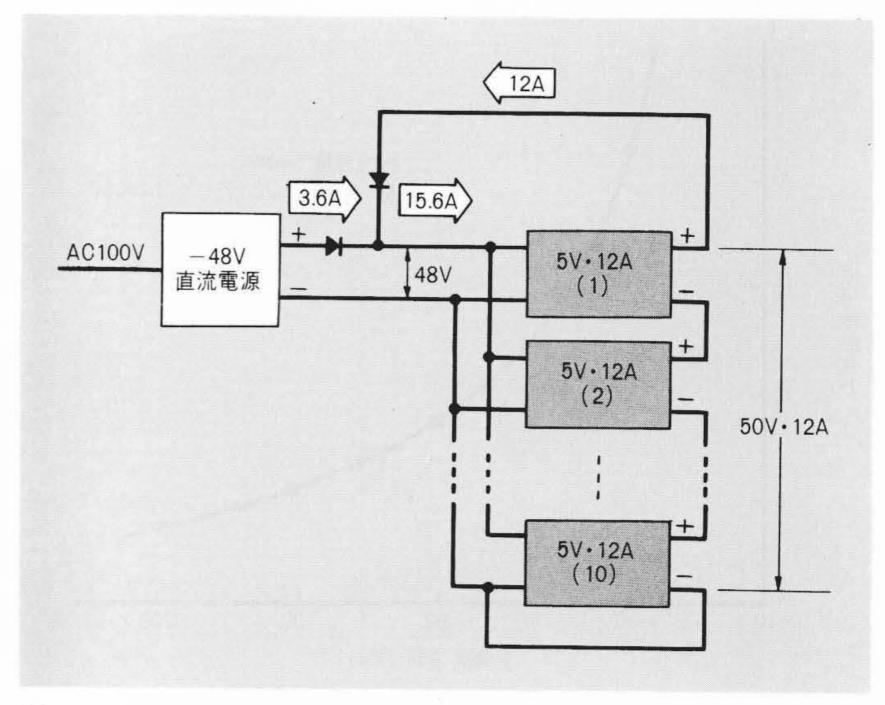

図 9 5V・12A電源の寿命試験装置の構成 5V・12A電源を10枚直列接続して得られた50V・12A出力電力を入力に戻すことにより、寿命試験を行なう。この構成は、入力電力を80%節約し、負荷抵抗を不必要にする。

底したアースの低インピーダンス化を行なった。これにより、スパイク雑音は $10 \text{mV}_{pp}$ になることを確認した。

体積及び重量は, 部品の小形化と部品取付金具類の削減により,各々約量に低減した。これにより,電力/体積比は55W/lが得られた。

この電源は高信頼度にするため、半導体などに通信工業用品を使用している。また、信頼度評価をするために20枚の電源を200日間にわたり、32,000枚・時間のランニングテストを行なったが、異常は認められなかった。

なお、ヒートランには、**図9**に示す寿命試験装置を用いて 大幅な省電力化を図った。

### 5 結 言

電源の小形,軽量化を目的として,200kHzスイッチング電源を開発した。

体積及び重量は、従来の20kHz電源の量に低減できた。また、効率は80%の高い値を達成し、雑音レベルも従来と同等以下に低減した。

これにより、電子装置用プラグインタイプの電源の製品化 を達成した。

今後, 更に小形化, 高効率化を進めるとともに, 経済性の 点でも優れた電源を開発していく考えである。

終わりに、パワーMOS FETの採用に当たり、御協力をいただいた関係各位に対し感謝する次第である。

### 参考文献

- 1) 福原:LSI実装における電源, 昭和53年電気四学会連合大会 予稿, No.192 (昭53-10)

- 2) 福原: MOSトランジスタを用いた高周波コンバータ, 昭54年 電子通信学会総合全国大会予稿, No.537 (昭54-3)

- 3) 上川:パワーMOS FETの話, 電子材料, Vol.17, No.10 (1978年10月)

- 4) 石黒, 外:パワーMOS FETを使用した250kHz低雑音スイッチングコンバータ, 昭和55年電子通信学会総合全国大会予稿, No.456 (昭55-3)