# 64kビットEEPROM

# 64k bit EEPROM

データの不揮発的記憶により、高度なマイクロコンピュータシステムの設計を容易にするメモリとして、EEPROM(電気的にデータ変更が可能なROM)が使われ始めてきた。本論文では、このたび開発された64kビットEEPROMの概要と技術内容について紹介する。

本製品では、 $2 \mu m MNOS$ (金属-窒化膜-酸化膜-半導体)技術による大容量化に加え、書き込み及び消去用の昇圧回路の内蔵により5 V 単一電源動作を、またメモリアレイ構成の工夫によりバイト消去機能を実現した。更に、スタティックRAM同様な使い方を可能にするラッチ回路の内蔵、 $10^4$ 回書き換え可能などの特徴をもっており、EEPROMのオンボードでの使用が一段と容易になった。

萩原隆旦\* Takaaki Hagiwara 谷田雄二\*\* Yûji Yatsuda 鍋谷慎二\*\*\* Shinji Nabetani 内田 憲\*\*\* Ken Uchida

#### 1 緒言

EEPROM(Electrically Erasable and Programmable Read Only Memory)は、ユーザーがメモリの内容をボード上で自由に書き換えることができるため、紫外線消去形のEPROM (Erasable and Programmable Read Only Memory) に比べて使いやすく、システム設計の自由度が増えるなどの点で魅力があり、また電池でバックアップされたCMOS(Complementary Metal Oxide Semiconductor)スタティックRAMに比べては、電池が不要であるため、システム構成が容易になるなどの利点をもっている。1980年に日立製作所が開発した16kビットEEPROM(HN48016)は、以前の他社品と比較して大幅に高性能化されており、マイクロコンピュータシステムに使用可能な近代的EEPROMの最初のものであったが1)、近年のマイクロコンピュータの急激な大規模化、高速化に伴い、EEPROMも更に大容量化、高機能化が要求されてきた。

本論文は、このようなニーズに対応するため開発された64kビットEEPROMの概要と主な技術内容について説明する<sup>2)</sup>。

# **2** MNOSメモリ素子

### 2.1 構 造

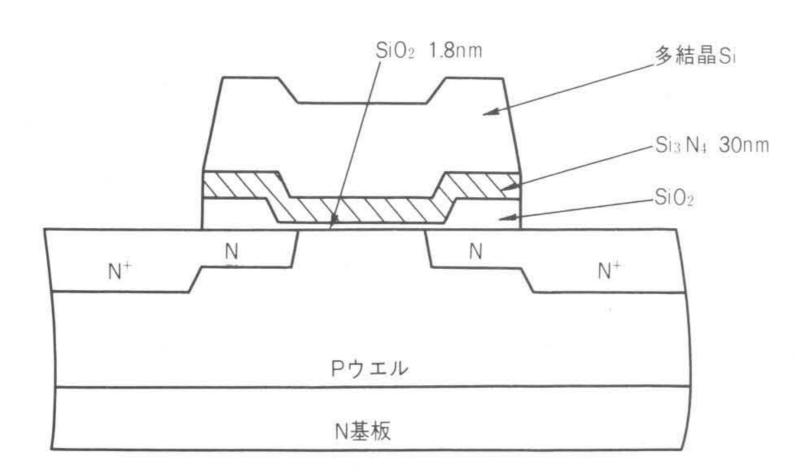

図1に本開発品で用いたMNOS(Metal Nitride Oxide Semiconductor)素子の構造を示す。MNOS素子は、MOSトラン

図 I MNOSメモリ素子の断面構造 MNOSメモリ素子は、シリコン窒化膜(Si<sub>3</sub>N<sub>4</sub>)とシリコン酸化膜(SiO<sub>2</sub>)の2層ゲート膜をもち、トンネル効果により電荷を窒化膜中に蓄積する。

ジスタのゲート酸化膜部分を厚さ 30 nm のシリコン窒化膜  $(Si_3N_4)$ と約 2 nm の極めて薄いシリコン酸化膜  $(SiO_2)$  の 2 層膜で置き換えた構造をもつ。書き込み時にはゲートに、消去時には基板に約16 V の高い電圧を印加して、トンネル効果によりSi基板からそれぞれ負及び正の電荷を窒化膜中に注入し、そこに蓄積する。蓄積された電荷が正であるか負であるかを回路的に判定して"1"、"0"に対応させる。

先の16k品では、 $3\mu$ mプロセスを用いており、セルサイズは $400\mu$ m²であったが、今回 $2\mu$ mプロセスを用いてこれを比例縮小し、64kに対応可能なセルサイズ( $180\mu$ m²)を実現した。また、16 Vの電圧を印加してもソース、ドレーンが降伏することのないように、図1 に示すようにゲート端部の絶縁膜を厚くし、かつその直下のソース、ドレーン不純物濃度を薄くして電界集中を緩和する方式の高耐圧構造を採用した。この構造はパワーMOSなどで使われているものと似ており、ソース、ドレーン耐圧は約20 Vとなった。

#### 2.2 メモリ素子の特性

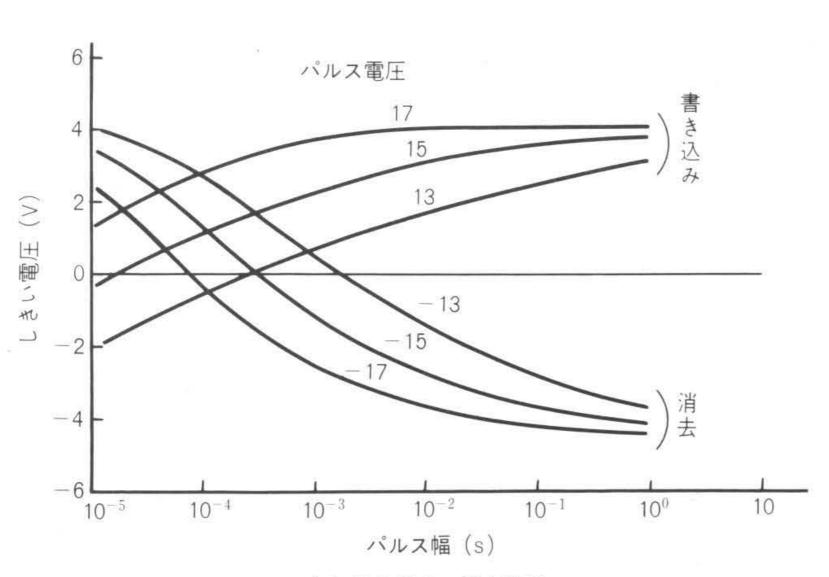

図2に本素子の書き込み・消去特性及び記憶保持特性を示す。(a) は書き込み・消去パルスを印加した時間と素子のしきい電圧の関係を、印加パルス電圧をパラメータとしてプロットしたものである。書き込みに要する時間は、大まかにはしきい電圧が負の状態から出発してゼロを横切るまでの時間、消去時間は逆に正の状態からゼロを横切るまでの時間と定義され、本開発品での使用電圧範囲(標準16V、最低15V)でそれぞれ数十マイクロ秒、及び数百マイクロ秒であり、製品目標仕様(両者とも10ms)を満たす特性であることが確認された。(b) は記憶保持特性であり、周囲温度125°Cでの書き込み・消去後のしきい電圧の放置時間依存性を測定したものである。この結果、10年の放置後に書き込み状態と消去状態の間に1.5 V以上のしきい電圧差が確保され、したがって、10年以上の情報保持が可能な実力をもっていることが確認された。

# 3 機能及び回路設計

EEPROMへの高機能化のニーズに対応するため、本開発品では、信頼性の高いバイト消去(8ビット単位の消去)及び5V単一電源化に重点をおいて設計した。

<sup>\*</sup> 日立製作所中央研究所 工学博士 \*\* 日立製作所中央研究所 \*\*\* 日立製作所武蔵工場

#### 3.1 バイト消去

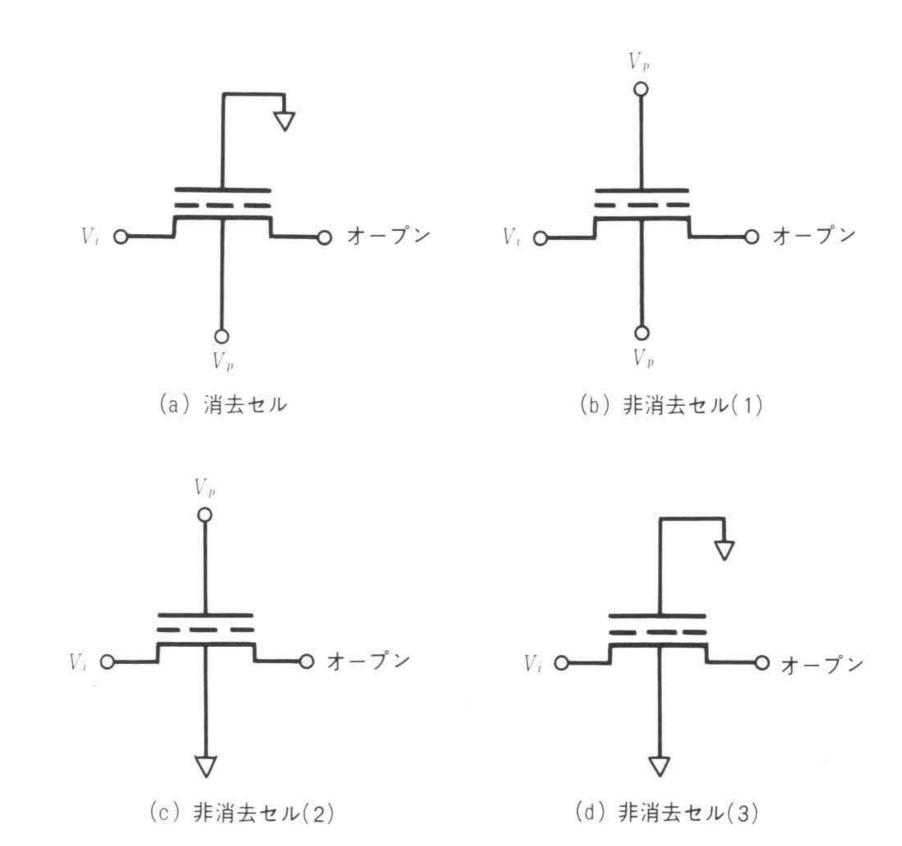

図3にバイト消去を実現するためのメモリ素子への電圧印加法を示す。MNOS素子を消去するためには、基板に電圧をかける必要がある。選択された1バイトを消去するときには、(a)に示すように、そのバイトが属する基板に16 Vのプログラム電圧(以下これを $V_p$ と記す。)を加え、選択されたセルのゲートを接地してゲート~基板間に高電圧を印加する。

このとき、セルがマトリックス状に配置されている関係で(b)  $\sim$  (d) に示す 3 種類の非消去セルが発生するが、これらで誤書き込みや、誤消去が絶対に起こらないようにする必要がある。本開発品では、書き込み禁止電圧 $V_i$ をメモリ素子のソース側に印加することにより、誤動作を防止するようにした。ここで $V_i$ は波形の立上がり、立下がり時を含めて常に $V_p$ と等しく設計しており、消去中にすべての非消去セルのゲート~基板間にかかる電圧は実効的にゼロとなる。これにより、バイト単位の消去が可能になった。

#### 3.2 5 V 单一電源化技術

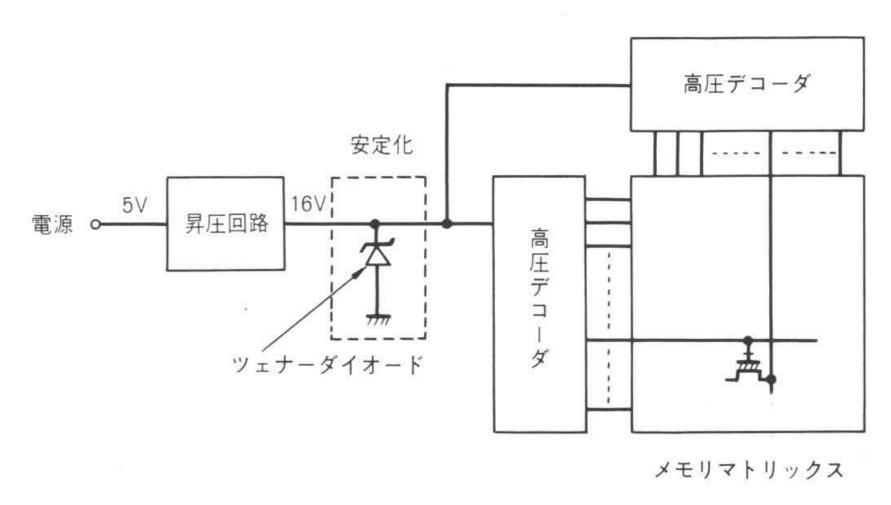

図4に、本開発品で用いた5V単一電源化方式を示す。まずチップ内に設けられた昇圧回路により5Vから16Vを発生し、これをツェナーダイオードにより安定化する。更に、高圧デコーダによりメモリマトリックス内の選択されたライン(ワード線、ビット線及び基板)に16Vを印加する。

#### 3.2.1 昇圧回路と安定化

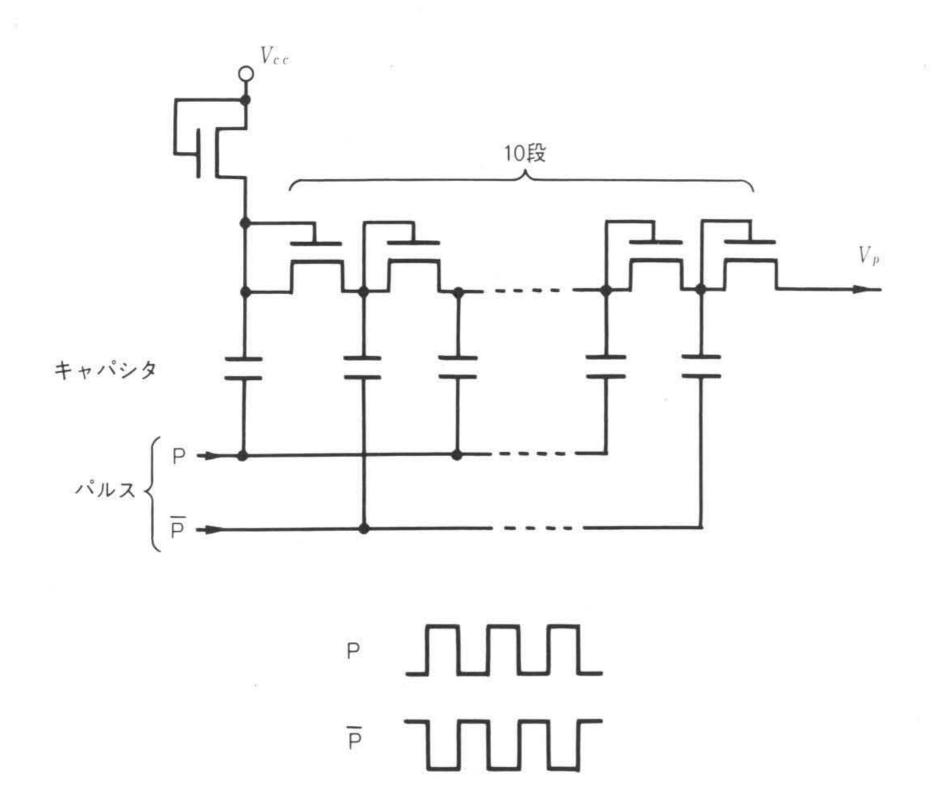

昇圧は、図5に示す回路で行なった。この回路は、位相の 180度異なる 2 個のクロックパルスを入力とし、電源  $V_{cc}$  側か

(a) 書き込み, 消去特性 周囲温度: 125°C

10<sup>3</sup> 10<sup>4</sup> 10<sup>5</sup> 10<sup>6</sup> 10<sup>7</sup> 10<sup>8</sup> か置時間(s) 10年

図 2 メモリ素子の特性 使用電圧条件( $16\pm1V$ )で書き込み時間は数十マイクロ秒,消去時間は数百マイクロ秒である。また記憶保持時間は、 $125^{\circ}$ Cで10年の実力がある。

(b) 記憶保持特性

図 3 バイト消去時での電圧印加方法 (a) 消去セルの基板に $V_p$ を 印加, ゲートは接地する。このとき(b) $\sim$ (d)の3種の非消去セルでの誤動作防止のため、書き込み禁止電圧 $V_i$ (= $V_p$ )をメモリ素子のソース側に印加する。

図 4 5V単一電源化の方式 昇圧回路により 5 Vから16Vを発生,これをツェナーダイオードで安定化したのち,高圧デコーダによりメモリマトリックス内の選択された素子に印加する。

ら $V_p$ 側に電荷を送り込む方式であり、チャージポンプ回路と呼ばれる。少ない段数で高い電圧を得るためには、回路中のMOSトランジスタのしきい電圧をできるだけ低くする必要があり、ここではしきい電圧がほぼゼロのトランジスタ(低しきい値MOSと呼ばれる。)を用いた。これにより、10段のチャージポンプ回路で5V電源から16Vへの昇圧が電源電圧や温度のワースト条件でも可能となった。

#### 3.2.2 高圧デコーダ

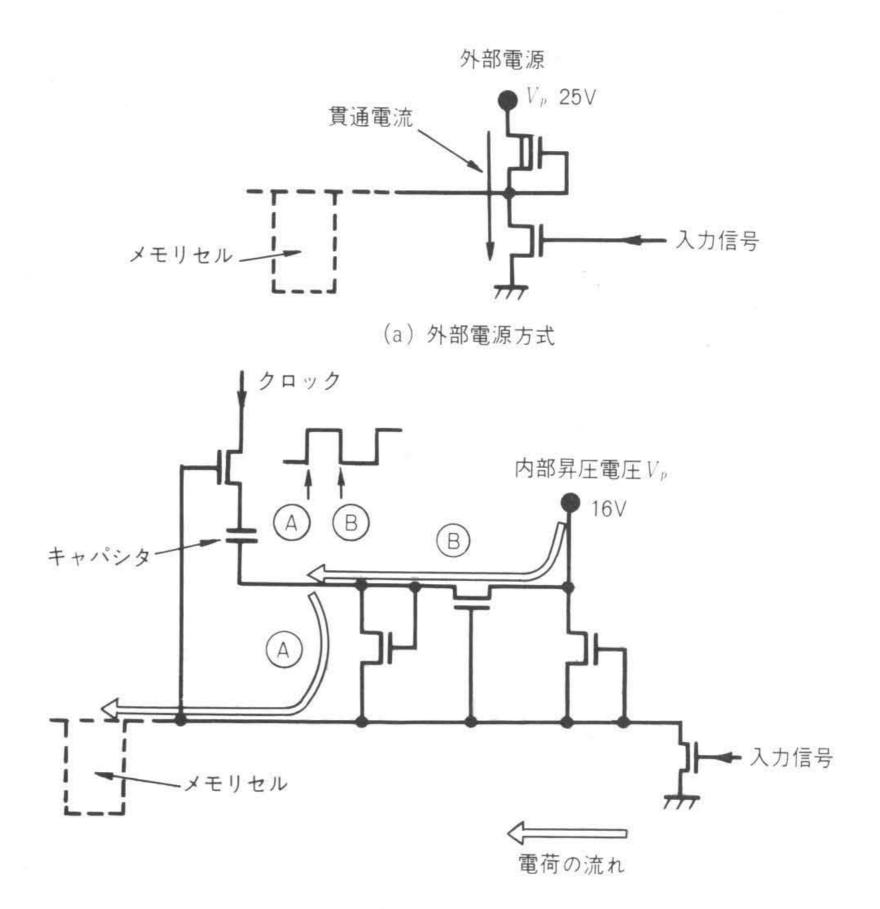

従来の $V_p$ 電源を外部から供給する場合の高圧デコーダの構成は、② 6(a)に示すようなE/D形インバータであった。このデコーダは非選択時(入力信号high)に大きな貫通電流(インバータ1個で約 $10\mu$ A、チップ全体では数ミリアンペア)が流れるため、5 V単一方式の場合は使うことができない。なぜならば、② 5 に示す昇圧回路の電流供給能力はたかだか10  $\mu$ A程度であり、数ミリアンペアの電流が流れると全く昇圧できなくなるからである。したがって、高圧のデコーディングが可能で、しかも貫通電流が全く流れない回路が必要となるが、

図 5 昇圧回路 MOSトランジスタとキャパシタを組み合わせたチャージポンプ回路10段から成り、5V電源から16Vを発生する。

メモリセルが非選択の場合は、入力信号をHighにすればメモリセル側のノードは接地に引き抜かれ、同時にクロック信号もカットされるので昇圧動作は行なわれなくなり、貫通電流が流れることはない。

(b) 内部昇圧電源方式

図 6 高圧デコーダ回路の比較 外部電源方式の場合はE/D形インバータが使えるが、内部昇圧方式の場合は(b)のようなチャージポンプ回路が必要になる。

このデコーダ回路を使うことにより、5V単一電源化が実現可能となった。

#### 3.3 機 能

本開発品はスタティックRAMやEPROMと同系統のバイトワイド系列にあり、したがって、構成は8kバイト×8ビット、又はピン配置はEPROMとコンパチブルである。書き込みはバイト単位であり、消去はバイト単位とチップ全体を一度に消去する二つのモードを用意している。アクセス時間は最高速のもので250ns、書き換え回数は16k品での実績から、10<sup>4</sup>を保証できる見通しである。

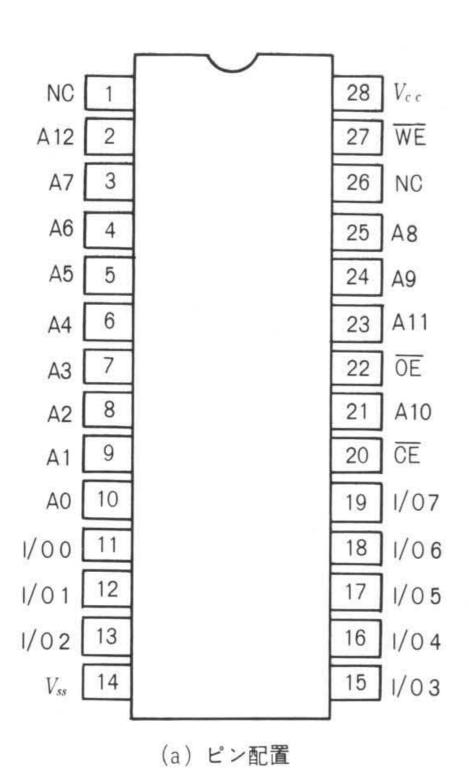

図7にピン配置とモード一覧表を示す。モードは主にCE,

| モード     | CE<br>(20) | 0E<br>(22) | WE<br>(27) | I/O 0∼7<br>(11∼13, 15∼19) |

|---------|------------|------------|------------|---------------------------|

| 読み出し    | VIL        | VIL        | VIH        | Dour                      |

| 待機      | VIH        | X          | X          | High Z                    |

| バイト消去   | VIL        | VIH        | VIL        | DIX = XID                 |

| バイト書き込み | VIL        | VIH        | VIL        | D <sub>1N</sub>           |

| チップ消去   | VIL        | VIL        | VIL        | $D_{IN} = VIH$            |

| 非 動 作   | VIL        | VIH        | VIH        | High Z                    |

注:VIL= $-0.1\sim0.8V$ VIH= $2.0\sim V_{cc}+1V$ X=Don't care

(b) モード選択

図 7 64k EEPROMのピン配置とモード選択 本EEPROMは、64k EPROM やスタティックRAMとコンパチブルである。動作モードは、 $\overline{CE}$ 、 $\overline{OE}$ 、 $\overline{WE}$ 及びデータ入力により判断され、選択される。

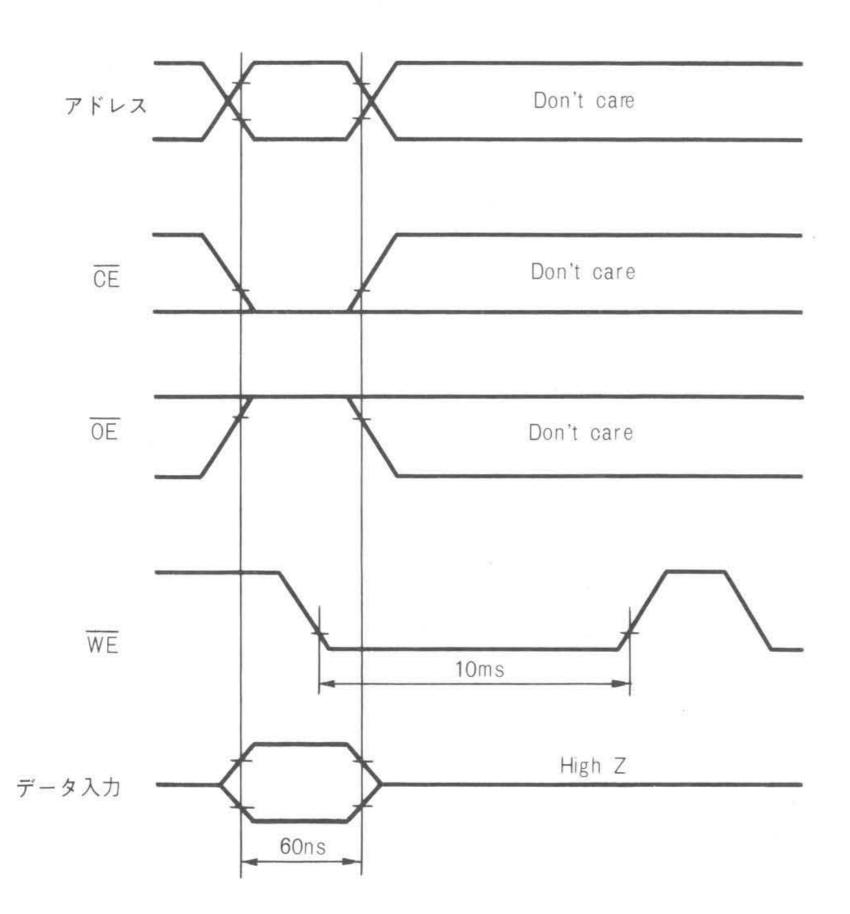

図 8 書き込み、消去時のタイミングダイヤグラム 書き込み、消去時のアドレス、 $\overline{CE}$ 、 $\overline{OE}$ 及びデータ入力信号は、 $\overline{WE}$ の立下がり時にすべて取り込まれ、ラッチされる。

$\overline{OE}$ 及び $\overline{WE}$ の 3 個のピンの入力信号で決めるが、書き込みと消去の区別はこれらのピンではなく、入力データがすべて"1"であるか(=消去)"0"が混じっているか(=書き込み)で判断する。入力信号電圧はすべて $\overline{TTL}(\overline{Transistor}\ Transistor\ Logic)$ レベルである。

図8に書き込み又は消去時の入力信号のタイミングダイアグラムを示す。本EEPROMはアドレス、CE、OE及びデータの入力をラッチする機能をもっており、これらはすべてWE信号の立下がり時に取り込まれる。書き込み及び消去時間(10ms)はWEがLowレベルにある時間で決められるが、ラッチ機能のため、その間アドレス信号などを保持しておく必要はなく、マイクロコンピュータ側は他の仕事をすることができる。この機能を活用することにより、本EEPROMは見掛け上スタティックRAMとほとんど同じように動作し、効率のよいシステム設計が可能となる。

## 4 主な特性

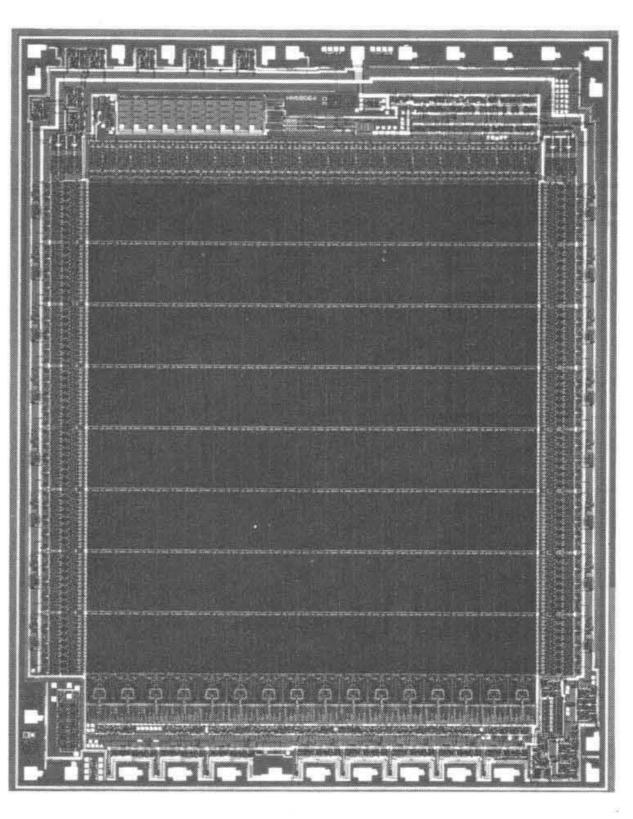

チップ写真を図9に示す。チップサイズは5.0mm $<math>\times 6.3$ mm である。

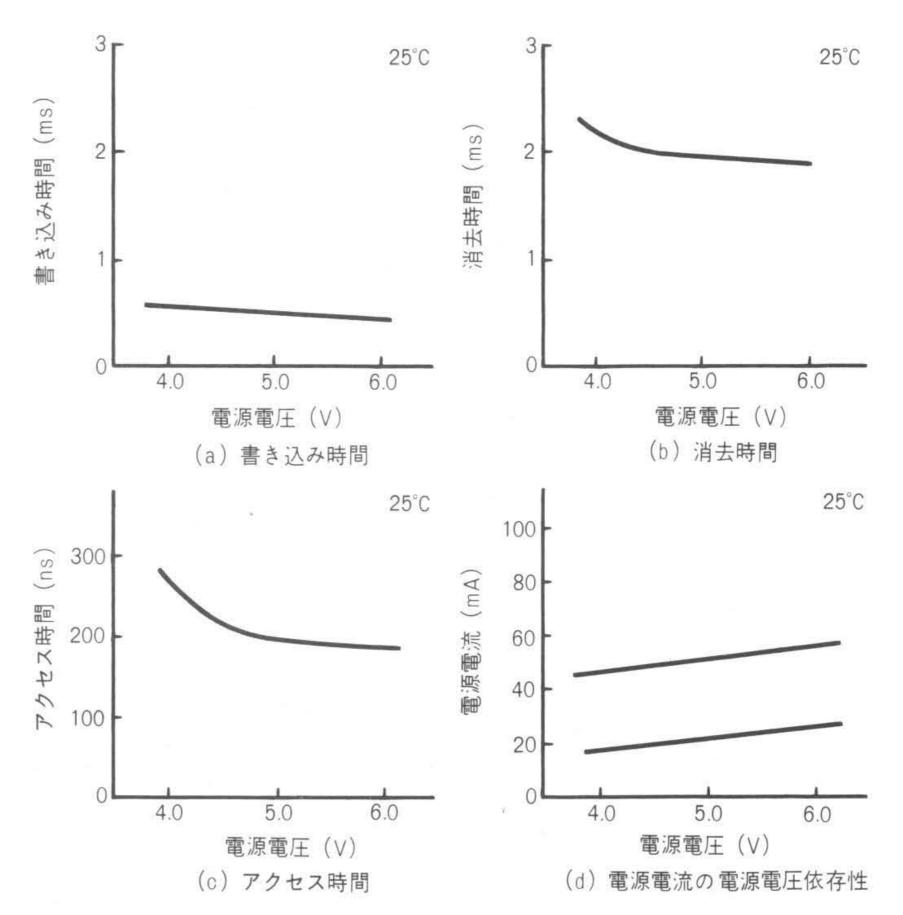

図10に室温での主な特性を示す。(a) は書き込み時間の,また(b) は消去時間の電源電圧依存性である。書き込み時間は0.5ms程度,消去時間は2ms程度である。内部昇圧電圧がツェナーダイオードで制御されているため,これらはあまり電源電圧依存性がなく安定に動作する。(c) にはアクセス時間の電源電圧依存性を示す。アクセス時間は標準条件で200nsである。また電源電流の電源電圧依存性を(d) に示すが,標準条件で動作時50mA,待機時20mAであった。

# 5 結 言

5V単一電源で動作する64kビットEEPROMを開発した。本開発品は、これまでの16k品に比べ近年の複雑化したマイクロコンピュータシステムにマッチするように使いやすさを大幅に向上させたものであり、見掛け上スタティックRAMと同様に動作し、

図 9 64k EEP-ROMのチップ写真 メモリマトツ 真 メモリマトリックスは マット方式とし、ワード系高圧デコーダはマット系高圧デコーダは上部に配置されている。

図10 64k EEPROMの特性 書き込み時間,消去時間は、内部昇圧電圧がツェナーダイオードで安定化されているため、電源電圧による変動が少ない。

システムの設計が一段と容易になった。また、電池なしで記憶保持が可能であるという特徴を生かし、エレクトロニックカードや情報パックとしての応用も期待できる。更に、EEPROMオンチップマイクロコンピュータのニーズも出始めており、本技術の適用分野は今後大きく広がってゆくものと思われる。

### 参考文献

- 1) T. Hagiwara, et al.: A 16Kb electrically erasable programmable ROM, ISSCC Dig. Tech. Papers, 50~51(1979)

- 2) 谷田,外:バイト消去可能なプログラム電源内蔵形64Kビット EEPROM,電子通信学会論文誌,J66-C 927~934(1983-12)