# システム集積形CMOS 8 ビットマイクロプロセッサ "HD64180"

# System Integration Oriented CMOS 8bit Microprocessor "HD64180"

従来のソフトウェア財産をそのまま流用でき、かつ性能の向上、システムコストの低減を実現するマイクロプロセッサが市場で求められている。この要求にこたえて、システム集積形CMOS 8 ビットマイクロプロセッサHD64180を開発した。

HD64180は、最新のCMOS  $2\mu$ m技術を用い、高速CPUのほかに、MMUやDMAC などの周辺機能をワンチップ上に集積したマイクロプロセッサである。CPUは80系の命令体系と互換性をもっており、既存の膨大なソフトウェア財産の利用が可能である。また、最高動作周波数  $6\,\mathrm{MHz}$ 、豊富な周辺機能の内蔵により、システムの高性能・高機能化、及びコストの低減を可能にした。本稿では、HD64180の機能を中心に紹介する。

赤尾 泰\* Yasushi Akao 馬場志朗\* Shirô Baba 越路誠一\*\* Seiichi Koeji 木田博之\*\*\* Hiroyuki Kida

#### 1 緒 言

マイクロプロセッサの開発競争は、16ビットから32ビット へと移行しつつあるが、市場の現状は依然として8ビットが 主流である1)。この背景には、今までに蓄積された膨大な量の ソフトウェア財産を活用したいという要求がある。そのため, 8ビットのマイクロプロセッサには既存のソフトウェアを流 用でき、かつ性能・機能の向上、システムコストの低減を実 現するマイクロプロセッサが強く望まれている。日立製作所 ではこのような市場の要求に対応するため、CMOS(Complementary Metal Oxide Semiconductor) 8 ビットマイクロ プロセッサHD64180を開発した。CPU(Central Processing Unit)の命令体系は、多くのソフトウェア財産をもつ80系の命 令体系と互換性があり,既存のソフトウェアの活用が可能で ある。また、応用システムの機能向上、コストの低減を図る ため、MMU (Memory Management Unit), DMAC (Direct Memory Access Controller), 直列通信器, タイマ, バスコ ントローラなどの応用システムには欠くことのできない周辺 機能をオンチップ化した。特に、512kバイトの物理アドレス 空間をもつMMUは、従来の8ビットの64kバイトというアド レス空間の制限を取り除き,新しい応用の道を開いた。

以下, HD64180の特長, 機能などについて述べる。

#### 2 特 長

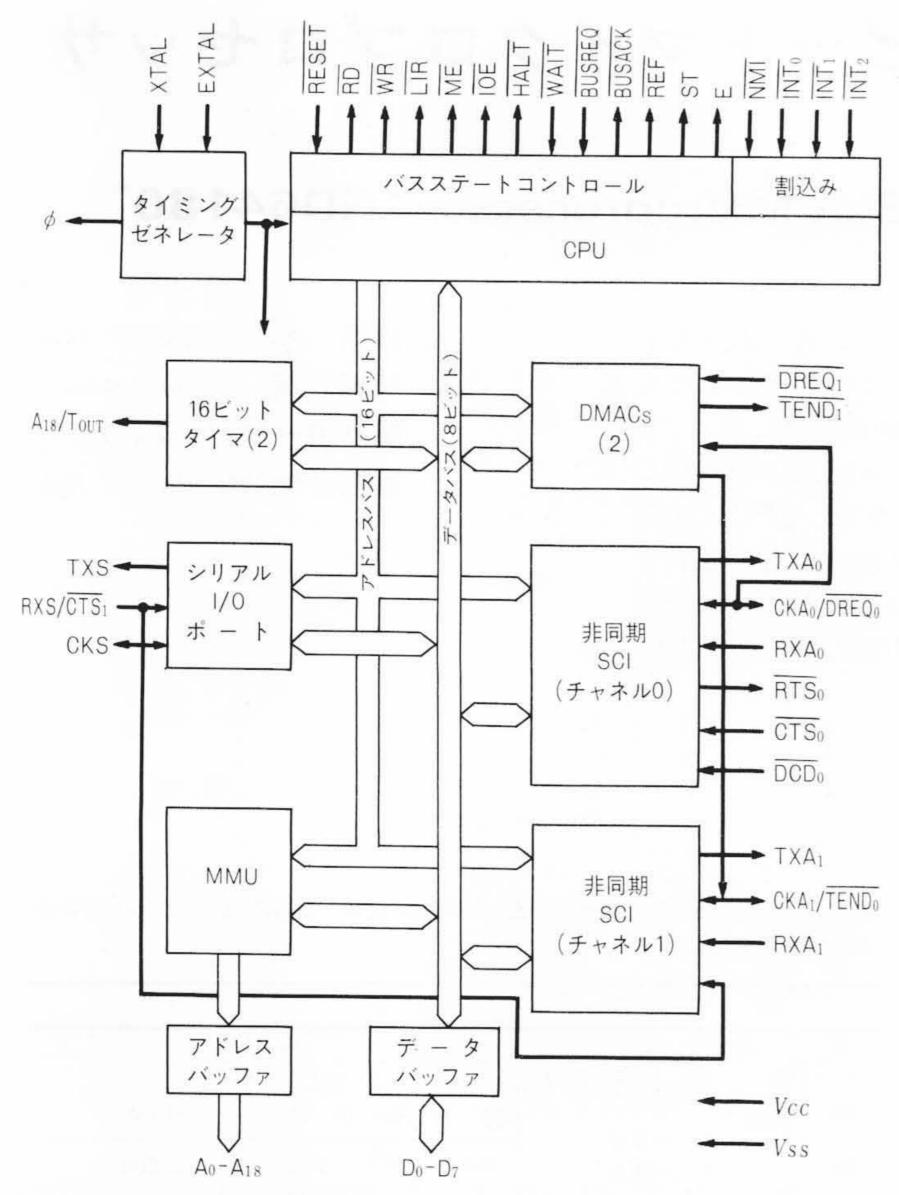

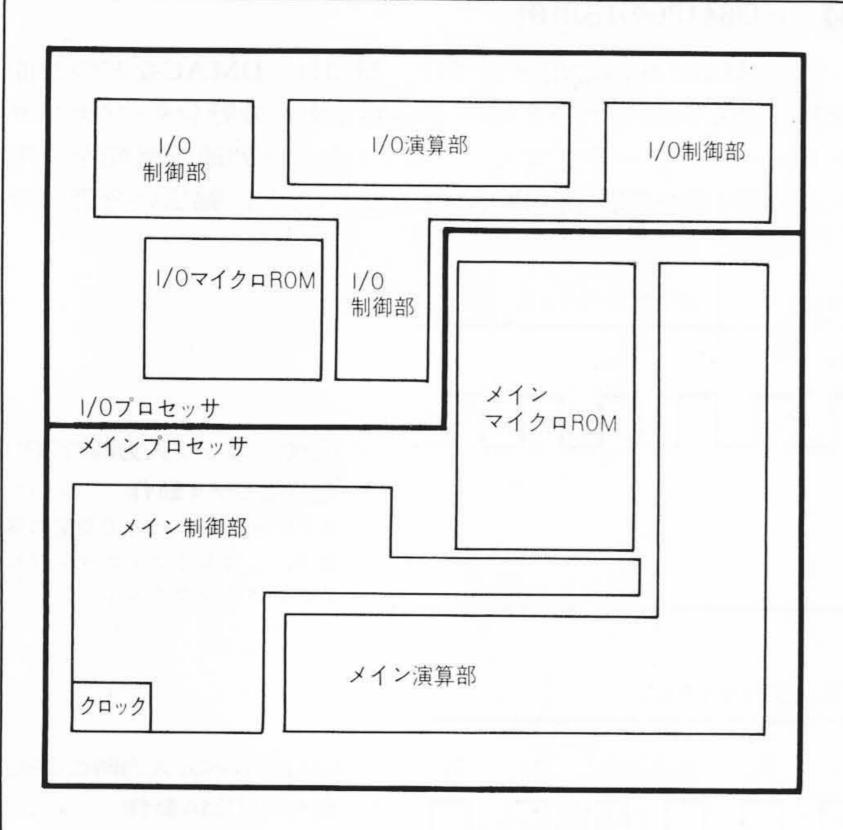

表1にHD64180の仕様の一覧を、図1にブロック図をそれぞれ示す。CPU以外の周辺機能もワンチップ化した、いわゆるSystem Integration Oriented Microprocessor(システム集積指向マイクロプロセッサ)ということができる。

命令体系は、特にデータ処理応用分野でのソフトウェアの互換性を保つことができるように、80系と上位互換性がある。また、メモリ空間の拡張に応じて、 $I/O(\Lambda \pm 1)$ 機器との間やメモリ間で高速に大量のデータ転送が必要となるが、これらは2チャネルのDMAC、3チャネルの直列通信器によって行なわれる。更に、バスウエイトコントローラ、DRAM(Dynamic Random Access Memory)用のリフレッシュコントローラを内蔵することにより、バスインタフェースの柔軟性を向上さ

表 I HD64180の仕様一覧表 HD64180は、高速CPUに加え、豊富な周辺機能を内蔵している。

|     | 項            | 目                           |                                                      |                                                                                     | 仕            |    |       | 様               |  |  |  |  |

|-----|--------------|-----------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------|--------------|----|-------|-----------------|--|--|--|--|

| プ   | ゜ロセス         |                             |                                                      |                                                                                     | CMOS         |    |       |                 |  |  |  |  |

|     | 電源           | 電                           | 圧                                                    | 5 V ± 10%                                                                           |              |    |       |                 |  |  |  |  |

| 特   | 消費           | 電 力<br>c = 5 V              | (typ)                                                | 通常                                                                                  | 動            | 作  | 時     | 50mW            |  |  |  |  |

| 性   | f= 4 MHz     |                             |                                                      | システムストップ時 I2.5mW                                                                    |              |    |       |                 |  |  |  |  |

|     | 最小命          | $0.5\mu s(f=6 \text{ MHz})$ |                                                      |                                                                                     |              |    |       |                 |  |  |  |  |

|     | 命令           | 体                           | CP/M-80*1)ソフトウェアコンパチブル                               |                                                                                     |              |    |       |                 |  |  |  |  |

|     | 基本           | 165                         |                                                      |                                                                                     |              |    |       |                 |  |  |  |  |

|     | 割            | 込                           | 外部4本,内部8本                                            |                                                                                     |              |    |       |                 |  |  |  |  |

|     | アド           | レ ス 空                       | 512kバイト(MMU内蔵)                                       |                                                                                     |              |    |       |                 |  |  |  |  |

| 機   | 1            | DMAC                        |                                                      | 2チャネル  ● メモリ↔メモリ  ● メモリ↔I/O(メモリマップ)  最大転送レート IMバイト/秒(f=6)                           |              |    |       |                 |  |  |  |  |

|     | インタ          | ノリアル<br>フェ・<br>ASCI)        | Access in the                                        | <ul><li>2チャネル</li><li>●8種のデータフォーマット</li><li>●3種のエラーフラグ</li><li>●モデム制御信号あり</li></ul> |              |    |       |                 |  |  |  |  |

|     | クロック         | クロック同期シフトレジスタ Iチャネル         |                                                      |                                                                                     |              |    |       |                 |  |  |  |  |

|     | 1/0 ポー       | - ト (CS                     | 1/0)                                                 | 最大ボ                                                                                 | ーレート         | 30 | 00kボー | -(f=6MHz)       |  |  |  |  |

| 能   | 9            | 1                           | マ                                                    |                                                                                     | リロード<br>け あり |    |       | チャネル<br>,トグル出力) |  |  |  |  |

|     | バスウエイトコントローラ |                             |                                                      | 外部端子による制御<br>内部レジスタによる制御<br>(メモリ, I/O独立に設定可)                                        |              |    |       |                 |  |  |  |  |

|     | リフレッシュコントローラ |                             |                                                      | プログラマブル非同期リフレッシュ<br>8ビットのリフレッシュアドレス(256kDRAM対応)                                     |              |    |       |                 |  |  |  |  |

|     | バスイン         | 80系・68系・(63系)とも可能           |                                                      |                                                                                     |              |    |       |                 |  |  |  |  |

| 18  | ッケ           |                             | デュアルインライン64ピン シュリンク パッケーシ (DP-64S) (リード間ピッチ70milタイプ) |                                                                                     |              |    |       |                 |  |  |  |  |

| ポート |              | リアルタイムトレース                  |                                                      |                                                                                     |              |    |       |                 |  |  |  |  |

| /ール | クロスアセンブラ     |                             |                                                      | 豊富なコマンド機能<br>H680SD200用                                                             |              |    |       |                 |  |  |  |  |

注:略語説明 DMAC(Direct Memory Access Controller)

I/O(Input-Output)

ASE(Adaptive System Evaluater)

CMOS(Complementary Metal Oxide Semiconductor)

MMU(Memory Management Unit)

DRAM(Dynamic Random Access Memory)

※1) CP/M-80は、米国ディジタルリサーチ社の登録商標である。

注:略語説明 SCI(Serial Communication Interface)

図 | ブロック図 内部アドレスは16ビット、MMUにより19ビットに拡張された物理アドレスが出力される。

せ、いわゆる「TTL(Transistor Transistor Logic)で組まなければならない雑ロジック」の低減を図っている。

低消費電力動作も、特長の一つである。通常動作時、50 mW ( $V_{cc}=5 \text{V}$ , f=4 MHz)と低消費であり、更に低消費電力動作を有効にする命令やモードを備えている。

開発ツールとしては、ソフトウェアはH680SD200用のクロスアセンブラ、ハードウェアはリアルタイムトレースが可能なインサーキットエミュレータH68AS02をそろえている。

#### 3 性能・機能

#### 3.1 ソフトウェア性能

内部動作をパイプライン化し、高速動作を実現した。他の80系CPUの実行サイクル数と比較した場合、平均16%サイクル数を圧縮した。特にサイクル数の多い命令ほど圧縮率は高く、インデックス修飾命令などサイクル数が多い命令を多用する場合は、高速化が顕著である。

また、性能向上のため、3種類のオリジナル命令を追加した。

#### 3.1.1 演算強化命令

8ビットの乗算命令及びテスト命令を追加した。これにより制御用演算の強化を図った。

#### 3.1.2 内蔵I/Oアドレッシング命令

内蔵のI/Oレジスタは、I/O空間の0ページ( $0000H\sim00$  FFH)にマッピングされている。このため、内蔵のI/Oレジスタをアクセスする場合、上位アドレスが0になるようなアド

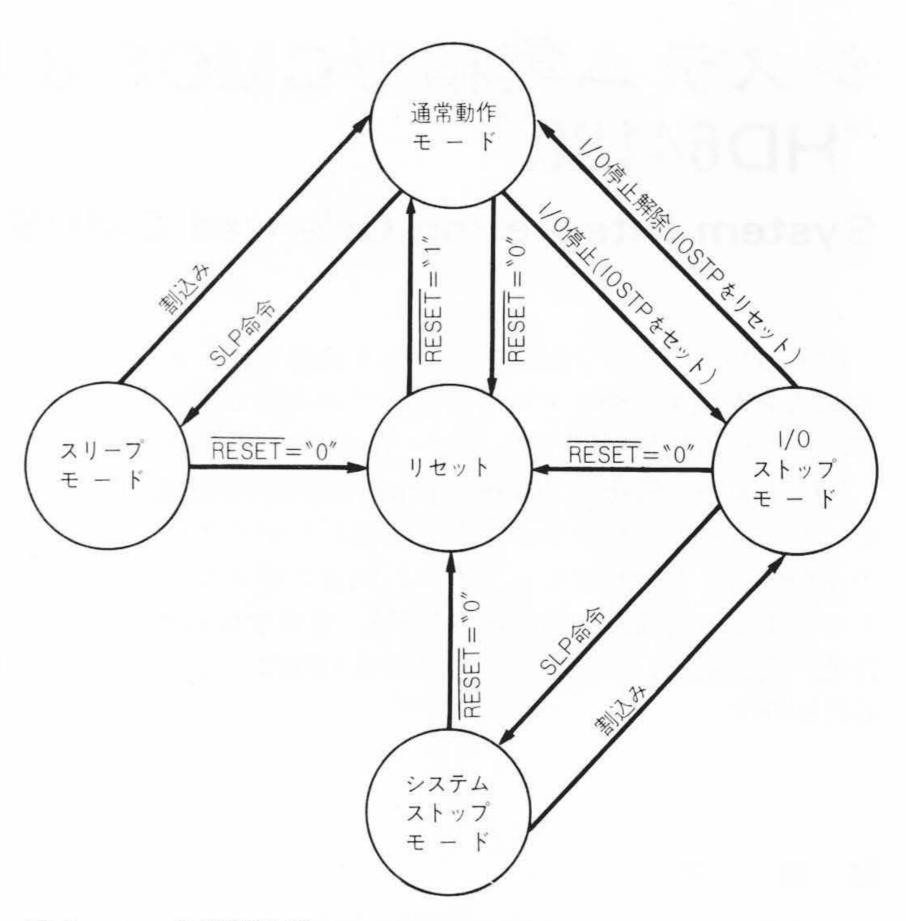

図 2 モード間遷移図 命令の実行,ビットのセット・リセット,割込み信号,リセット信号により各モード間を遷移する。

レッシング命令を追加し、内蔵のI/Oレジスタに対するアクセスの効率を上げている。また、転送ごとにメモリアドレスだけでなく、I/Oアドレスも増減するブロック転送命令をもっており、連続した内部I/Oレジスタへの初期値の設定などに有効である。

#### 3.1.3 低消費電力動作命令

低消費電力動作を有効に利用できるモードとして、 スリー プモード, I/Oストップモード, システムストップモードの3 種類がある。スリープ命令を実行するとスリープモードとな り、CPUの動作は停止し、タイマや通信機能といったI/O機能 だけ動作を継続する。スリープモードでは、消費電力は通常 動作時の約号となる。スリープモードは割込み、リセットに より解除されるので、CPUが割込み待ち状態にあるようなと きに使用すると有効である。I/OストップモードではCPUを動 作させたままで、I/O機能の動作だけを停止させることができ る。このI/Oストップモード中、スリープ命令を実行すると、 CPU, I/O機能の両方共停止したシステムストップモードにな る。このモードでは、消費電力は通常動作時の約1になる。 このモードは外部割込み、リセットにより解除される。これ らのモード間遷移の様子を図2に示す。応用に従い、これら のモードを使用することにより, 効果的に消費電力を低減す ることができる。

#### 3.2 割込み

HD64180は割込みとして、内部 4 本、外部 8 本の要因をもっている。

#### 3.2.1 TRAP

TRAP割込みは、未定義のオペコードを読み込んだときに発生する。TRAP割込みが発生すると、論理アドレスの0000 Hからリスタートするが、これはリセット直後のスタート番地と同じであるため、通常そこにはリセットかTRAPかを判断するプログラムを置いておく。TRAPと判断した場合、TRAPの処理プログラムにジャンプする。この処理プログラムによりTRAP割込みを、エラープロテクション、ユーザー定義命

令など,種々の応用に利用することができる。

#### 3.2.2 NMI

NMI割込みが発生すると、CPUは論理アドレスの0066H番地にジャンプする。NMIはマスクすることができないため、電源瞬断時など緊急の割込み処理に用いられる。また、後述するDMACの外部からの停止要求信号としても使用される。

#### 3.2.3 INT<sub>0</sub>

INToには次の三つのモードを命令により選択できる。

- (1) データバス上の命令を実行する。

- (2) 論理アドレス0038Hからリスタート

- (3) ベクタアドレスの発生(ベクタリング)

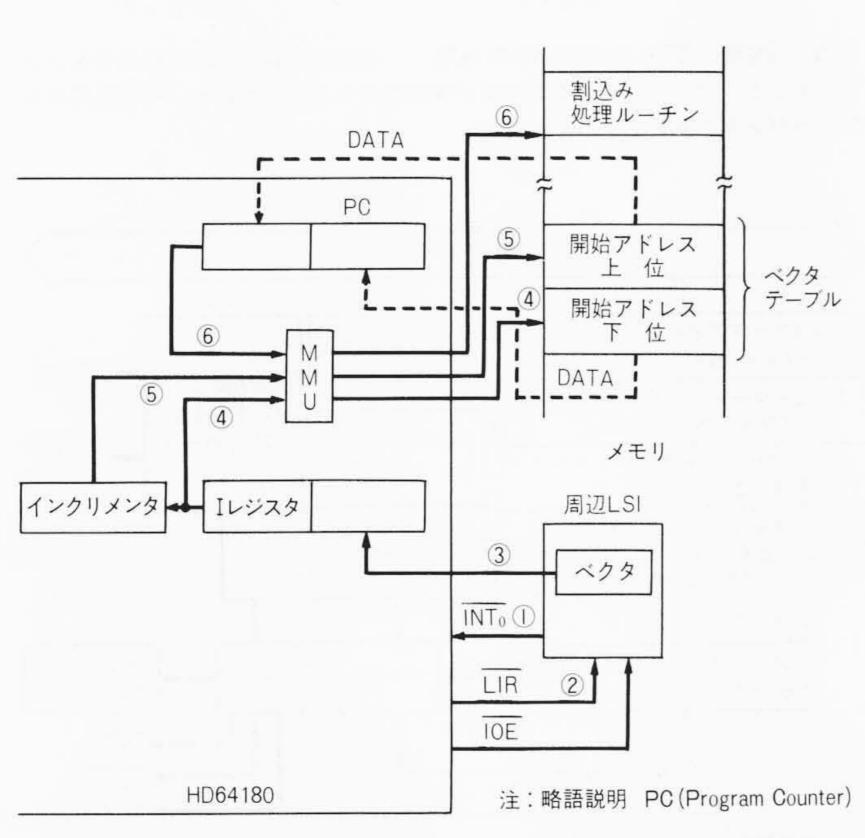

(3)のベクタアドレスは論理アドレスであり、上位8ビットは Iレジスタと呼ばれるレジスタから、下位8ビットは割込みア クノレッジサイクル中にデータバス上に載せられたデータか ら供給される。このベクタアドレスはMMUにより物理アドレ スに変換された後、ベクタテーブルを参照するのに用いられ る。この様子を図3に示す。

#### 3.2.4 INT<sub>1</sub>, INT<sub>2</sub>及び内部割込み(TRAPを除く。)

これらの割込みはベクタリング方式である。ベクタアドレスは論理アドレスであり、その上位8ビットはIレジスタから、下位8ビットはILレジスタと呼ばれるレジスタから供給される。ILレジスタの下位5ビットは各要因ごとに固定コードが

図 3  $INT_0$ ベクタシーケンス ベクタアドレスは、Iレジスタの値と割込みを要求した周辺LSIからのデータにより生成される。このベクタアドレスは、MMUにより物理アドレスに変換され出力される。

表 2 割込み要因とベクタ ベクタアドレスの下位 8 ビットは、 Lレジスタから供給される。 Lレジスタの下位 5 ビットは、 各要因ごとに固定、 上位 3 ビットがプログラマブルになっている。

| dulta + #FED     | /百 / · · · · · | Lレジスタ |         |                | 固定コード          |                |                |                |         |  |

|------------------|----------------|-------|---------|----------------|----------------|----------------|----------------|----------------|---------|--|

| 割込み要因            | 優先度            | b7    | b6<br>* | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | bo<br>0 |  |

| INT <sub>1</sub> | 高              |       |         |                |                |                |                |                |         |  |

| INT <sub>2</sub> | 4              | *     | *       | *              | 0              | 0              | 0              | 1              | 0       |  |

| タイマチャネル0         |                | *     | *       | *              | 0              | 0              | - 1            | 0              | 0       |  |

| タイマチャネルー         |                | *     | *       | *              | 0              | 0              | 1              | L              | 0       |  |

| DMAチャネル0         |                | *     | *       | *              | 0              | 1              | 0              | 0              | 0       |  |

| DMAチャネルI         |                | *     | *       | *              | 0              | 1              | 0              | -1-            | 0       |  |

| シリアル1/0ポート       | -              | *     | *       | *              | 0              | 1              | 1              | 0              | 0       |  |

| 非同期SCIチャネル0      |                | *     | *       | *              | 0              | l t            | I              | - 1            | 0       |  |

| 非同期SCIチャネルI      | 低              | *     | *       | *              | 1              | 0              | 0              | 0              | 0       |  |

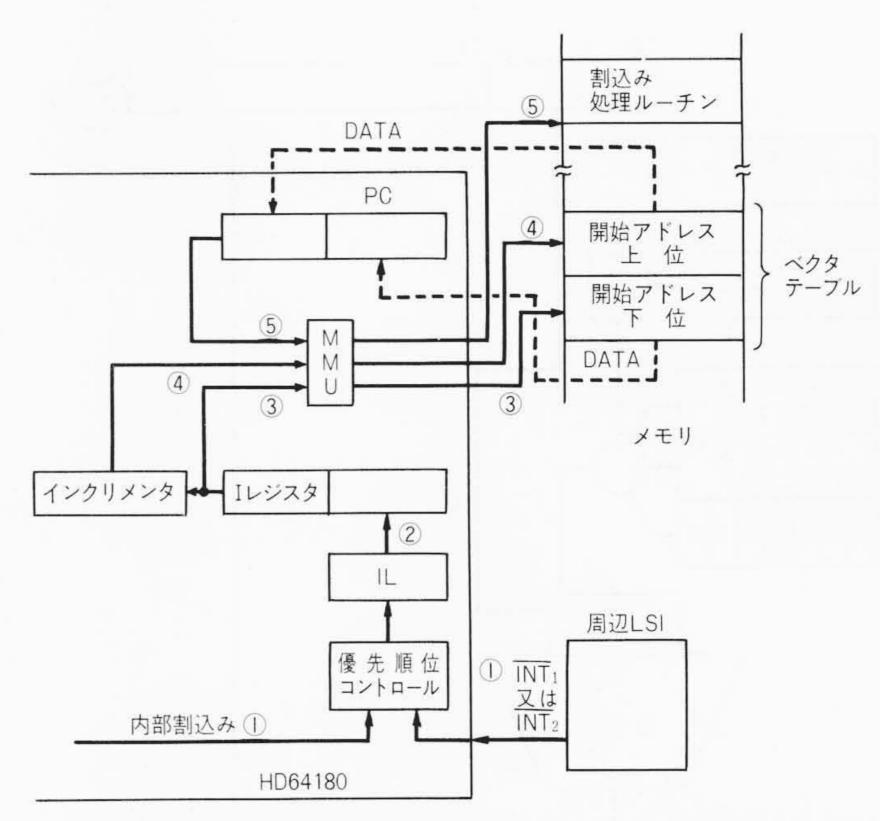

図 4 INT1, INT2, 内部割込みベクタシーケンス ベクタアドレスは、 |レジスタの値と|Lレジスタの値により生成される。このベクタアドレスは、 MMUにより物理アドレスに変換され出力される。

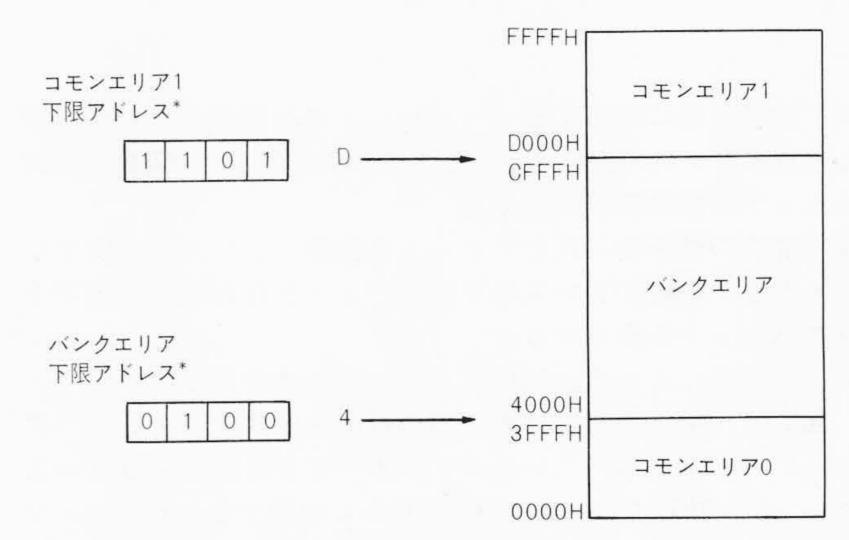

図 5 論理空間 \* コモンエリア | の領域の下限のアドレス及びバンクエリアの領域の下限のアドレスとして、上位4ビットを設定することができる(バンクエリア、コモンエリア 0 の領域の上限のアドレスは、この下限のアドレスの設定により自動的に決まる)。

割り当てられており、上位 3 ビットがプログラマブルになっている(表 2 参照)。したがって、Iレジスタと合わせて上位11 ビットがプログラマブルであり、64kバイトの論理空間中32バイトごとに、ベクタテーブルを置くことができる。このベクタアドレスもMMUにより物理アドレスに変換された後、ベクタテーブルを参照するのに用いられる。この様子を図 4 に示す。

#### 3.3 MMU

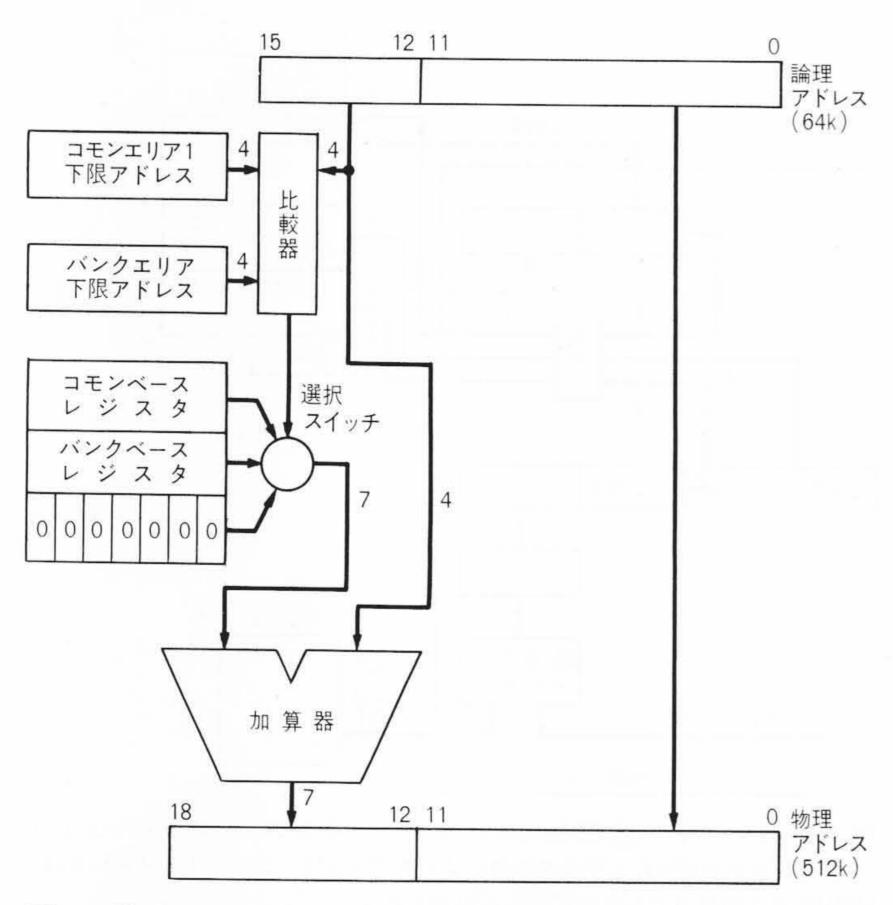

内蔵のMMUは、64kの論理空間を512kの物理空間に拡張する機能をもっている。MMUは、論理空間を三つの空間に分割(コモンエリア 0、1及びバンクエリア)して管理する。どのように分割するかはユーザープログラマブルであり、この分割の様子を図5に示す。MMUはこれらの論理空間の各領域ごとに、各々の対応するベースレジスタの値に従って独立に物理空間に写像する。この論理アドレス→物理アドレスの変換の機構を図6に示す。この動作は以下に述べるとおりである。(1) アクセスされた論理アドレスが論理アドレスのどの領域にあるのかを判定する(図6の比較器の部分で判定)。

図 6 物理アドレス生成の機構 MMUは比較器,選択スイッチ,加算器及び各レジスタから構成されている。

- (2) 論理領域に対応するベースレジスタを選択し、この内容と論理アドレスの上位4ビットとの加算を行なう(図6の選択スイッチ及び加算器の部分)。

- (3) 加算の結果得られた7ビットを物理アドレスの上位7ビットとし、論理アドレスの下位12ビットと合わせて物理アドレス19ビットを出力する。

以上の演算によって, 物理アドレスが生成される。

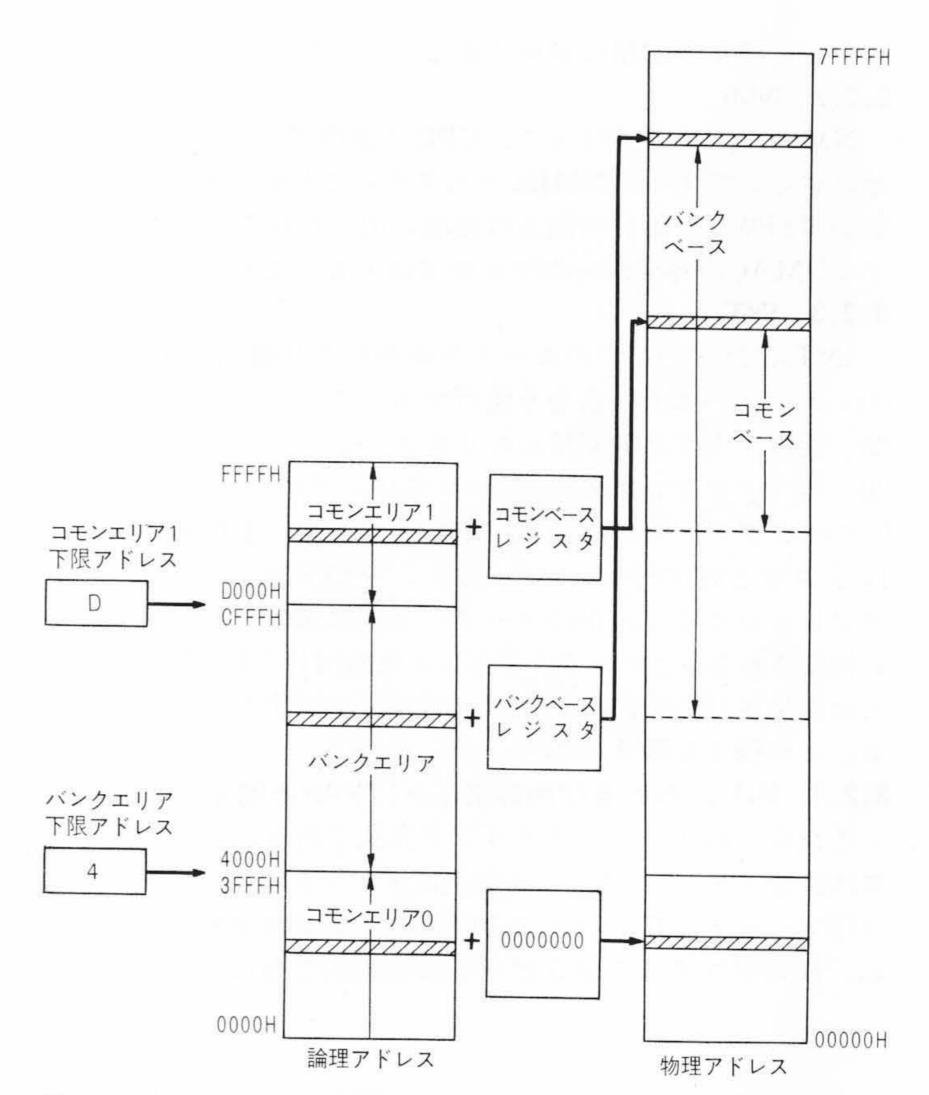

図7に、論理空間と物理空間の対応を示す。コモンエリア 0は、対応するベースレジスタがすべて0に固定されている ため、常に物理空間の底(00000H)から位置する。バンクエリ アとコモンエリア1に対応するベースレジスタは、ソフトウ ェアにより任意の値を設定することができ、物理空間上4kバ イトごとに任意のアドレスに各領域を写像することができる。 その結果, 異なる論理アドレスが同じ物理アドレスに重なっ て置かれたり,同じ論理アドレスの領域が物理アドレスのト ップとボトムに分かれて位置する場合など, ベースレジスタ の値により種々のメモリマッピングを選択することができる。 このように物理空間への拡張に非常に柔軟性がある一方,通 常の8ビットマイクロコンピュータのアドレス拡張法として よく見られる単純なバンクスイッチ方式とも互換性がある。 この場合、バンクスイッチを切り換えるため、外部回路のフ リップフロップなどを書き換える処理の代わりに、ベースレ ジスタの値を書き換えればよい。

MMUによって変換されるのは、CPUによりメモリ空間をアクセスする場合のすべてであり、この中には通常のオペコード、オペランドなどのアクセス以外に、割込みなどのリスタートアドレス、ベクタアドレスなども含まれる。I/O空間へのアクセス及び後述するDMACによる転送の場合は、メモリ空間、I/O空間共MMUによる変換を受けない。

MMUはリセット解除後、ベースレジスタがすべて0にイニシャライズされ、見掛け上MMUが機能しない状態に設定されるので、論理アドレス=物理アドレスとなり、従来のソフトウェアとの互換性を保つことができる。

図 7 論理空間と物理空間の対応 物理アドレスで斜線の部分をアクセスすると、ベースレジスタの内容が論理アドレスに加算され、物理空間の斜線の部分をアクセスする。

注:略語説明 DMA(Direct Memory Access)

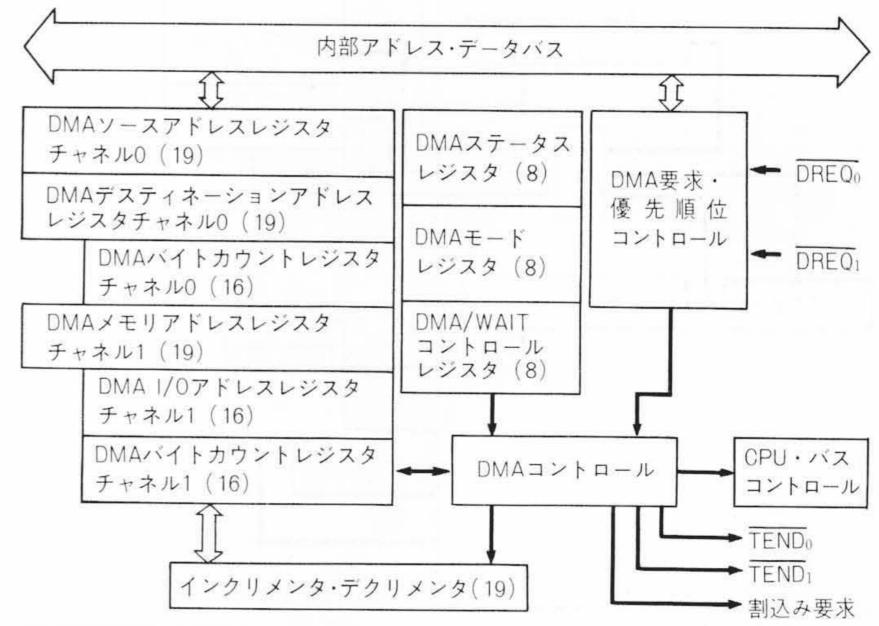

図 8 DMACブロック図 メモリアドレスを指定する場合には、19ビットの物理アドレスを設定する。

#### 3.4 DMAC

HD64180は 2 チャネルのDMACを内蔵している。DMACのブロック図を図 8 に示す。チャネル 0 は、メモリ  $\rightarrow$  メモリ転送及びメモリ  $\rightarrow$  I/O転送を、チャネル 1 はメモリ  $\rightarrow$  I/O転送を行なうことができる。3 .3 のMMUの節で説明したように、DMACの動作中アドレスはMMUをバイパスして出力される。このため、DMACのアドレス指定用のレジスタには直接物理アドレスを指定するようになっており、512kバイトの物理空間上任意のアドレス間の転送が容易に行なえる。

メモリ→メモリ間の転送モードとして、次に述べる2種類のモードがある。

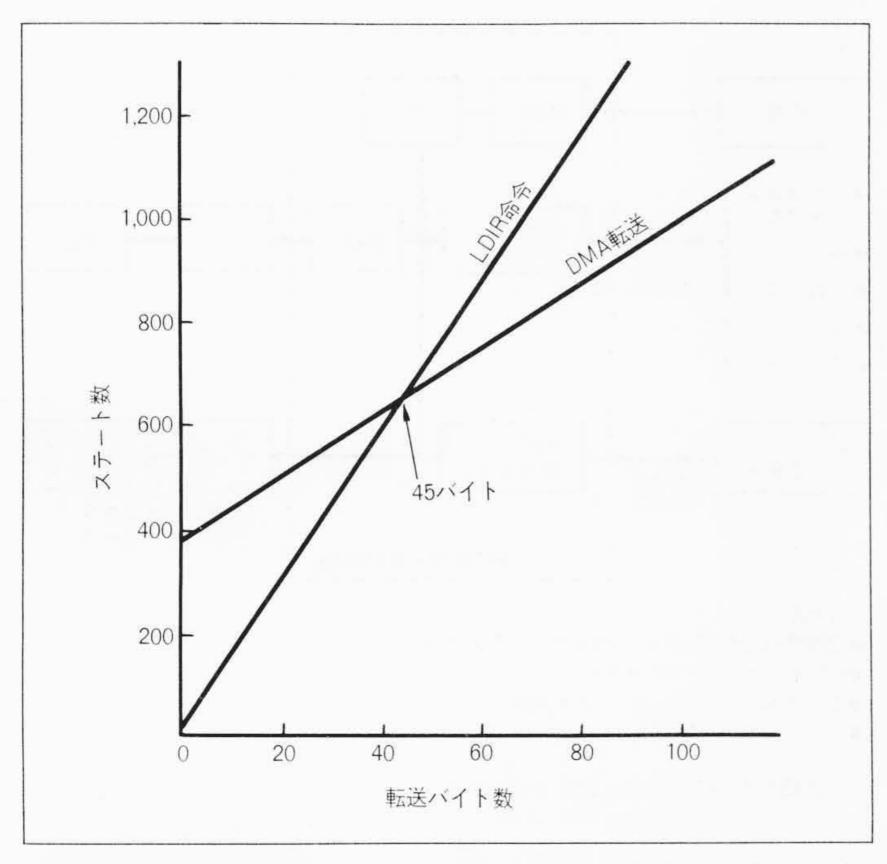

図9 DMAとLDIR命令との比較 メモリ→メモリ転送では、転送バイ ト数が45バイト以上になれば、DMA転送のほうが有利となる。

#### (1) サイクルスチールモード

1バイトの転送とCPUの1マシンサイクルの実行とが交互 に行なわれる。それほど高速転送が必要とされない場合、CPU のバックグラウンドジョブとしてメモリ間転送を行なう場合 有効である。

### (2) バースト転送モード

バイトカウンタが0になるまでDMA動作を連続して実行 する。メモリ間転送を高速に行なう必要がある場合有効であ る。

メモリブロック転送命令を用いた場合と, DMACのバース トモードを用いた場合の転送速度の比較を図9に示す。この 例では、単純な転送速度だけの比較ではなく各々の転送のた めの設定に必要なオーバヘッド, 例えばDMACで論理アドレ スを物理アドレスに変換するルーチンなどを考慮に入れた計 算であり、実際の使用例に非常に近い。同図からメモリ間転 送にどちらを使用したほうが速く転送できるかの目安を得る ことができる。DMACの場合,初期設定にかなりステート数 を費やすため、転送バイト数がある程度長くなければそのメ リットがでてこない。

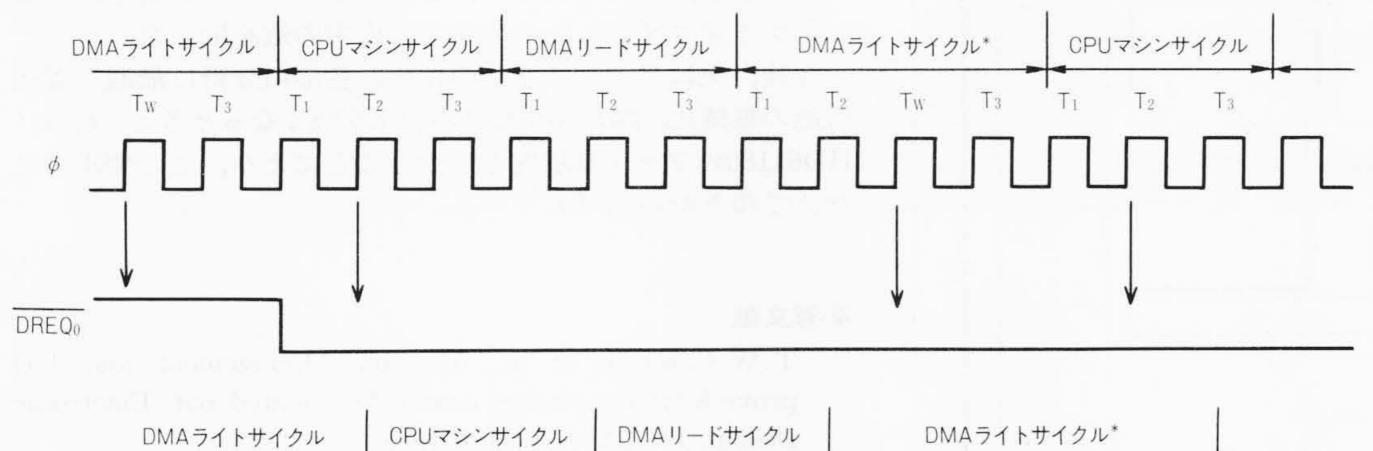

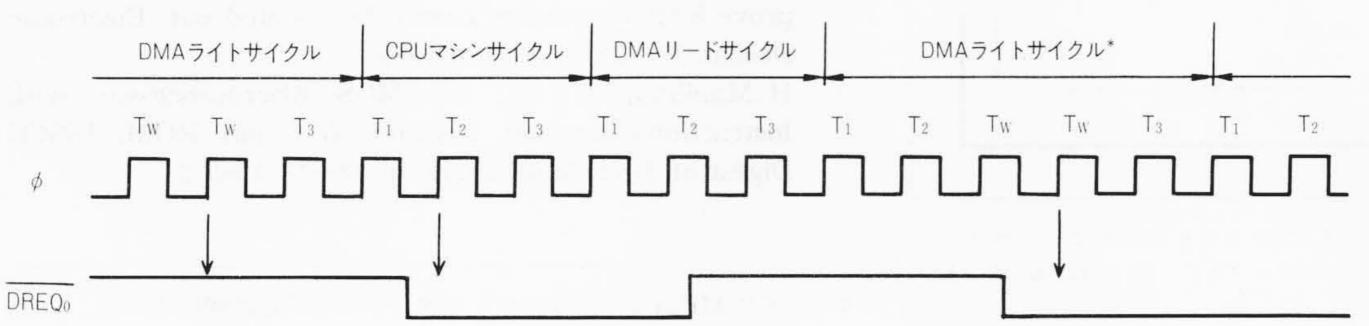

メモリ→I/O転送の場合、I/O機器からのDMA要求信号とし て、エッジ又はレベルが選択可能であり、機器の仕様に対応 できる。エッジ検出,レベル検出の場合の各々の動作例を図 10, 11に示す。I/O機器へのアクノレッジ信号は, I/Oアドレ スをデコードした信号を使用する。

チャネル 0 は内蔵のASCI (Asynchronous Serial Communication Interface)とDMA転送することが可能である。こ れを利用することにより、シリアル通信によるデータ転送を CPUの介在なしに行なうことができる。

DMA動作の外部からの中断は、NMI信号によって行なわれ る。DMAが動作中NMI割込み要求が入力されると、転送中で あればその1バイトの転送が終了した後, DMA動作は禁止さ れ制御がCPUに移る。転送中でない場合は、DMA動作が禁止 されCPU動作が続行する。CPUは通常のNMI割込み動作を実 行する。このときDMACの各レジスタの内容はそのまま保持 されているので、CPUにより再びDMAを動作可能の状態にす ることによって、DMA動作を再開、継続することができる。 このNMIによるDMA中断の機能は、DMA転送を行なってい るI/O機器の異常などによるDMACの異常動作を中断するた めに使用することができる。

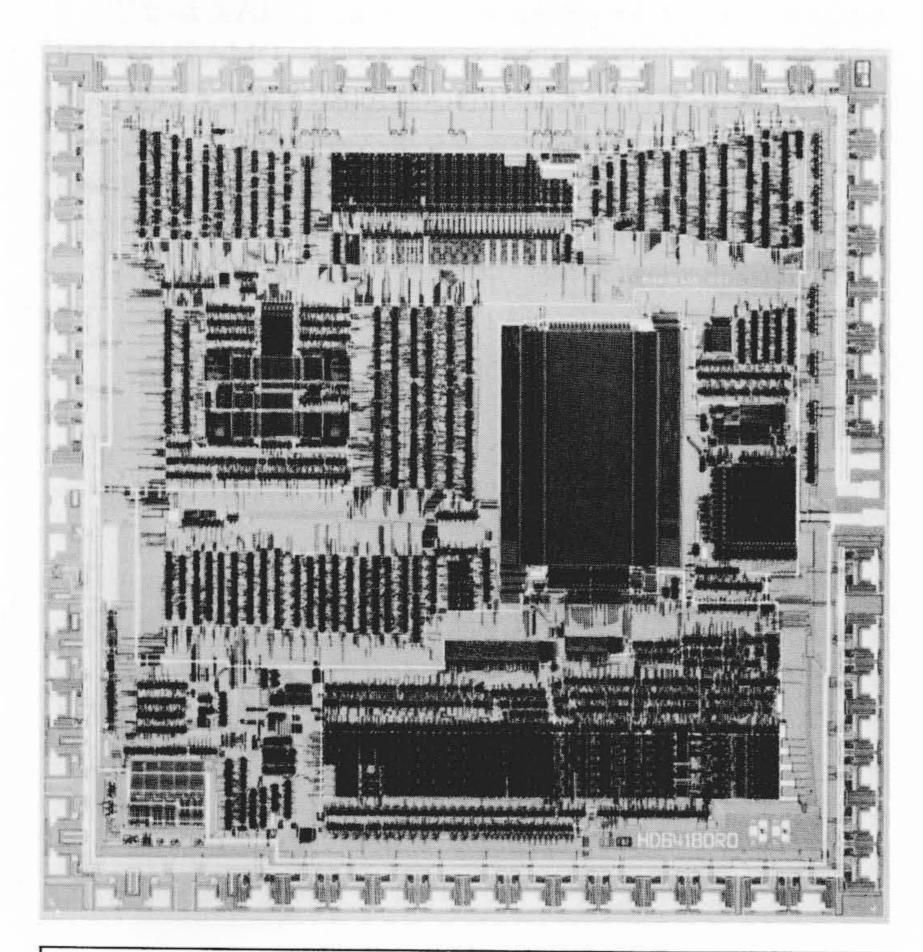

#### 4 設計技術2)

図12にHD64180のチップ写真を示す。2µm CMOSプロセス により、5.98×5.90mm<sup>2</sup>のチップ上に約4万5,000個のトラン ジスタを集積している。図12に示すように二つのプロセッサ で構成されている。一つはCPU、MMU、DMAC、割込みな どを制御するメインプロセッサ, もう一つは直列通信器, タ イマなどを制御するI/Oプロセッサである。これらはいずれも マイクロプログラムにより制御され、各々独立した実行部に より実行される。このように、従来ランダム論理で構成されて いたI/O部分にプロセッサ構成を採用し、論理の規則化、ハー ドウェアの最適化を図ったことにより多機能を実現した。

## 5 HD64180の応用例

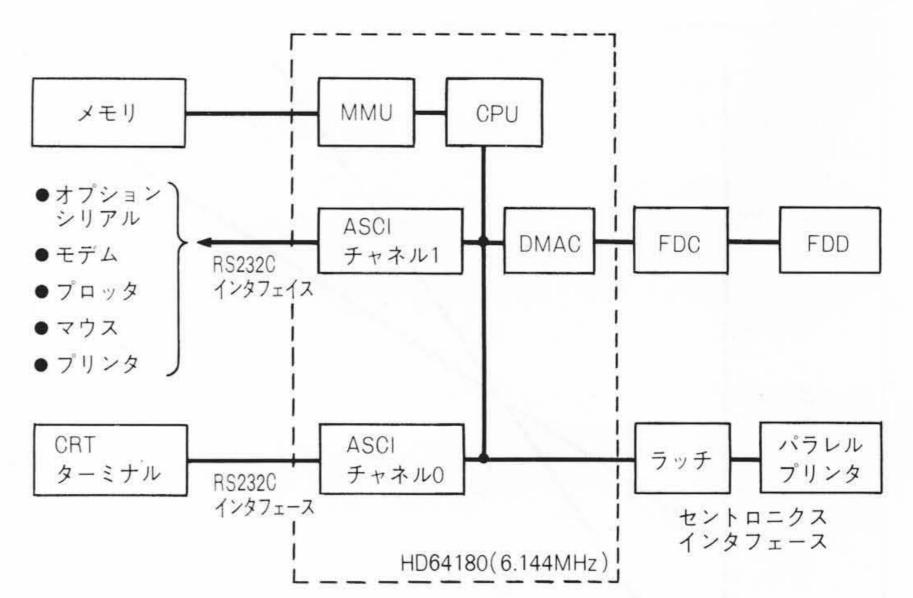

このHD64180の応用としては、MMU、DMACなどの機能 を生かせる大量のデータ処理を必要とする分野(パーソナルコ ンピュータ,ワードプロセッサなど)や,直列通信機能を使用 する分野(データ端末、POS/ECRなど)など、幅広い分野が考

図IO エッジ入力時のCPU 動作とDMA動作 スティネーションがI/O指定の場 合を, ↓は要求信号のサンプリ ングタイミングを示す。

図II レベル入力時のCPU 動作とDMA動作 \* はデ スティネーションがI/O指定で WAITサイクルが2の場合を,↓ は要求信号のサンプリングタイ ムを示す。

えられる。HD64180を使用することで多機能,小形のシステムを低価格で実現することができる。

例えば、HD64180を使用して次のようなデータ処理用の応用システム(例えばパーソナルコンピュータ)を実現できる。メモリは、MMUにより、256kバイト(HM50256×8)のDRAM、OSをRAM上に読み込むためのプログラムを格納するEPROM(HN27C64など)を実装する。また、内蔵のDMACやシリアル通信機能を利用することにより、FDDインタフェース、RS232Cインタフェースなどの機能を実現している。この応用システムのブロック図を図13に示す。

このシステムを従来のIC/LSIを使用して構成した場合, LSI は 5 個必要となり, B 5 サイズの大きさの基板となる。これに

図12 HD64180チップ写真 メインプロセッサとI/Oプロセッサの2プロセッサ構成である。5.98mm×5.90mmのチップ上に、約4万5,000個のトランジスタを集積している。

#### 主な機能

- CP/MPLUSシステム 256kバイトのメモリ

- ●RS232Cポート 2チャネル

- ●セントロニクスポート 1チャネル

- ●FDDインタフェース

注:略語説明 FDC(Floppy Disk Controller) FDD(Floppy Disk Driver)

図13 HD64180応用システム例 HD64180を使用したデータ処理システムのブロック図を示す。このシステム上には、256kバイトのメモリ、RS232Cインタフェース 2 チャネル、セントロニクスポート | チャネル、FDDインタフェースを装備している。

対しHD64180を使用すると、上記システムをはがき大サイズに収めることができる。

このシステムでは、512kバイトのメモリ空間をサポートする $CP/MPLUS^{*2}$ などの汎用OSの搭載が可能である。したがって、このOS上で動作するアプリケーションソフトウェアを利用することができる。

以上に述べたように、HD64180により既存のソフトウェアの活用、システムの小形化及びシステムVA(Value Analysis)を容易に実現でき、システムの高付加価値化を促進することができる。

#### 6 結 言

以上, HD64180についてその機能を中心に述べた。従来のソフトウェアとの互換性を保ちながら, 性能, 機能面では 8 ビットの枠を大きく越えたマイクロプロセッサを実現することができた。特にMMUによるアドレス空間の拡張は, 64kバイトの制限に束縛されてきた 8 ビットユーザーに対し, 8 ビットマイクロプロセッサの新たな応用の道を開いた。

今後,更にアドレス空間の拡張,各応用分野に最適な周辺機能の集積化,高速動作などの要求が強くなると考えられる。 HD64180のファミリ展開を行なうことにより,この要求にこたえてゆきたいと考えている。

#### 参考文献

- 1) T.W.Cantrell, et al.: Memory Management and I/O prove 8-bit Processors cannot be counted out: Electronic Design. 10, 303~312(Jan. 1985)

- H. Maejima, et al.: A CMOS Microprocessor with Instruction-controlled Register file and ROM, ISSCC Digest of Technical Papers, p.12~13(1985-2)

※2) CP/MPLUSは、米国ディジタルリサーチ社の商標である。