# ISSCC '86に見る半導体技術の動向

# Semiconductor Technology Trends at ISSCC '86

固体回路素子(IC, LSI)の分野で、世界最先端の技術が発表されるISSCCの昭和61年度の動向をまとめ、日立製作所からの発表論文について概説した。集積度向上に伴い多様化するVLSIの最先端を概観するとともに、日立製作所のVLSI開発活動の一端を併せて紹介する。

日立製作所からの論文は、メモリ、ロジック、通信、民生・アナログの広い分野で発表され、合計6件となっている。特に昭和61年度は、Hi-Bi CMOS技術による高速論理、メモリ回路など、高速指向の論文が新しい技術動向をリードするものとして注目されている。

浅井彰二郎\* Shôjirô Asai

下東勝博\*\* Katsuhiro Shimohigashi

前島英雄\*\*\* Hideo Maejima

## 1 緒 言

昭和61年のISSCC (International Solid-State Circuits Conference)は、2月19日から21日まで、米国カリフォルニア州のアナハイムで開催され、半導体を取り巻く厳しい経済環境にもかかわらず2,000人を超える研究者、技術者が一堂に会した。

今年も3日間の会期にわたって18の論文セッションと10のパネルセッションが開かれた。発表論文の件数は基調講演を除いて102件であり、そのうちレートニュースが15件である。近年、日本からの論文が半数近く採用されているが<sup>1)</sup>、今年も38件が日本の論文であった。

今年の基調講演は、J. Solomon (元 National Semiconductor社, 現在はLSI設計とCAD(Computer Aided Design) を専門とするSDA Systems社の社長〕によって行なわれた。 "Computer-Based Design for Tomorrow's Super Chip" と 題するこの講演は、いわゆるASIC(Application Specific Integrated Circuits, すなわち特定用途向けIC) 時代を迎え2), 100万個以上の素子を集積できる複雑なチップの設計上の問題 をいかに克服するかについて論じたものであり、その骨子は 次のようなものであった。『システム設計者は,今や1チップ に100万素子以上を集積できるハードウェア技術をいかに利用 するかの問題に直面している。このような大規模ICは, 必然 的に専用化方向へ向かう。したがって、複雑な専用ICの設計 を汎用品よりも少ない期間と費用で行なえる新しい設計手法 の確立が急務である。従来のゲートアレー, スタンダードセ ル方式は小規模のもの、もしくはプロトタイプには有効であ ろうが、100万素子以上をもつ将来のSuper Chipでは、高度に 自動化された階層形マクロセルアプローチが重要となろう。 「チップ設計はアーキテクチャレベルで、その詳細設計は自動 化で」を基本思想として,新しいCAD環境の創出を行なう必 要がある。』

一般論文での本年の傾向で注目されることは、マイクロコンピュータ、信号処理LSIなど各種プロセッサの発表が活発なことである。特に画像やデータベースの処理、制御用などの分野での特定用途向けプロセッサの発展が目覚ましい。メモリ分野では、4 MビットDRAM(ダイナミックメモリ)の先駆が発表されたのが注目を集めたほか、256kビットまでのSRAM(スタティックメモリ)での高速化の動向が目立った。ゲート

アレーの高速・高集積化やA(アナログ)-D(ディジタル)変換の高速化についても発表が多く、LSIの応用展開は多様化の一途をたどっている。

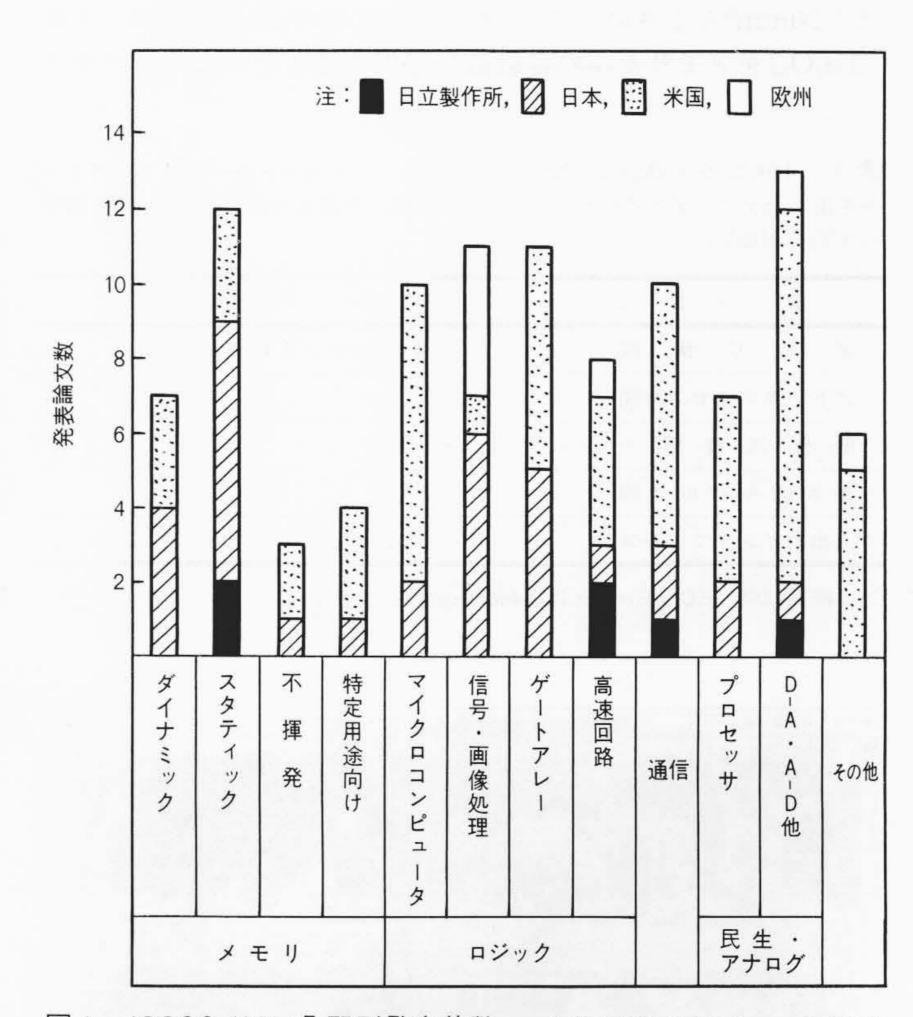

日立製作所からは、本年は**図1**に示すように6件の論文発表がなされた。発表内容はメモリ、論理LSI、通信、民生・アナログの各分野をカバーした。

以下, 2章で, メモリ, ロジック, 通信及び民生・アナログ, その他の4分野での技術動向, 及び日立製作所から発表された論文の要点と特徴について記述する。

図 I ISSCC '86の分野別発表件数 全発表件数は102件で、メモリ分野が25%、ロジック分野が39%、通信分野が10%、民生・アナログ分野が20%、その他6%の構成比である。

<sup>\*</sup> 日立製作所中央研究所 工学博士 \*\* 日立製作所中央研究所 \*\*\* 日立製作所日立研究所

# 2 分野別動向と日立製作所の活動状況

#### 2.1 メモリ分野

MOS (Metal Oxide Semiconductor) メモリ、特にDRAM は、最先端のプロセス技術をけん引する役目を果たしている。昭和61年のISSCCでも、 $0.8\sim1.0\mu$ mレベルの微細プロセス技術による実験的な  $4\,M$ ビットDRAMの発表が  $3\,$ 件あった。ここ1~2年で本格的  $4\,$ MビットDRAMの開発が行なわれるものと思われ、VLSIレベルでサブミクロン時代の到来は近い。

SRAMについては、今回高速素子の発表が相次いだ。MOS・SRAM又はBi CMOS(BipolarとCMOSとの複合構造)SRAMは、64kビットでアクセス時間(Typical値)13~15ns、256kビットで25~30nsの発表が中心となっている。また、Bipolar SRAMも16~32kビットで、アクセス時間(Typical値)で3~4nsとなっている。特定用途向けメモリ(Application Specific Memory)開発では、Video RAM³のほかにテレビジョンもしくはVCR(Video Cassette Recorder)用、レーダ用、キャッシュメモリ内蔵MMU(Memory Management Unit)などの発表があり多様化が進んでいる。

日立製作所からは、高速SRAMに関し、16kビットBipolar SRAM 及 び 64k ビット Hi-Bi CMOS (High performance Bipolar CMOS) SRAMの2件が発表された。以下、これら日立製作所からの発表論文の概要について述べる。

#### (1) 16kビットBipolar SRAM

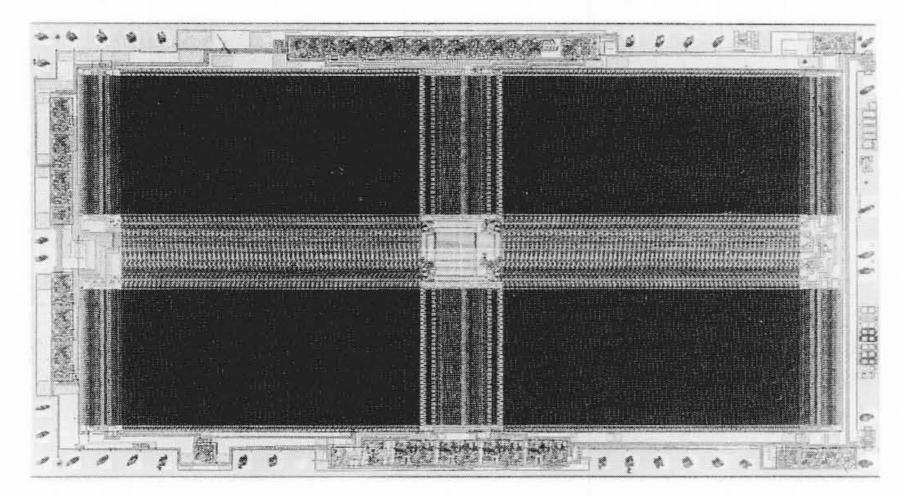

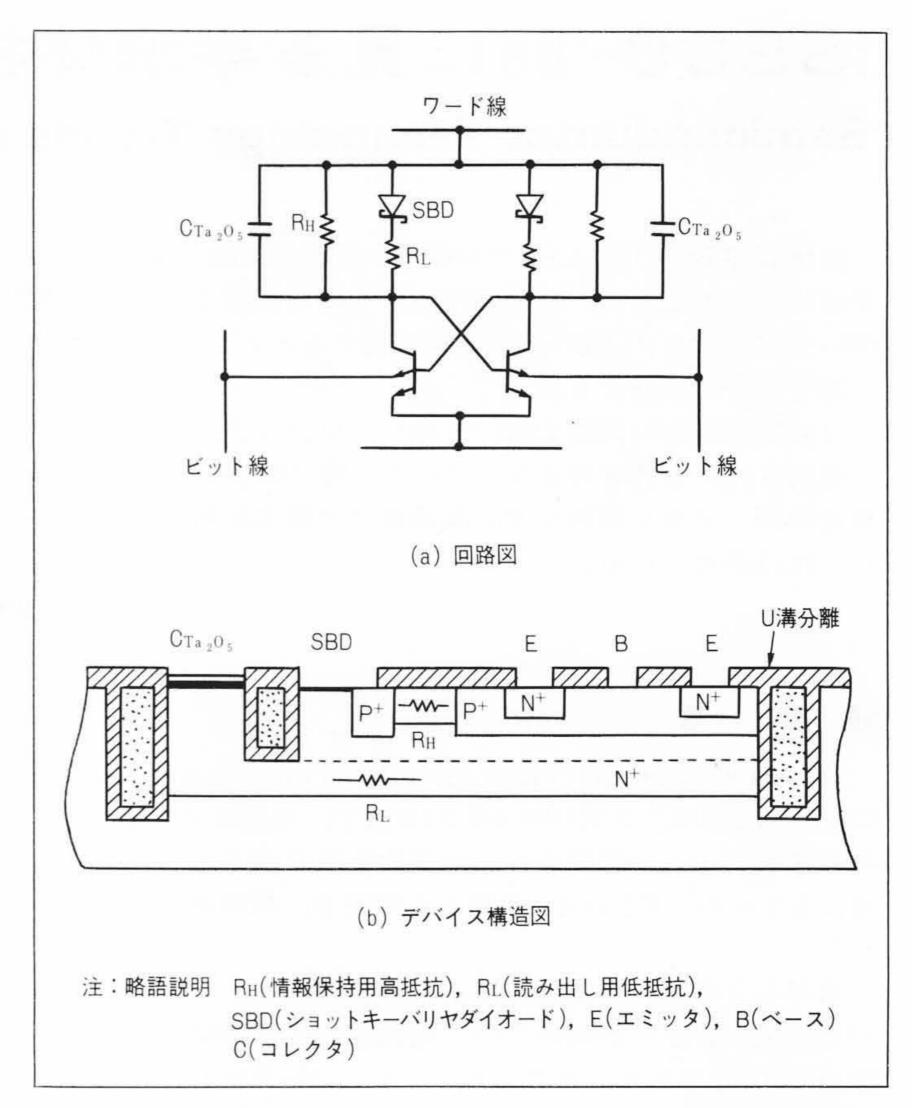

$1.0\mu$ mデザインルール,U溝分離技術を用いた16kビットRAMのチップ写真を図2に,素子特性を表1に示す。本RAMは,ECL(Emitter Coupled Logic)インタフェースで,アクセス時間(Typical値)が3.5nsと高速である。また,チップサイズも20mm $^2$ と小さい。これは,比誘電率の高い酸化タンタル( $Ta_2O_5$ )をメモリセルの容量部に採用することにより,メモリ

表 I 16kビットBipolar SRAMの特性 ショットキーバリヤダイオードを用いたデコーダ方式などの回路技術により、高速化が達成できた(特性はすべてTypical値)。

| 項目         | 特性            |

|------------|---------------|

| メモリ構成      | 4 kワード× 4 ビット |

| アドレスアクセス時間 | 3.5ns         |

| 動作消費電力     | 2.0W          |

| 書き込みパルス幅   | 2.0ns         |

| 入出力インタフェース | ECL           |

注:略語説明 ECL(Emitter Coupled Logic)

図 2 I6kビットBipolar SRAMのチップ写真 チップサイズは3.3×6.1mm²である。

図 3 16kビットBipolar SRAMのメモリセル 酸化タンタル膜を用いた記憶容量( $C_{Ta_2O_3}$ ), U溝分離技術により、メモリセル面積495 $\mu$ m<sup>2</sup>が実現できた。

セル面積を $495\mu$ m<sup>2</sup>と小さくできたためである。メモリセルの等価回路と素子構造を**図3**(a), (b)にそれぞれ示す。

#### (2) 64kビットHi-Bi CMOS SRAM

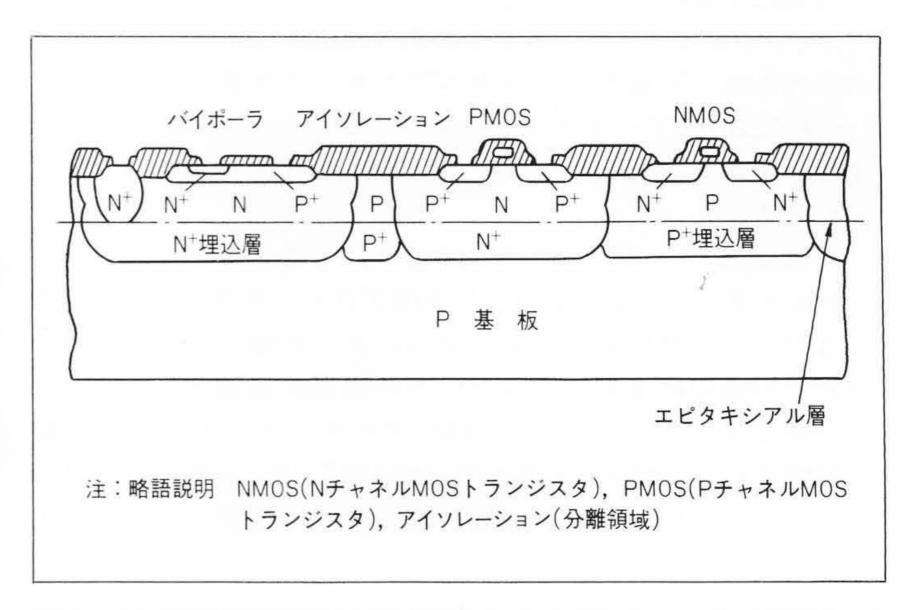

$2 \mu \text{m}$ デザインルール、Bipolar と CMOS複合構造 (Hi-Bi CMOS構造:図 4 )による 64 k ビット SRAMのチップ写真を図 5 に示す。メモリセルは、高集積化可能で作りやすいMOS構造 (4 MOSと 2 抵抗から成るフリップフロップ回路) とし、メモリセル駆動回路を高速・低電力特性を合わせもった Bi-CMOS複合回路とすることにより、高速で高集積の SRAMを実現した。表 2 に特性表を示す。

図 4 Hi-BiCMOSのデバイス構造 PMOS及びBipolarは、P基板上のN エピタキシアル層に、NMOSはPウエル内に作られる。

図 5 64kビットHi-BiCMOS SRAMのチップ写真 チップサイズは、 $4.4 \times 6.8$ mm²で、メモリセルサイズは230 $\mu$ m²である。

表 2 64kビットHi-BiCMOS SRAMの特性 Hi-BiCMOS技術により、 2μmデザインルールでCMOS 1.3μmデザインルール並みの性能が得られた。特性はすべてTypical値を示す。

| 項目         | 特性          |  |  |

|------------|-------------|--|--|

| メモリ構成      | 16kワード×4ビット |  |  |

| アドレスアクセス時間 | I3ns        |  |  |

| 動作消費電力     | 500mW       |  |  |

| 書き込みパルス幅   | 7 ns        |  |  |

| 入出力インタフェース | ECL         |  |  |

#### 2.2 ロジック分野

ロジック関係のセッションは、マイクロプロセッサ、特定 用途向けプロセッサ、信号及び画像処理プロセッサ、その他 高速ディジタル回路技術と幅が広い。各セッションごとの動 向を要約した後で日立製作所の発表論文を紹介する。

### (1) マイクロプロセッサ関係

32ビットマイクロプロセッサが4件あった。新しい汎用マイクロプロセッサのほか、Smalltalk専用のプロセッサ、RISCアーキテクチャを採用したプロセッサなど新しい流れがある。また、6チップ構成ながら汎用メインフレームのVLSI化の発表もあり、システムオンチップ化は着々と進展している。

# (2) 特定用途向けプロセッサ

ディジタル静止画像用や文字・図形統合ビデオシステム用 など、画像・図形処理指向が強い。

#### (3) 信号及び画像処理プロセッサ関係

信号処理プロセッサは、音声、通信の分野をねらった高速・高精度のプロセッサの開発が盛んである。一方、画像処理プロセッサ関係は、今回ビデオ信号のディジタル処理を行なうプロセッサを中心に7件の発表があり、活動は活発である。マイクロプログラム方式による実時間画像処理や適応フィルタリング法、オーバサンプリング法など多様な処理方式の発表があり、画像処理がLSI応用の一つの大きな分野となってきた。

#### (4) ゲートアレー関係

集積度の点では、44万個のトランジスタをもつCMOSマスタスライス、また速度の点では、ECLでゲート遅延時間0.15 nsの発表があった。シリコンの有効利用のため、配線領域にもアクティブ素子を配置するなどの工夫がある。EPROM

(Erasable Programmable Read Only Memory) もしくは EEPROM (Electrically Erasable PROM) とCMOSロジック をオンチップ化したプログラマブルロジックの発表が 4 件あり、1-2 kゲート相当の集積度である。

#### (5) 高速ディジタル回路関係

Bipolar ECL, Bi CMOS, GaAs, JJ (Josephson Junction) と高速素子技術が勢ぞろいし、速度を競った。それぞれ異なった応用回路で高速性を実証しているが、ゲート遅延でサブナノ秒、動作周波数で10GHzを超えるものとなっている。

次に日立製作所からの発表論文の要約を述べる。

#### (1) 60MHzディジタル処理用Bi CMOS回路

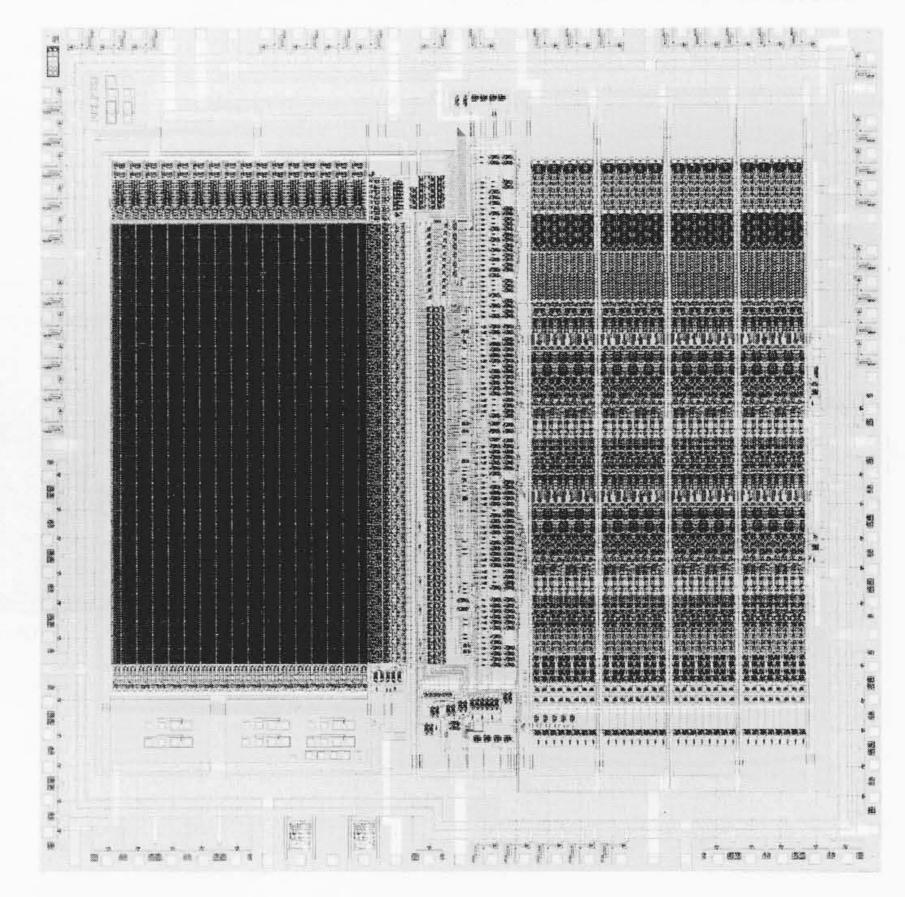

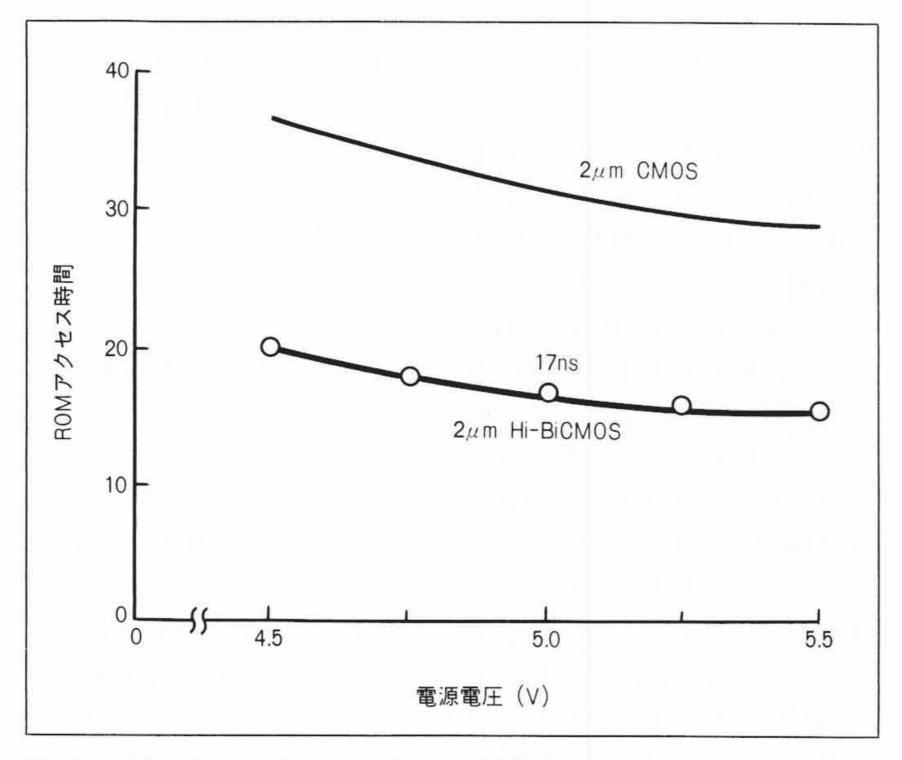

Bipolarの高速性とCMOSの高集積性を兼ね備えたBi CMOS構造(図4)のディジタルLSIへの応用を、図6に示す32 ビットの加算器及び64ビット×2kワードのROM(Read Only Memory)で検討した。デザインルールは2 $\mu$ mである。ROMのアクセス時間は、17nsと2 $\mu$ m CMOSに比べ約2倍高速である(図7)。加算器の速度もCMOSの約2倍であり、各種信号処理をはじめとする高速ディジタル回路への応用が期待できる。

# (2) ジョセフソンしきい値論理回路による 4 ビット乗算器と 3 ビット分周器

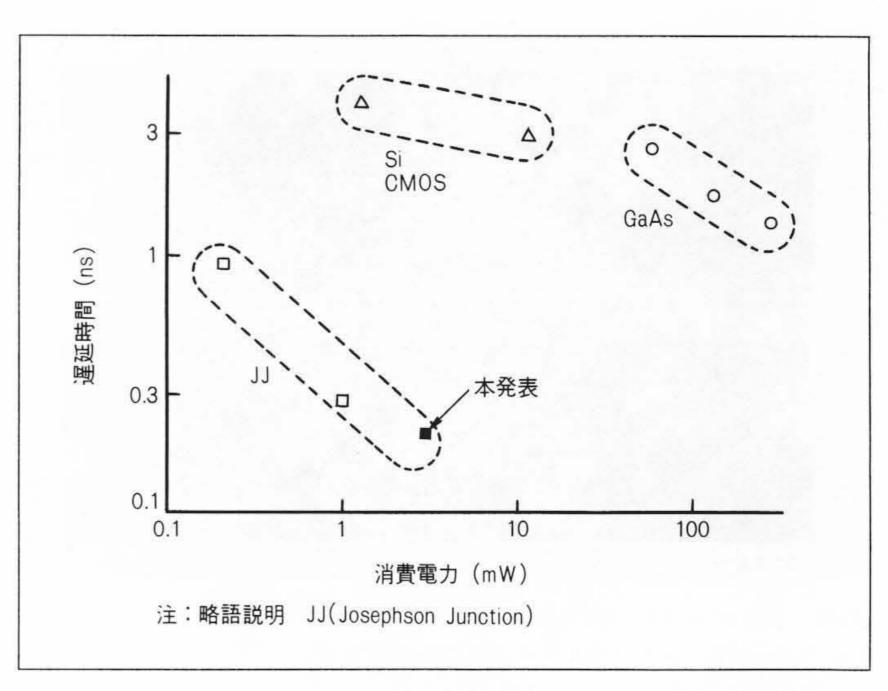

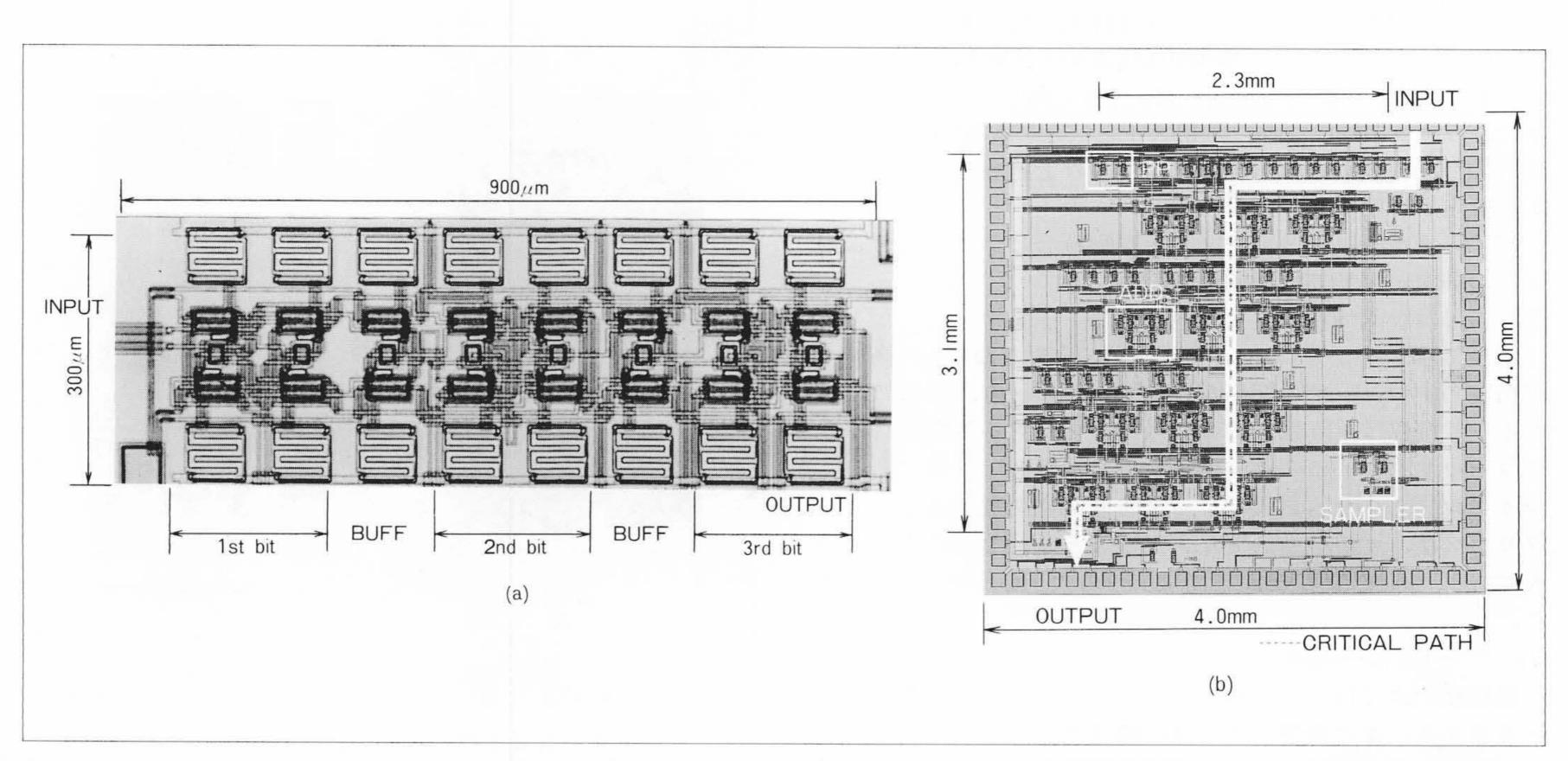

しきい値論理 (入力信号の合計が所定の値を超すと出力信号が出る論理方式)による、3ビット分周器と4ビット×4ビットの乗算器のチップ写真を図8(a)、(b)にそれぞれ示す。JJの面積は $1.5\mu$ m× $1.5\mu$ m、電極材料はNbN(窒化ニオブ)である。分周器の動作速度は2.2GHz、109ゲート、270個のJJをもつ加算器のクリティカルパスの遅延時間は、279psである。加算器の性能を、CMOS及びGaAsと比較して図9に示す。速度はGaAsの約10倍で、消費電力はCMOS並みの高性能が得られた。

# 2.3 通信分野

通信用IC, LSIは、音声帯域向けと光通信用に分けられる。

図 6 Hi-BiCMOSによる32ビット加算器(右)とROM(左)のチップ写真 チップサイズは9.2mm平方である。ROMサイズは  $2 k 7 - F \times 64$ ビット、デザインルールは $2 \mu m$ である。

音声帯域向けでは、2,400ビット/秒のモデムが2件、ライン回路関係が2件、ADC/DAC(Analog-to-Digital Converter/Digital-to-Analog Converter)が2件となっている。今回はさまざまな光通信用高速ICの発表があり、活動は活発である。すなわち、50Mビット/秒のデータリンク用CMOS ICや、200Mビット/秒の光ファイバ用リンク回路、更には2Gビット/秒と超高速で半導体レーザを変調する $1\mu$ mゲートのNMOSドライバの発表が相次いだ。

次に日立製作所からの発表論文の要約を述べる。

#### (1) 音声帯域15ビット補間形コンバータチップセット

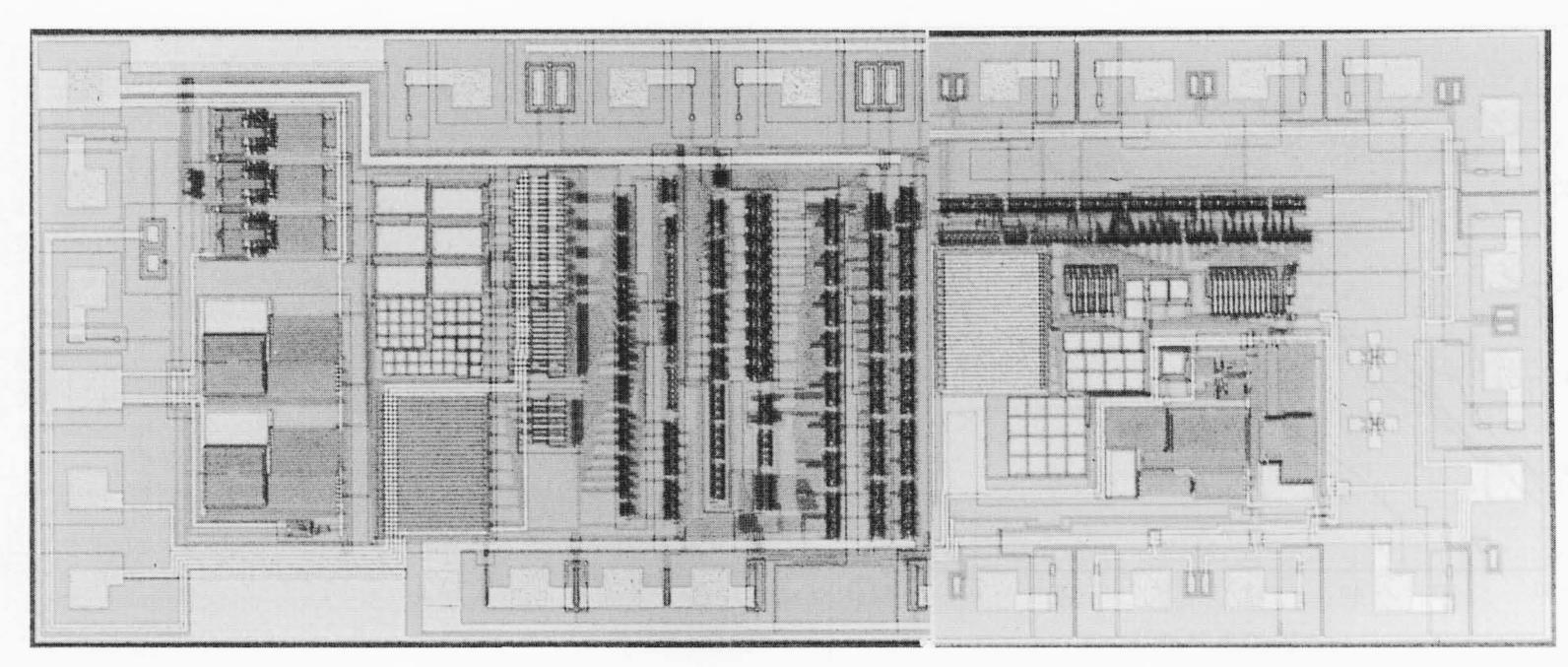

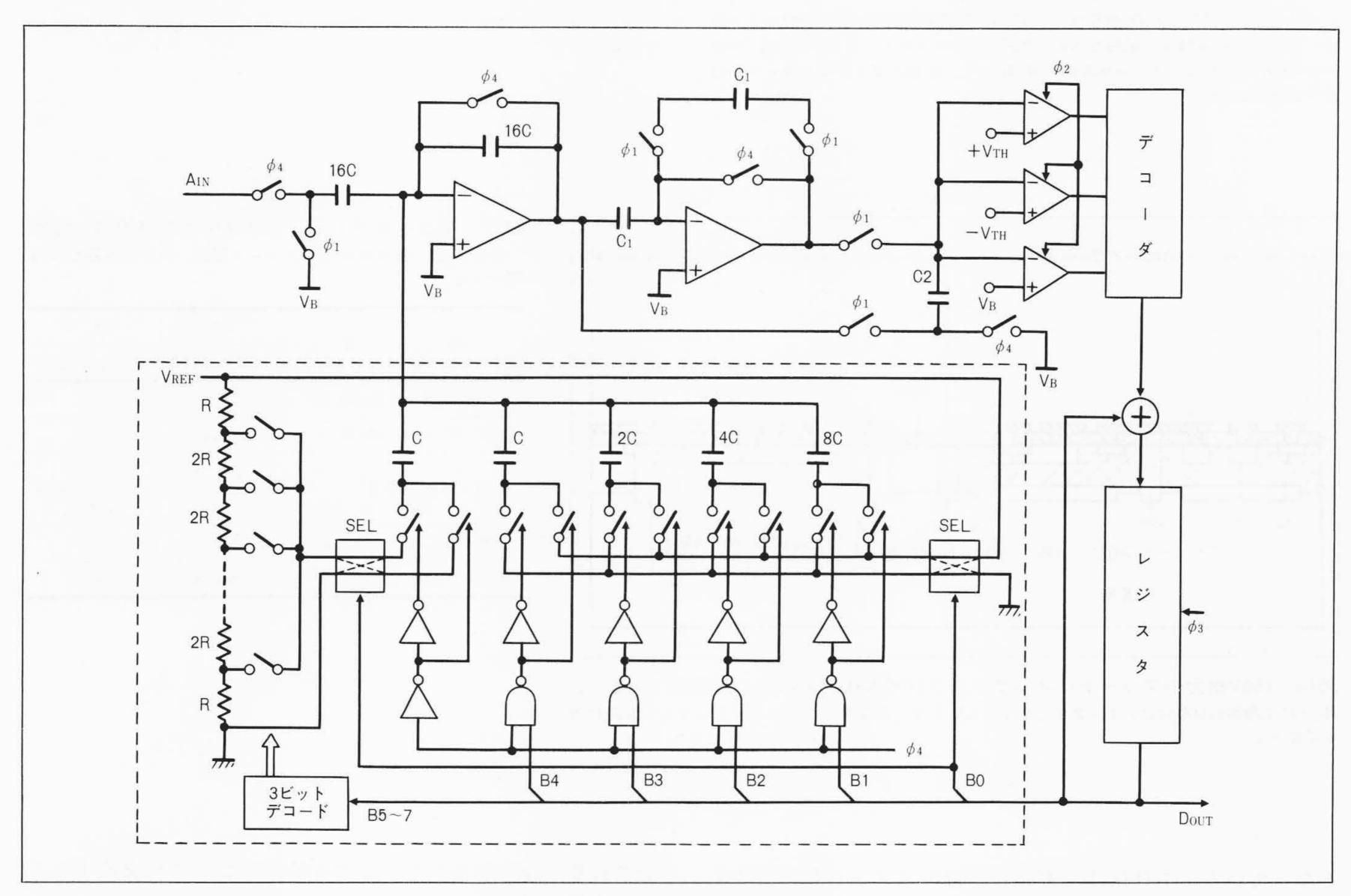

ディジタルCODEC(Coder-Decoder)用,15ビットの分解能をもつADC/DACのチップセットの写真を**図10**に示す。 VLSI化に適合し,高分解能を得るため補間形エンコーダを

図 9 4 ビット×4 ビット乗算器の性能 ジョセフソン素子の性能を、 高速半導体素子GaAsと低電力半導体素子CMOSとの比較で示した。

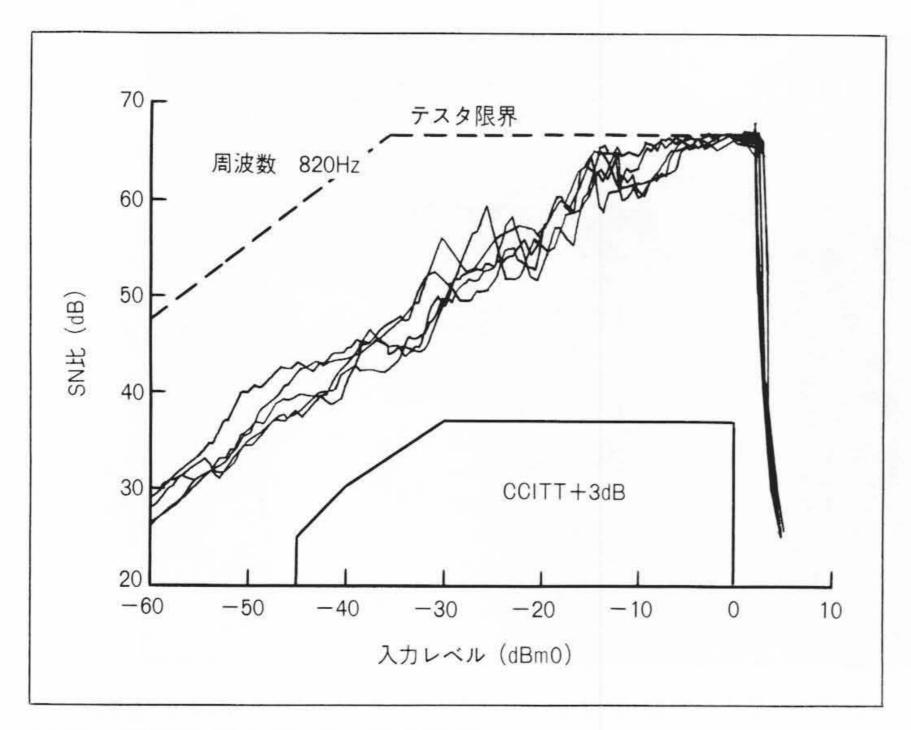

採用した。図11にADCの回路図を示す。DACの回路は、このADC内に使用されているDAC(点線内)と同様な回路である。基本サンプリング周波数は、 $1,024kHz(\phi_1 \sim \phi_4)$ であり、 $2\mu m$  デザインルールのCMOSで実現できた。これらADC/DACの総合性能を図12に示す。ダイナミックレンジは93dBm0で、これは15ビットの入力電圧分解能に相当する。

#### 2.4 民生・アナログ分野

アナログ処理、センサ及びインタフェース、D-Aコンバータ・A-Dコンバータが主なセッションである。アナログ分野ではあるが、高機能化及び使い勝手をよくするため、ディジタル回路も共存させるアナログ・ディジタル混在が大きな技術の流れであり、今回もカラーマップメモリ(38ビット×12ビット)内蔵のビデオディスプレイ用DACが発表された。また、アナログ処理のセッションでもパワーMOSとCMOSロジック

図 8 ジョセフソンしきい値論理による 3 ビット分周器(a)と 4 ビット× 4 ビット乗算器(b)のチップ写真 分周器の面積は0.3×0.9mm², 乗算器は3.1×4.0mm²である。

図10 音声帯域15ビット補間形コンバータチップセットの写真 ADC(左)のチップサイズは2.0×2.8mm², DAC(右)のチップサイズは2.0×1.9mm²である[CMOS 2μmデザインルール使用]。

図II 補間形ADCの回路図 8ビットのDAC(点線内)及び4レベルの量子化回路を中心に構成されている。

をオンチップ化した発表が2件あった。イメージセンサ関係は、高感度化に加え、高解像度化が進んでおり、今回画素数970×1,280、約1,000TV本の解像度をもつイメージセンサが発表されている。A-Dコンバータでは、オーディオ用に15ビット以上の分解能をもつものが発表されるとともに、250MHz(8ビット)と高速のコンバータがBipolar技術により実現されている。一方、DACはビデオ用が中心で、1,000×1,000の高精細ディスプレイ用のDACも発表された。

次に日立製作所からの発表論文の要約を述べる。

## (1) 150V出力のフラットパネル ディスプレイ制御用IC

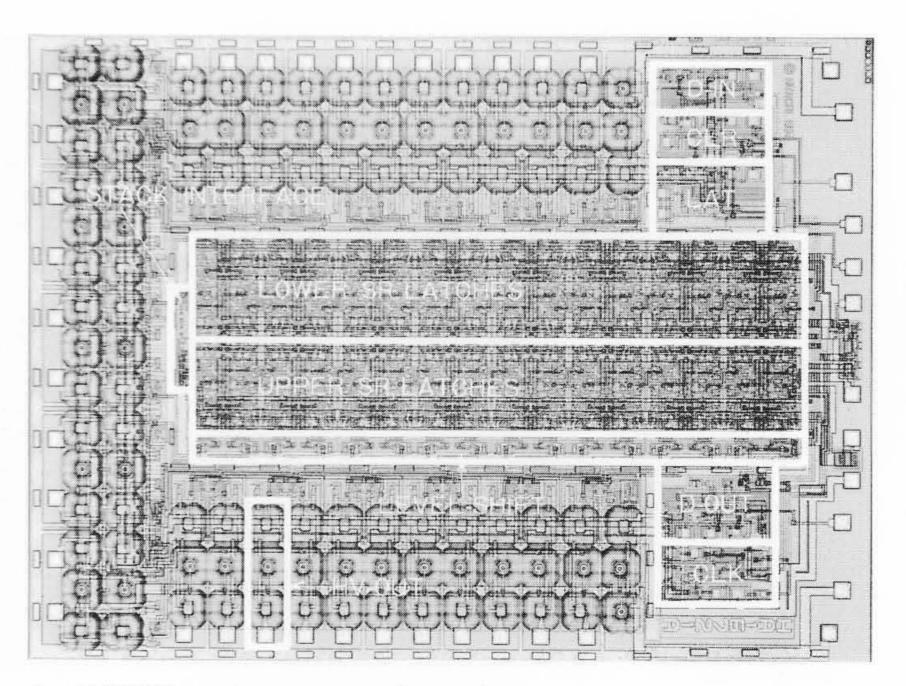

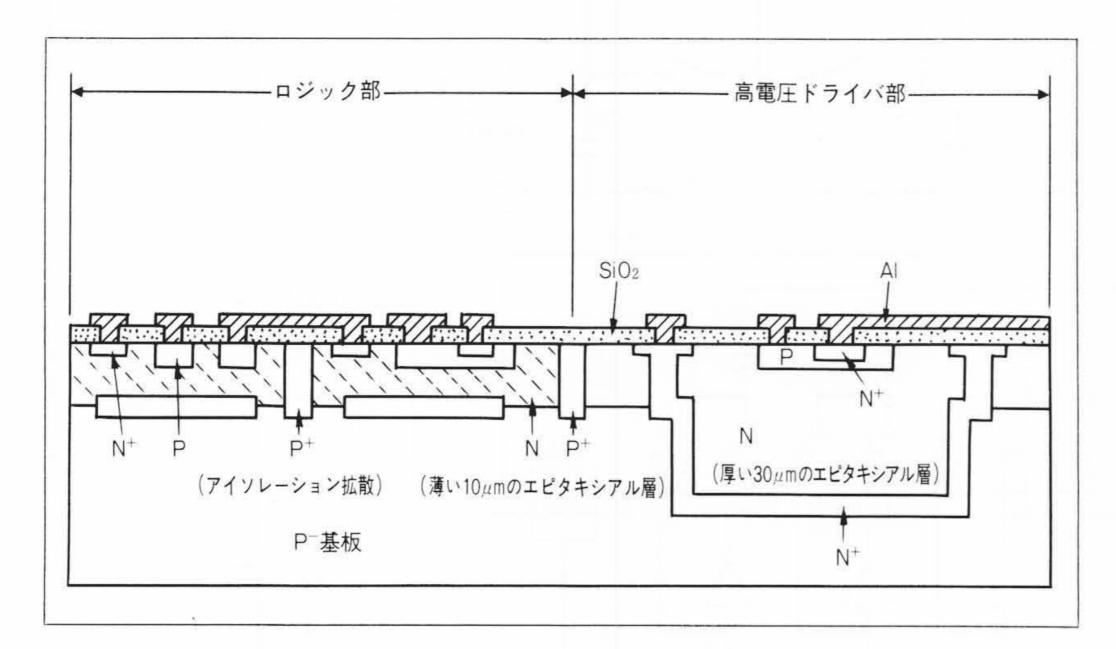

150Vの高電圧ドライバと制御ロジックとを一体化した,フラットパネル用蛍光表示管駆動ICをバイポーラ技術を用いて開発した。図13にチップ写真を示す。ロジック部は,32ビットのシフトレジスタ及びラッチ回路から成り,ドライバは32個で32チャネルを駆動する。図14は,本制御用ICの素子断面図で,ロジック部と高電圧部をそれぞれ $10\mu$ mと $30\mu$ mのエピタキシアル層上に形成した。これによりアイソレーション用拡散は薄い $10\mu$ mの部分だけに限定でき,作りやすいプロセス

図12 補間形ADC/DACの総合性能 入力レベル単位(dBm0)は、交換基準電力(交換基準点で I mW を与える電力)に対する電力をデシベル(dB)で示してある。(CCITT+3dB)の線は、CCITT(国際電信電話諮問委員会)による規格に3dBの余裕を加えた範囲を示す。本図では省略されているが、本ADC/DACのSN比が3dBとなる入力レベルは-90dBm0で、総合のダイナミックレンジは最大93dBm0である。

注:略語説明 SR(シフトレジスタ), D-IN(データ入力), D-OUT(データ出力), HV-OUT(高電圧出力), CLK(クロック)

図13 150V出力のフラットパネルディスプレイ制御用ICのチップ 写真 蛍光表示管のアノード駆動用チップで、チップサイズは5.0×6.6mm² である。

図14 150V出力のフラットパネルディスプレイ制御用ICの素子断面図 10μmと30μmの2種類のN形エピタキシアル層を用いることで、高電圧部の深いアイソレーション用拡散を不要とした。

表 3 フラットパネルディスプレイ制御用ICの特性 本技術は、蛍光表示管のアノード駆動、グリッド駆動に適 用できる。

| 西        | 目   | 特      | 性      |

|----------|-----|--------|--------|

| 項        |     | アノード駆動 | グリッド駆動 |

| ロジック部    | 電 圧 | 7 V    | 7 V    |

| ドライバ部電圧  |     | 150∨   | 150V   |

| ビニノバ山土電流 | ソース | 0.2mA  | 25mA   |

| ドライバ出力電流 | シンク | 2 mA   | 2 mA   |

| 動作周波     | 数   | 7 MHz  | I MHz  |

| 消費電      | カ   | 650mW  | 650mW  |

となっている。本技術は、蛍光表示管のアノードもしくはグリッド駆動に適用できる。特性表を表3に示す。

# 3 結 言

以上、昭和61年のISSCCに見られる技術動向と日立製作所からの発表論文について概観した。MOSメモリを中心とする高集積・高速化の基本技術での研究開発努力とその成果の集積には改めて目を見張るものがある。また、システムの機能と性能の高度化が、マイクロコンピュータ・信号処理LSI・ゲートアレー・A-D変換LSIなどに与える推進力は顕著であり、今後のLSI研究開発ではシステム部門・半導体部門の緊密な連係と、これを支える新しいCAD環境の創出が必要となろう。ISSCCは技術発表と国際交流の場として今後とも重要な学

会であり、論文発表を中心とする積極的な寄与を継続することが重要である。

# 参考文献

- 1) 久保,外:ISSCCの動向と日立製作所の発表論文,日立評論,67,8,577~582(昭60-5)

- 2) 専用LSIの台頭が目立つISSCC82, 日経エレクトロニクス, No. 285, pp.58~61(1982-5)

- S. Ishimoto, et al.: A 256k Dual Port Memory, ISSCC Digest of Technical Papers, pp.38~39(1985-2)