# 4 ビットシングルチップマイクロコンピュータの モジュール展開

### Modular Chip Design Approach for 4bit Single Chip Microcomputer

4ビットシングルチップマイクロコンピュータは、VTRなどの民生機器を中心に応用され、ニーズの多様化とともに高機能化・高性能化が進んでいる。更に、高いコストパフォーマンスと商品計画に合致した市場競争力のあるマイクロコンピュータがタイムリーに開発されることが期待されている。

HMCS400シリーズのマイクロコンピュータ開発では、シリコンチップを幾つかの機能モジュールと標準化したモジュール間インタフェースに分割したモジュールアーキテクチャの構築に成功した。この設計手法により、機能モジュールの再利用とその設計資産の有効活用がCAD技術を併用することにより効果的に行なえ、開発期間の短縮及び設計品質の向上を図ることができた。

#### 1 緒 言

4ビットシングルチップマイクロコンピュータ(以下, 4ビットマイクロコンピュータと略称する。)は、VTR(Video Tape Recorder)などの民生機器をはじめとして、電話機、OA(Office Automation)機器、産業用制御機器などに応用されている。マイクロコンピュータを応用した商品は、急進する技術革新とニーズの多様化により、開発競争が一段と激しくなっている。応用機器の高機能化、高性能化、高信頼化とともに、商品のライフサイクルの短期化及び高いコストパフォーマンスの追求がある。マイクロコンピュータは商品を構成するキーパーツの一つであり、開発期間を短縮し応用機器の商品計画にタイムリーに一致させることが必要である。

4ビットマイクロコンピュータ設計過程のうちで、設計工数のかかるのは論理設計、テスティング設計及びレイアウト設計である。このうちレイアウト設計は、論理図入力によるCAD(Computer Aided Design)化が急速に進んでおり、多品種少量の設計に適した方式として、ゲートアレーの自動レイアウト、階層化レイアウトなどがある。自動レイアウトは、現在のところマニュアルレイアウトに比べて、集積密度の点で劣るものの、多様化したニーズの中でますますその重要性は高まっている。

このような流れの中で、コア アーキテクチャの性能向上と設計法の改良を行なったHMCS400シリーズの製品化を行なった。階層設計手法を採用したHMCS400シリーズのモジュール展開では、CADを活用した豊富な品種展開とプログラム開発用サポートツールの充実を図っていく計画である。特にマスクROM(Read Only Memory) 品との同期化を行なうために評価用デバイスとして、EPROM(Erasable and Programmable ROM) 搭載形及びEPROM内蔵形マイクロコンピュータの品ぞろえを行ない、顧客ニーズに立脚した製品開発を推進している。

#### 2 HMCS400シリーズの設計概要

HMCS400シリーズでは、従来のHMCS40シリーズのソフトウェア資産が継承できるとともに、最新のコア アーキテクチ

ャにより性能を飛躍的に向上させたばかりでなく、顧客ニーズにタイムリーに対応できるモジュール アーキテクチャの構築に成功した。HMCS400シリーズの開発目標は次の3点に置いている。

- (1) 標準化による容易な品種展開

- (2) 開発期間の短縮

- (3) 品質の確保

以上を達成するために、設計法として階層設計ができるモジュール方式設計を導入し、貴重な設計資産の再利用とCAD 援用による設計の自動化を推進した。

#### 3 モジュール方式設計

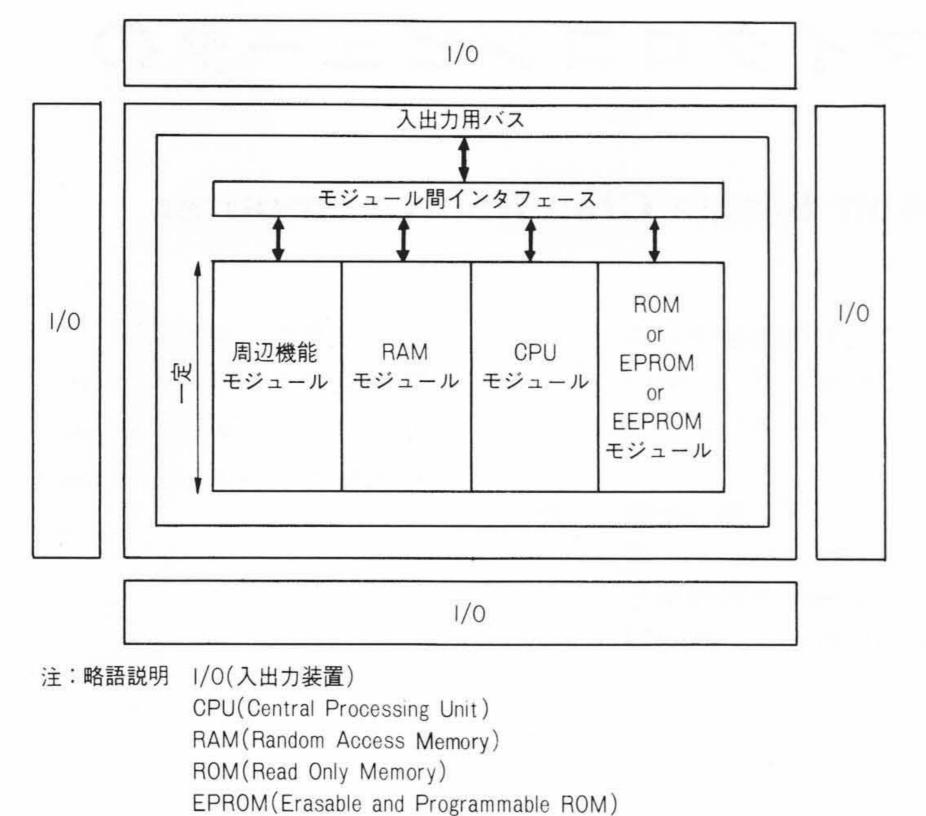

HMCS400シリーズでは、論理設計の段階で機能ブロックに分割する方式をとっており、論理図及びレイアウト図が図1に示すようなモジュール構造をとる。モジュール方式設計の最大の特徴は、各機能モジュールが完全に分離され、モジュール間インタフェースによってだけ結合していることであり、チップ設計上各機能モジュールの再利用を容易に行なえるところにある。すなわち、(1)機能モジュールごとにモジュール分割が明確に定義されている。(2)モジュール間インタフェースが明確に定義されている。(3) CADシステムに適用しやすい階層構造になっている。(4)機能モジュールの物理的な大きさは、一辺の長さをほぼ一定にし幅方向に展開できるようにしている。

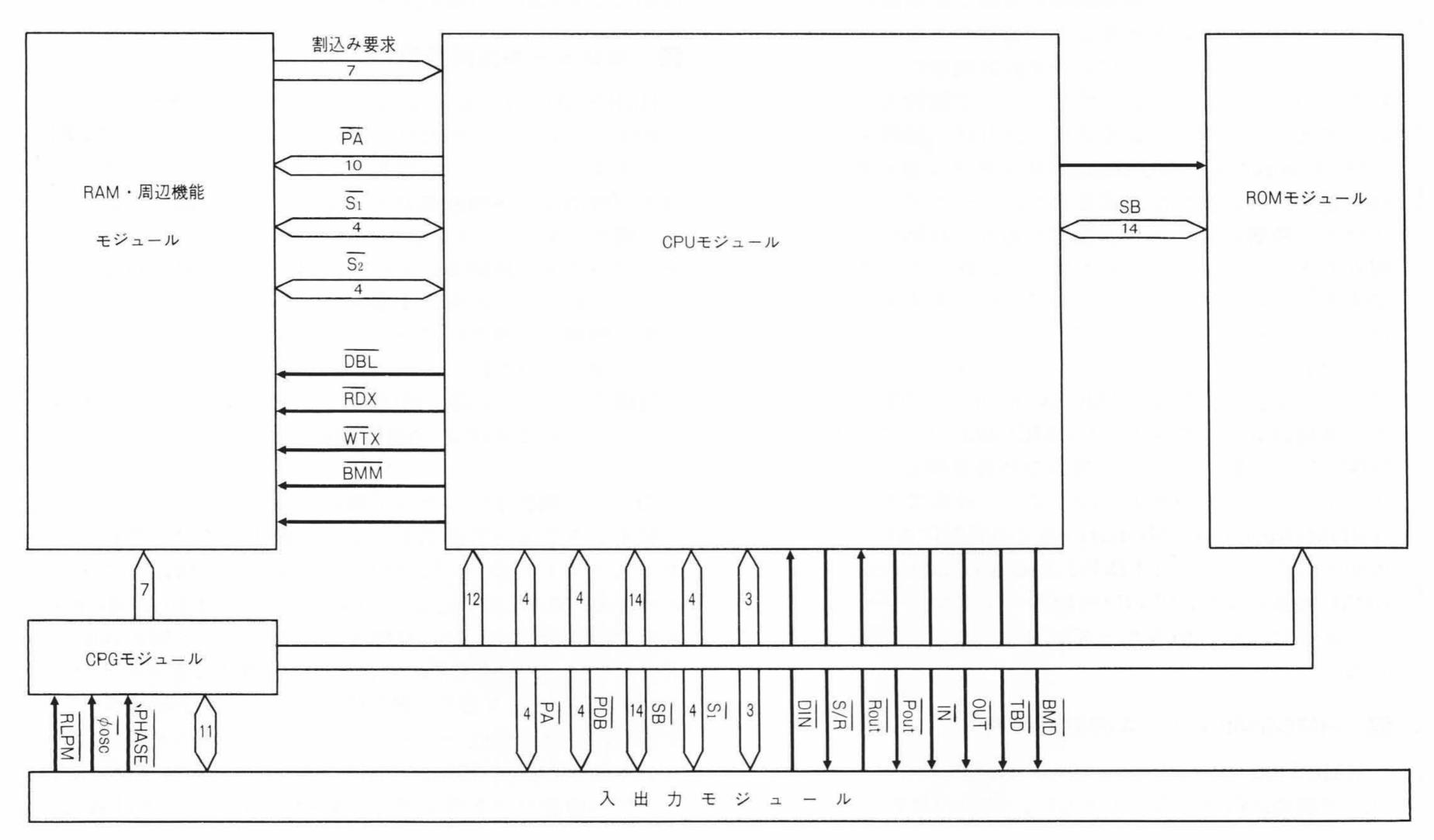

図2に各機能モジュールを接続する標準化されたモジュール間インタフェースを示す。また, $\mathbf{z}$ 1に標準化されたデータバス,アドレスバス及び制御信号を示す。機能モジュールの分割は,図1に示したようにROM,RAM,CPU,周辺機能,入出力の5分割とした。品種展開上重要となる周辺機能ハードウェアは,RAMアドレス空間上に配置されるメモリマップドI/O方式をとっており,RAMアドレス信号( $\overline{PA}$ )をデコードするだけで周辺機能ハードウェア制御用レジスタ及びデータレジスタの読出し,書込みの制御ができる。したがって,RAM及び周辺機能ハードウェアは,RAMアドレスバス( $\overline{PA}$ )とデ

<sup>\*</sup> 日立製作所武蔵工場 \*\* 日立マイクロコンピュータエンジニアリング株式会社

図 I HMCS400シリーズの機能モジュール構成 各機能モジュールの組合せ及びモジュールの切り口を分かりやすくするために使用する。

EEPROM(Electrically Erasable and Programmable ROM)

ータバス $(\overline{S}_1, \overline{S}_2)$ ,及び数本の標準制御信号だけで制御されている。

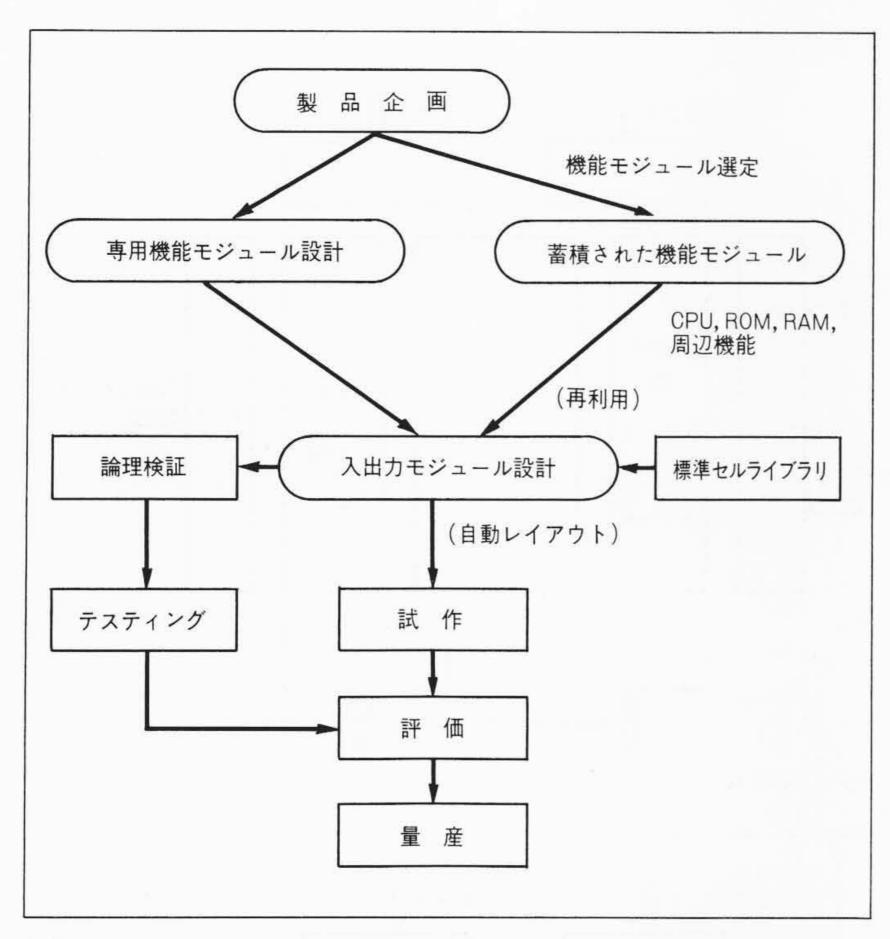

HMCS400シリーズのモジュール方式設計手順を**図3**に示す。顧客要求に基づいた製品企画を行ない既存モジュールの選定と新規機能モジュールの設計を行なう。それらの機能モ

表 | モジュール間インタフェース信号の動作 信号の名称と動作 説明のために使用する。

|        | 分 類                  | 信号名称                                       | 動作                               |  |  |  |

|--------|----------------------|--------------------------------------------|----------------------------------|--|--|--|

| 標準バス   |                      | SB                                         | プログラムカウンタ・ROMデータ<br>のマルチプレックスバス  |  |  |  |

|        |                      | $\overline{S_1}$ , $\overline{S_2}$        | RAM・周辺・入出力回路の入力・<br>出力データバス      |  |  |  |

|        |                      | PA                                         | RAM・周辺・入出力回路のアドレ<br>スバス          |  |  |  |

|        |                      | PDB                                        | 入力データ・出力データのマルチ<br>プレックスバス       |  |  |  |

| 標準制御信号 | RAM·周<br>辺機能制<br>御信号 | DBL, RDx, WTx, BMM                         | RAMの書込み・読出し・ビット操作・Push-Popを制御する。 |  |  |  |

|        | CPG制御<br>信号          | NFET, INToc, LPM, RPO<br>PHASE, posc, RLPM | 低消費電力モードを含めたCPG動作を制御する。          |  |  |  |

|        | 入出力制<br>御信号          | DIN, S/R, Rout, Pout IN, OUT, TBD, BMD     | Dポート,Rポートの書込み・読出し・動作モードを制御する。    |  |  |  |

|        | その他制御信号              |                                            |                                  |  |  |  |

注:略語説明 CPG(Clock Pulse Generator)

ジュールの組合せと入出力モジュールの設計を合わせてチップ設計を行なう。一方、チップ設計で機能モジュールの再利用があっても、入出力モジュールの機能変更、端子数の変更の場合が多く、入出力モジュールのレイアウト変更は不可欠である。そこで、設計工数の低減を図るために本設計法で取り扱うデータを素子ゲートレベル、機能ブロックレベル、モ

注:略語説明 CPG(Clock Pulse Generator), SB(Standard Bus)

図 2 標準化されたモジュール間インタフェース(無記名はその他の標準制御信号,表 | 参照) モジュール間インタフェースが標準化されていることを示す。

図 3 HMCS400シリーズのモジュール方式設計手順 モジュール 方式設計法の開発手順を示す。

ジュールレベル及びチップレベルに階層化を行ない, CADシステムが適用しやすい方式としている。現在, チップ面積を考慮して, 入出力モジュールを除く機能モジュールはマニュアルレイアウトにより最適設計を行ない, 入出力モジュールはCADによる自動レイアウトを導入している。本自動レイアウトでは, チップ面積の60~70%を占める内部の機能モジュールと周辺のモジュール間インタフェース及び入出力ハードウェアの配置・配線を行なっている。また, 標準セルライブラリと機能モジュールの整備・拡充により広範なチップ設計が可能となっている。更に, モジュール構造を採用したテスト技術及び特性評価合理化技術も製品設計の生産性を向上させる上で重要であり, 合わせて開発した。

#### 4 HMCS400シリーズのモジュール展開

HMCS400シリーズは、ソフト生産性向上の要求に対して、応用プログラムを更に組みやすくするために、演算命令の強化及び命令セットの見通しを行なうと同時に、直接アドレッシングモードを採用するなどアドレッシングの強化拡充を行なった。また、ROM部が10ビット/1ワードで構成されているため、99命令中76命令が1ワードで構成でき、少ないステップ数で効率的にプログラムを作成することができる。

応用システムのコスト低減要求に対しては、シリアル通信機能、タイマ機能、高耐圧回路を標準装備し、アナログ回路、表示用回路などの専用ハードウェアを内蔵することによって、外付部品の低減及び外付回路の簡素化を行なっている。

HMCS400シリーズがHMCS40シリーズから改良した主な点は、次の6項目である。

(1) ROM/RAM容量の拡大

ROMARTING量・バルス ROM最大:16k×10ビット RAM最大:1k×4ビット

- (2) HMCS40シリーズからの移行が容易なアーキテクチャ

- (3) 10ビット/1命令の強みを生かした1サイクル1命令動作

- (4) 高速動作最大目標 0.5 µs

- (5) モジュール方式設計による周辺機能の柔軟な拡張性

- (6) プログラム開発支援ツールの充実

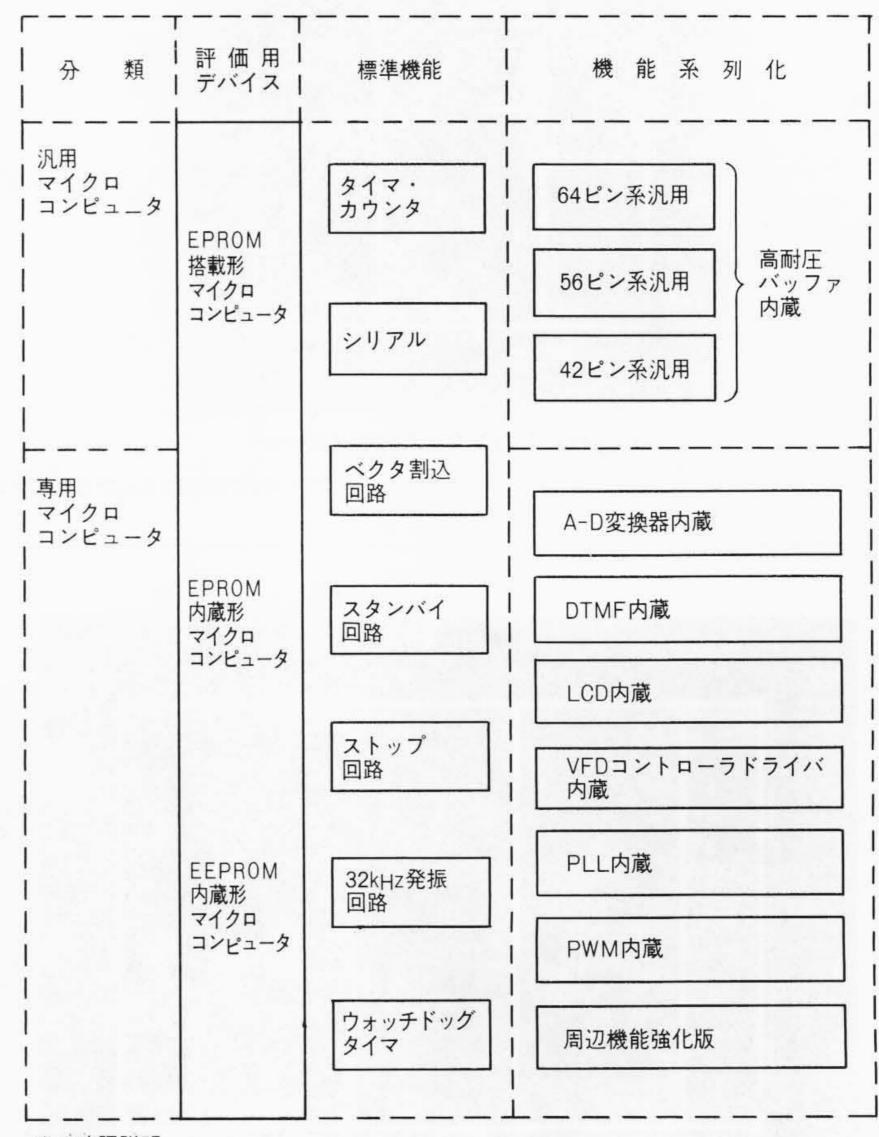

HMCS400シリーズの製品分類は、図4に示すように汎用マイクロコンピュータと専用マイクロコンピュータから構成される。汎用マイクロコンピュータについてはほぼ開発を完了し、図5のようなモジュール方式設計手法に従い製品ラインアップ(表2)を行なった。ROM、RAM、周辺機能、I/O及びパッケージの豊富なバリエーションの中から応用システムに合致した4ビットマイクロコンピュータを選択することができる。

現在、特定の応用分野を指向した専用マイクロコンピュータの開発要求が一段と強くなっており、HMCS400シリーズでもこの流れに対応していくために、次のような周辺機能内蔵化を進めている。内蔵する専用周辺機能としては、A-D変換器、電話機用のDTMF(Dual Tone Multi Frequency)回路と大容量データメモリ、蛍光表示管、LED(Light Emitting Diode)及びLCD(Liquid Crystal Display)用の表示用コントローラ・ドライバ、PLL (Phase-Locked Loop)及びPWM (Pulse Width Modulation)によるディジタルチューニング機能などを計画している。更に、HMCS400シリーズは今後ソフトウェア開発を含めて使い勝手のよい製品の品ぞろえを強力に進めてゆく予定である。

注:略語説明

DTMF(Dual Tone Multi Frequency)

PLL(Phase-Locked Loop)

PWM(Pulse Width Modulation)

VFD(Vacuum Florescent Display)

LCD(Liquid Crystal Display)

図 4 HMCS400シリーズ品種展開計画 系列別製品展開計画を示す。

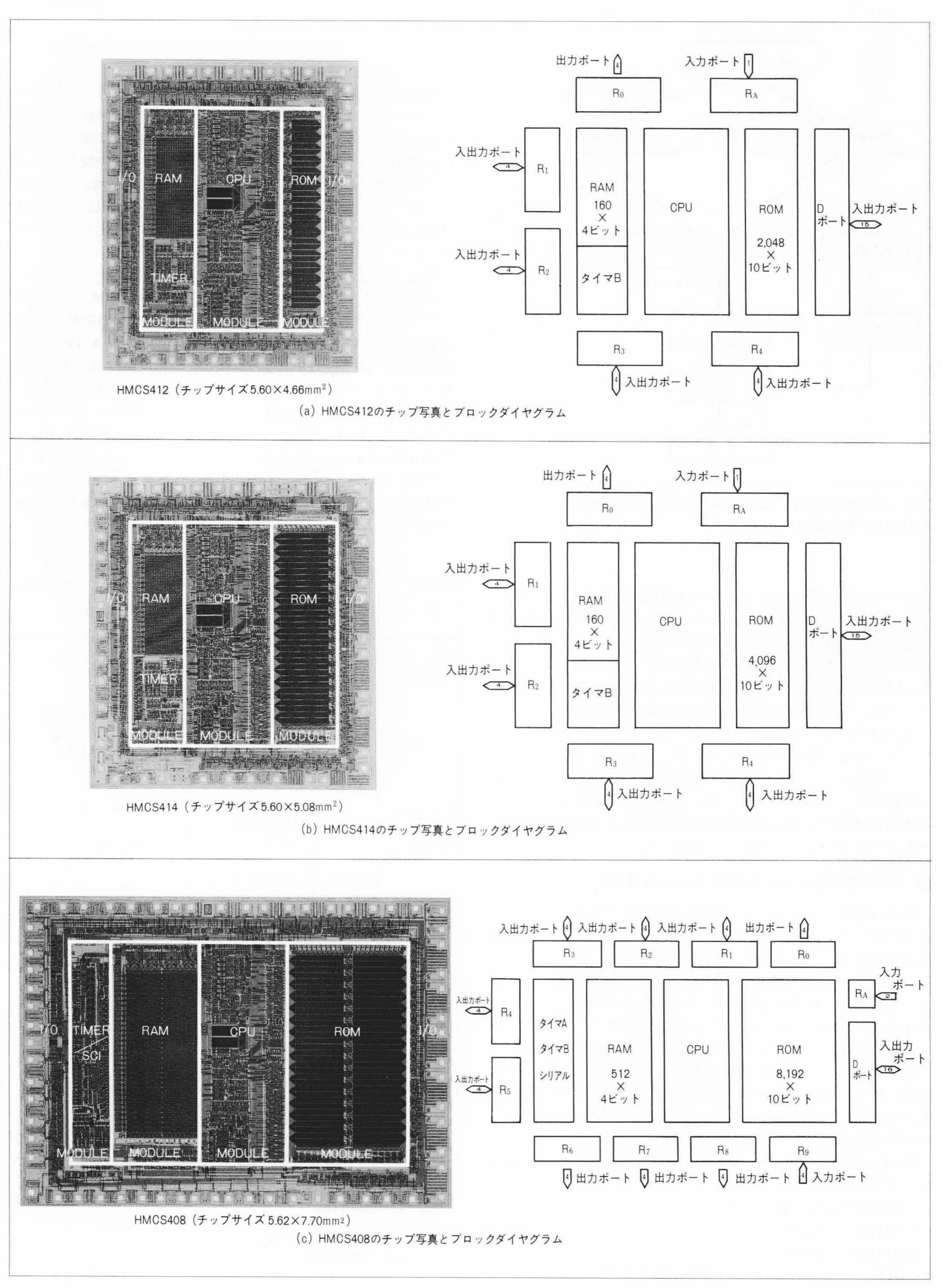

図 5 同一CPUによるHMCS400シリーズのモジュール展開 モジュール展開が具体的に理解できるように, チップ写真とブロックダイヤグラムを示す。

| 機種      | ROM<br>(×10ビット) | RAM<br>(×4ビット) | スピード<br>(μs) | 1/0 | タイマ | シリアル | パッケージ               | 評価用デバイス                                                                                                       |

|---------|-----------------|----------------|--------------|-----|-----|------|---------------------|---------------------------------------------------------------------------------------------------------------|

| HMCS402 | 2 k             | 160            | 1.33 · 2 · 4 | 58  | 2   | 1    | DILP-64S<br>FPP-64  | <ul> <li>EPROM搭載形         HD614P080S         HD614P0160S</li> <li>EPROM内蔵形(非高耐圧)         HD4074080</li> </ul> |

| HMCS404 | 4 k             | 256            | 1.33 · 2 · 4 | 58  | 2   | 1    |                     |                                                                                                               |

| HMCS408 | 8 k             | 512            | 1 · 2 · 4    | 58  | 2   | 1    |                     |                                                                                                               |

| HMCS412 | 2 k             | 160            | 1 · 2 · 4    | 36  | 1   | _    |                     | • EPROM搭載形<br>HD614P180                                                                                       |

| HMCS414 | 4 k             | 160            | 1 . 2 . 4    | 36  | 1   | _    | DILP-42<br>DILP-42S |                                                                                                               |

| HMCS424 | 4 k             | 256            | 1 . 2 . 4    | 36  | 2   | 1    |                     | • EPROM搭載形<br>HD40P4281<br>HD40P42161                                                                         |

| HMCS428 | 8 k             | 512            | 1 . 2 . 4    | 36  | 2   | 1    |                     |                                                                                                               |

表 2 汎用マイクロコンピュータ ラインアップ 汎用形マイクロコンピュータの製品概要を示す。

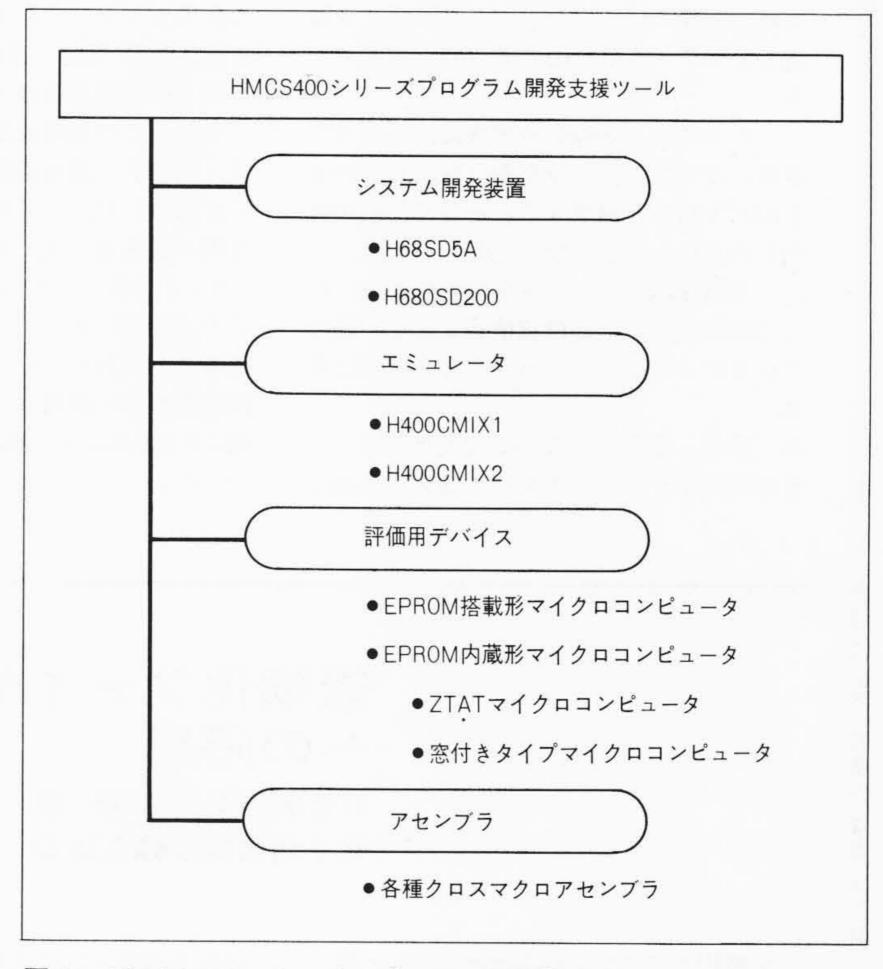

#### 5 開発支援ツール

マイクロコンピュータでは、プログラム開発支援ツール が完備していることがマイクロコンピュータ選定の一つの重 要なかぎとなっている。HMCS400シリーズでは、図6に示す ように使い勝手のよいプログラム開発支援ツールの充実を図 っている。応用システムのリアルタイム評価,確認に重点を 置き、システム開発装置、エミュレータだけでなく、実装評 価用にモジュール方式設計手法によるEPROM搭載形及び EPROM内蔵形マイクロコンピュータ (ZTAT (Zero Turn Around Time)マイクロコンピュータ」の開発にも力を入れ、 評価用デバイスとマスクROM内蔵品の同期化を推進してい る。

アセンブラはユーザープログラムの大容量化に対応するた めに、アブソリュート形式だけでなく、リロケータブルオブ ジェクト出力機能を追加し, 性能の向上を図っている。

#### (1) EPROM搭載形マイクロコンピユータ

EPROM搭載形マイクロコンピュータは, 市販の標準 EPROMが搭載できるところに特長がある。マイクロコンピュ ータのパッケージ上面のピンソケットに容易に搭載でき,実 際の応用機器にマイクロコンピュータを実装した状態でプロ グラム開発及びデバッグを行なうことができる。

#### (2) EPROM内蔵形マイクロコンピュータ

EPROMを内蔵した書換え可能な窓付きタイプ及びワンタ イムタイプのZTATマイクロコンピュータの品ぞろえを行な う。ZTATマイクロコンピュータはマスクROM品と同じプラ スチックパッケージに封入されている。ユーザーが汎用PROM ライタにより自由にプログラムを書き込むことができ, 応用 プログラムの作成からマイクロコンピュータの製造に必要な "TAT (Turn Around Time)"を"0 (Zero)"にすることが可能 となる。ZTATマイクロコンピュータにより、形状面の欠点 は解消され、価格的にも、プロトタイプの少量生産には最適 である。これにより、従来の量産品と同等の製品をプログラ ム開発時に入手することができ、機能・性能評価の面でも開 発期間の大幅な短縮が可能となる。

#### 6

以上、マイクロコンピュータを応用した分野は今後も技術 革新が続き, 応用機器のライフサイクルも短期化し開発競争

図 6 HMCS400シリーズのプログラム開発支援ツール 支援ツー ルの一覧を示す。

は激しくなっていく。その中で、シリコンチップ上にいかに 所望の機能を短期間で実現するかの新しい設計手法が求めら れている。この問題を解決する一つの設計法として, 論理設 計とレイアウト設計を1対1に対応させたモジュール方式設 計法を実現し、HMCS400シリーズの品種展開に適用した。モ ジュール方式設計は,今後専用化する特定用途向けの多品種 少量生産形の大規模LSIの設計を支える重要な技術の一つと して期待できる。

#### 参考文献

S. Hotta, et al.: New 4bit Single-Chip Microcomputer HMCS-404, HITACHI REVIEW, 33, No.2, 57~60 (1984)

### 完全両立性を有するEDTV信号方式

動特性の理論検討― 一その1

日立製作所 平野裕弘・吹抜敬彦・他 | 名 テレビジョン学会誌 39-10,885~890(昭和60-10)

近年、現行テレビジョンの高画質化、高 精細化への関心が高まり, 現行系との両立 性を考慮した様々な伝送方式の提案が行な われている。

完全両立性をもつEDTV (Extended Definition TV) 信号方式は、白黒テレビジ ョンからカラーテレビジョンへの移行時に 考慮されたような伝送路, 受像機の両者に 対する両立性をもち, 現行の伝送路のまま 高精細画像の送受信ができ,かつ既存受像 機でもアダプタなしに受信可能な方式であ る。

この方式は、映像信号帯域幅、色信号の 重畳, 音声などの信号形態は現行規格のま まEDTV信号を構成する。そして、解像度 向上のため, 下記の信号処理を行なう。

- (1) 帯域圧縮のため、輝度信号高域成分 YH (4.2MHz以上)を高精細情報として, 現行 テレビジョン信号のスペクトルの隙間に多 重。

- (2) 水平, 垂直, 時間の3次元周波数の信 号処理により、インタレース妨害、漏話な

ど現行テレビジョン方式固有の画質妨害を 低減。

一般に, 現行方式の画質妨害は, 「時間-垂 直」周波数領域での帯域制限の不完全さに よるところが多く、3次元フィルタで解決 できるとされているが, 反面, 動特性は制 約も受ける。このため、方式実現のための 動特性に関して理論的検討を行なった。

まず,水平・垂直方向に移動する動画像 の信号スペクトルを 3 次元周波数領域で解 析し、「時間-垂直」 周波数領域での帯域制限 に伴う動解像度特性を明らかにした。

また,この動解像度特性を基に,輝度信 号, 色信号, 高精細情報間の漏話発生につ いて検討した。この結果,輝度信号,色信 号間の漏話発生は、水平移動時で<u>1</u>秒間に 0.5~2 画素(1ライン910画素), 垂直移動 時で $\frac{1}{60}$ 秒間に $0.5 \sim 2$  ラインの動きに限ら れることが分かった。一方、輝度信号、高 精細情報間の漏話は、水平移動時には10秒 間に0.5画素以上の動きで発生することが分 かった。

方式実現の信号処理は,動きに応じてパ ラメータを変える動き適応処理が有効であ る。送信部の輝度信号,色信号,高精細情 報の多重では、0.5~2画素の水平移動時 に、輝度信号から漏話となる成分を3次元 フィルタで除去する。また、0.5画素以上の 動きでは, 高精細情報の多重を中止する。 一方, 受信部では, 0.5画素以下の動きは「時 間-垂直」, 0.5~2 画素の動きは「時間-垂 直」、「水平-垂直」、2画素以上の動きは「水 平-垂直」の周波数領域で、ほぼ理想的な分 離が可能なことを示した。

また、走査による折返しひずみを除くた め,送信部では走査線数525本,60フレーム, 順次走査の信号を時空間フィルタで帯域制 限した後, 走査線を間引き, インタレース 走査の信号を構成する。この場合にも, 折 返しひずみとなる成分が存在するときだけ, 時空間フィルタによりひずみ成分を除去す る適応処理の有効性を示した。

## 短縮化ファイヤ符号の復号法とVLSIプロセッサ への応用

日立製作所 岩崎一彦・船橋恒男・他 | 名 電子通信学会論文誌 D 68—D, 12, 1998~2006(昭60-12)

半導体テクノロジーの進歩に伴い, 様々 な機能を1チップに集積化することが現実 的なものとなってきた。その一つとして誤 り訂正符号がある。誤り訂正符号は, ディ スクシステムで、データの信頼性向上を目 的としてしばしば用いられる。

本論文では、VLSIチップに適した誤り訂 正符号(ファイヤ符号)の誤り訂正方式を提 案した。同時に、本方式を用いたVLSIチッ プを開発し、VLSIでの実用性を明らかにし

ファイヤ符号をディスク制御VLSIへ応用 するためには、幾つかのトレードオフを考 慮する必要がある。すなわち、(1)ハードウ ェア規模(チップ面積), (2)誤り訂正に要す る時間,(3)使用される頻度,(4)設計(論理, 回路, レイアウト)の容易さ, (5)将来の拡張 性などである。

実用に当たって、ファイヤ符号は短縮化 され、使用される。すなわち、意味のある タをチップ内のメモリに設定することによ

ビットパターンは後半部分にだけ存在し, 先頭部分はオールゼロとみなしてよい。誤 り訂正時間を高速化するために、このオー ルゼロの部分を省略する手法が、現在まで に幾つか提案されている。しかし、これら は多大なハードウェアを必要とするなど, VLSIに適した方法ではなかった。

本論文では,ファイヤ符号の生成多項式  $G(x) = (x^c+1) \times P(x)$  のうち, 多項式P(x)の性質に着目し、ハードウェアが少なく、 実用上の範囲内で誤り訂正時間も短いよう な誤り訂正方式を提案した。すなわち、除 多項式が*P*(x)であるフィードバックシフト レジスタの内容は、P(x)の周期 e だけシフ トすると元のパターンに戻る。これを利用 し、オールゼロの部分のうちeの整数倍のシ フトを省略し、誤り訂正の高速化を図るも のである。

この手法を用いると、ある種のパラメー

り、種々のレコード長に対応できる。この ため拡張性にも優れている。

また,本方式を一般の巡回符号の誤り訂 正手法へも拡張した。

提案した誤り訂正方式の応用対象として 32ビットファイヤ符号を選び、HDC(Hard Disk Controller) へ適用した。HD63463 HDCは、16ビットマイクロプロセッサの周 辺LSIとして開発されたもので、現在量産中 である。

HDCの総素子数は129Kトランジスタ,チ ップ面積は62.3mm<sup>2</sup>である。このうち誤り 訂正に必要なハードウェア及びマイクロプ ログラムは6,745トランジスタであり、HDC 全体の5.2%を占める。HDCの製造プロセス は2µmCMOSである。

半導体チップのいっそうの高集積化に伴 い、今後、VLSIに適した各種アルゴリズム の開発, 及び具体的応用が望まれる。