# 半導体プロセスから見た最近の超LSI製造システム

Recent Super LSI Manufacturing System Viewed from the Semiconductor Process

ハーフミクロン時代の技術課題は、微細化・高集積化に伴う立体構造化、多層配線化、素子特性の限界といった問題への対応である。基本となる微細加工技術では、露光技術は光の限界を追求する中で新たな芽が出てきた。一方、加工では高アスペクト化とダメージフリーの加工技術が最大の課題である。立体化・多層化・薄膜化に伴い膜形成技術が大きく変わろうとしている。タングステン膜配線のような新材料の開発と金属CVD(Chemical Vapor Deposition)技術の開発がその代表例である。同時に、これらを支えるクリーン化技術、計測・分析技術(装置)の向上が重要なポイントとなってきた。装置面では、大口径化

清水真二\* Shinji Shimizu

#### 1 はじめに

半導体の最大の特徴は、微細加工技術を基本とした高集積化技術である。これは、DRAM(Dynamic RAM)に象徴されるような高集積化によるビット単価の低減や実装密度の向上のような直接的効果だけでなく、現在の社会の流れとなっている小形化、低消費電力化イコールポータブル化、多機能化などの要求を実現する最大の武器となっている。

に対応し枚葉化・連続化が基本構造となってきた。

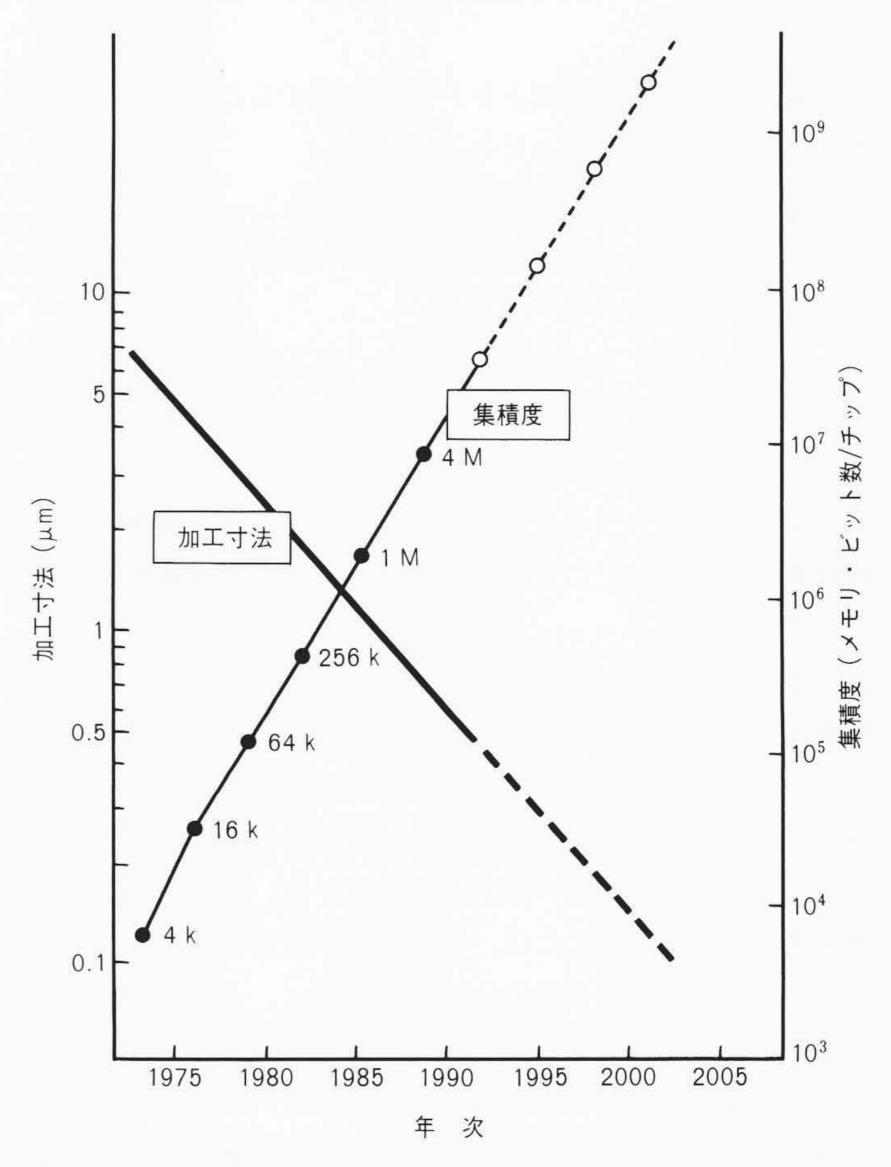

'90年代に入り、微細加工の世界は「ハーフミクロン」の時代になった。微細加工技術の推移とDRAMの集積度推移を図1に示す。ハーフミクロン時代になっても、3年で世代交代し4倍の高集積化を実現するトレンドは衰えていない。このトレンドは21世紀まで続くと想定され、それに向かった研究・開発が進められている。

半導体製造技術(プロセス技術)は、最も市場規模の大きいDRAMをテクノロジードライバとして先端技術開発が進められ、それを基本にさまざまな分野の半導体製品に展開されている。その基本は、リソグラフィー、ドライエッチなどの微細加工技術であるが、それだけでなく薄膜形成技術、酸化・ドーピング技術や計測・分析・評価技術などさまざまな技術の集積が必要である。そして、これらの新技術開発のために、同時に新しい装置が開発されてきた。

本稿ではハーフミクロン技術の技術動向と将来展望を探り、 その中から今後の半導体製造技術、製造装置に要求される事 柄について述べる。

図 I 加工寸法とDRAM (Dynamic RAM) 集積度の年次推移 3年で4倍の高集積トレンドも、3年で0.7倍の微細化トレンドも衰えていない。このトレンドは、21世紀まで続くと考えられる。

<sup>\*</sup> 日立製作所 デバイス開発センタ

## 2 ハーフミクロンプロセスの技術課題

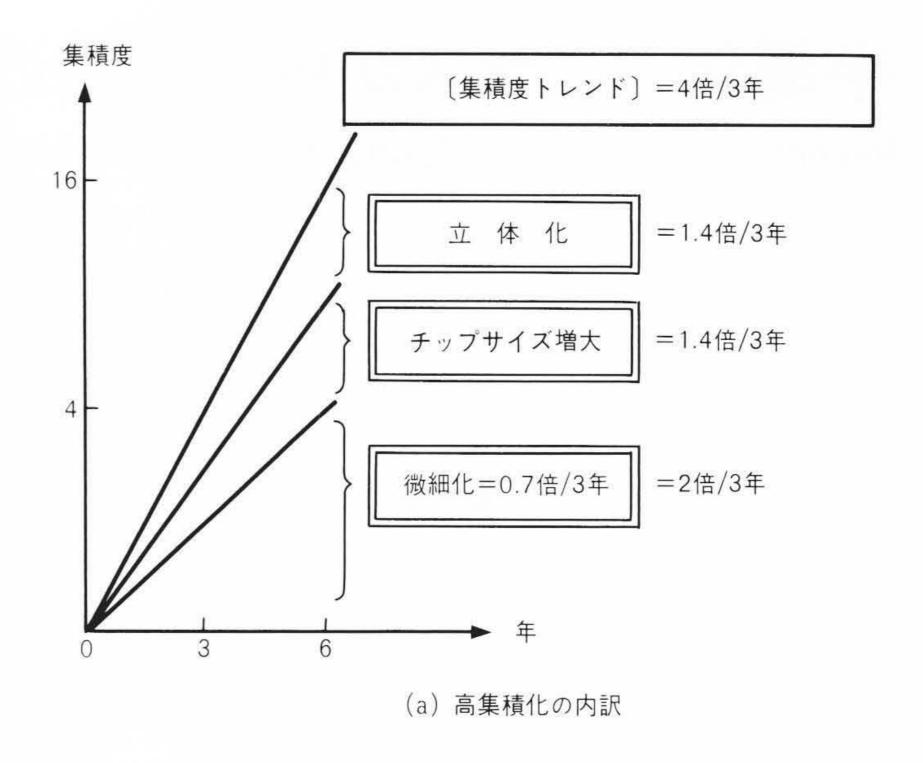

高集積化トレンドの内容をDRAMを例にとり、その内訳を示すと図2(a)のようになる。高集積化のニーズ(4倍/3年)に対して微細加工化(0.7倍/3年)だけでは追いつかず、チップサイズの増大と構造の立体化(高密度化)で対応している。

一方、高集積化の基本的な考え方は「スケーリング」」にあり、電界強度を一定にして平面構造・縦構造を縮小し、高密度化・高速化・低消費電力化を図ることである。しかし、実際のLSIでは、より高性能化を追求し、縦構造を一定にし(負荷容量を低減させるため)、電圧を一定にし(従来製品との互換性のため)、より高集積化する(多機能化)といったアプローチをとる。このため高アスペクトな構造・多層配線化・素子の限界に近づくといった問題が出てくる。これらの問題を、図2(b)にまとめて示す。

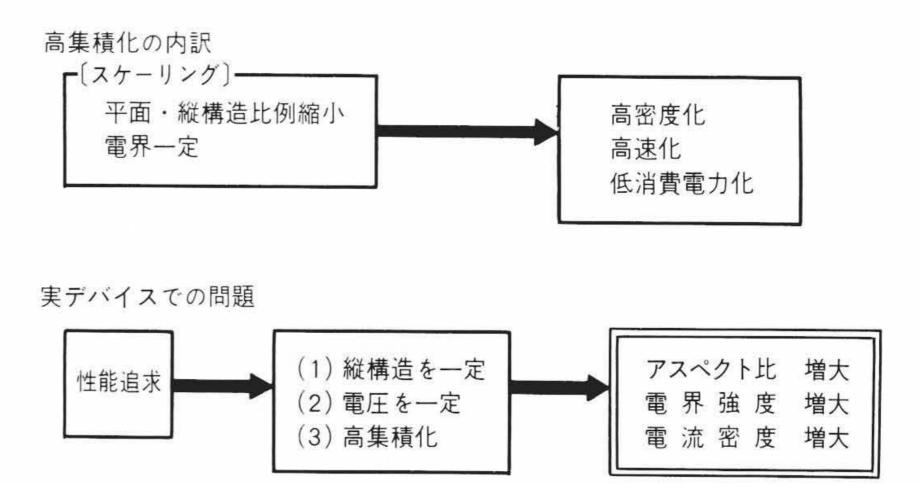

この結果, (1) 立体化構造, (2) 多層配線構造, (3) 素子特性が重要開発課題となってきている。立体化, 多層化の例を図3に示す。

ハーフミクロン時代の技術の特徴は以下のようにまとめる ことができる。

- (1) 従来どおりの微細化トレンドを実現することが必要であり、すべての前提となっている。

- (2) 立体構造・多層配線構造の比重が増大し、CVD(Chemical Vapor Deposition)・スパッタなどの膜形成技術が重要となり、また多用される。

- (3) 同時に、高アスペクトな構造でこれら微細加工・膜形成が必要である。このための新技術開発が不可欠である。

- (4) 一方,デバイス特性として,素子が限界に近づいてきており高品質なプロセスが必要である。このため,洗浄・前処理技術などウェーハにとっての環境クリーン化技術が重要になってきている。

- (5) そして、これらの技術をハーフミクロン時代に対応して開発するには、加工にせよ成膜にせよ、ウェーハ上で何が起きているかが正しく理解されていなければならない。その意味で、計測・解析技術が重要になってきている。

また、チップサイズの拡大という点から、ビット単価の低減を実現していくためには、大口径化が必要である。8インチ化への移行は、16 MDRAMの量産を控え、急速に動き出している。このため、大口径化への対応がプロセス面・装置面で重要な課題となっている<sup>2)</sup>。

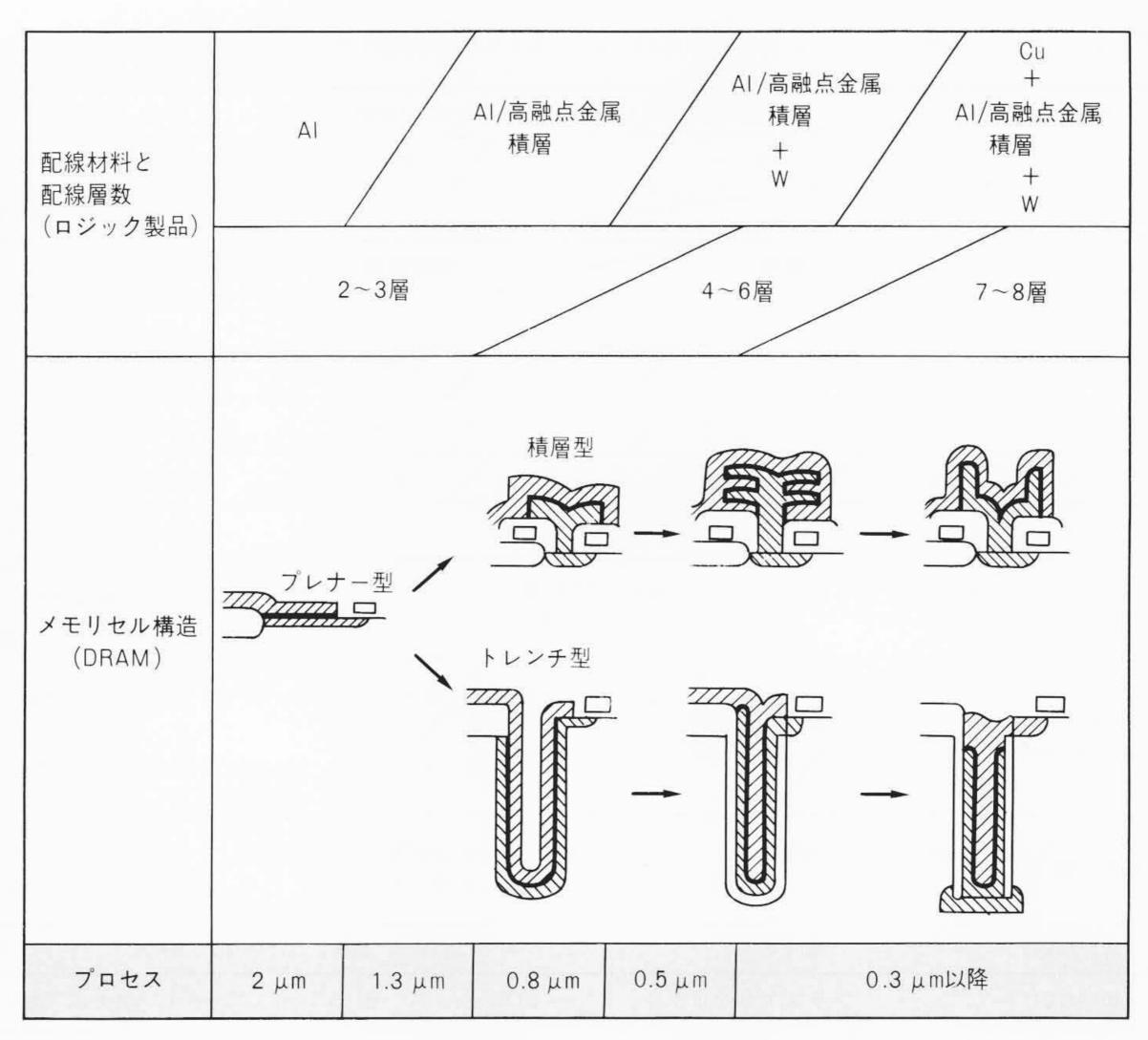

DRAMを中心としたプロセス技術の推移を**表1**にまとめて示す。

### 3 プロセス技術の開発動向

#### 3.1 リソグラフィー技術

2μmの256 kDRAMの時代から始まった縮小露光技術が、

(b) 高集積化のアプローチ

図2 高集積化トレンドとアプローチ DRAMでの例を示す。微細加工化だけでは要求を実現できず、チップサイズの増大と立体化を追加して実現している。高集積化のアプローチの基本は、「スケーリング」である。しかし、実際には「スケーリング」から外れたアプローチが必要になり、技術的な難しさを増大させている。

0.5 μm時代にも主流技術である。しかし、波長と同じオーダーの加工寸法レベルとなっており、これ以上の微細化は非常に困難であり、さらに、高集積化→高密度化→立体構造化に伴う高段差構造が、微細加工マージンを大幅に狭くしている。

したがって、レンズの高NA (Numerical Aperture) 化 (NA  $\sim$  0.5) と短波長化 (g線→i線) だけでは不十分であり、レジスト材料の性能向上が不可欠であり、現在精力的に進められている。

今後の量産マージンを考えると、さらに装置面、材料面で の性能向上を期待したい。その意味で、今後に期待される技 術を以下にまとめてみる。

#### (1) 電子ビーム露光技術

描画の自由度が高くこれを生かしてASIC(Application Specific IC)対応の露光技術として一部実用化されているが、スループットの制約から、現在はまだDRAMのような大量生産

図3 立体化と多層化の流れ 高集積化→高密度化→立体化・多層配線化の流れは、DRAMで はメモリセル構造の立体化で、ロジック製品では多層配線化で顕著に現れている。

には適用されていない。本質的に微細加工に適しており、ス ループットの問題を解決できれば、ディープサブミクロン以 降の主流技術となりうる。

## (2) エキシマレーザ露出技術

従来の縮小露光装置の延長として期待されているが、光源、 レジストなど改良が今後の課題である。0.3 μm時代の量産用 装置として期待したい。

## (3) 光技術の延命

EB(Electron Beam)装置もエキシマレーザも当面の量産ラ インには間に合わない。このため、従来の光技術でのくふう がいろいろなされている。

- (i) 高段差構造に対して、多層レジストプロセス

- (ii) 穴パターンに対して、FLEX(多重結像露光)法<sup>3)</sup>

- (iii) 解像度向上のために、CEL(Contrast Enhancement Lithography)法

しかし、これらの手法は一般にプロセスが複雑になるとい う欠点がある。

これに対して、最近、位相シフト法4という新しい技術が注 目されている。従来の光リソグラフィーがマスクを通過する 光の強度だけを情報として用いていたのに対して, 位相シフ ト法では、マスク上に補助パターンを追加し、ウェーハ上で 位相をずらし光の強度をゼロにできることを利用している。

大幅な解像度の向上が図られ、光技術の寿命を1世代以上延 命できる見込みである。

微細パターンの形成と同時に, その計測評価が同様に困難 な課題となっている。寸法測定に関しては、1μmレベルから 走査電子顕微鏡式の測長方式が定着したが5),すでに従来方式 の限界が見え始めている。

### 3.2 ドライエッチ技術

0.3~0.5 μm時代にドライエッチ技術に要求される課題は,

- (1) 微細化に伴う下地との選択比の向上, 寸法シフトの低減

- (2) 立体構造化に伴う高アスペクト比パターンの加工,マス ク材料との選択比の向上

- (3) ダメージ・汚染などの低減、高速エッチング である。

これらの両立しにくい要求を満足させるには、イオンの低 エネルギー化, 高密度化, 均一化, 指向性の強化などのプラ ズマの制御だけでなく, ウェーハ上での化学反応の制御が不 可欠である。

この点, サブミクロン時代から導入され出したマイクロ波 プラズマエッチは、イオンエネルギーを低くかつ制御でき、 イオン化率も高く,無電極放電という特徴でこの条件を満た し, 適応分野を拡大してきた。さらに, ウェーハ上での制御 という点から、低温化(温度制御)が重要な技術となっている。

DRAM集積度 64 k 256 k 16 k 1 M 4 M 16 M 64 M 256 M~1 G 2 µm  $5 \mu m$ 3 µm 加工レベル 1.3 µm 0.8 µm  $0.4 \sim 0.3 \, \mu m$  $0.25 \sim 0.1 \, \mu \text{m}$  $0.5 \sim 0.6 \, \mu \text{m}$ プロセス技術 nMOS CMOS BICMOS メモリセル構造 1トランジスタ・平面容量形 積層容量形 溝容量形 シングルドレーン トランジスタ構造 ダブルドレーン LDD 実効チャネル長 2 µm  $3 \mu m$ 1.3 µm 1.0 µm 0.8 µm  $0.6 \mu m$ 0.4 µm  $0.25 \sim 0.15 \, \mu \text{m}$  $0.5 \mu m$ 0.4 µm  $0.25 \, \mu m$ 接合深さ xj 0.8 µm 0.3 µm 0.15 μm 0.2 µm  $0.1 \sim 0.07 \, \mu \text{m}$ ゲートSiO2膜厚 Tox 50 nm 25 nm 75 nm 35 nm 20 nm 15 nm 10 nm  $7\sim5$  nm アイソレーション LOCOS 改良LOCOS 溝形アイソレーション 構造 エキシマ 密着·1/1投影露光 g線縮小投影露光 線縮小投影露光(高NA化 EB SOR リソグラフィー 単層レジスト 単層レジスト 位相シフト 反応性イオンエッチ\マイクロ波エッチ 低温マイクロ波エッチ 中世ビーム 枚葉形プラズマエッチ ウエットエッチ (異方性) ドライエッチング 円筒形プラズマエッチ (等方性) 高段差・トレンチ TMエッチ法 高選択性 側面反応制御 低ダメージ (側壁保護) ソフトランディング酸化 縦形酸化 低温プロセス(RTA) ボートローダ酸化 前処理一体化 不純物拡散 酸化・ドーピング 高エネルギー打ち込み 低エネルギー打ち込み 表面・界面制御 イオン打ち込み 一般 減圧CVD 常圧CVD ドープトPol Si SiO2 被覆性 ロードロック形CVD 枚葉処理・連続処理 層間 常圧CVD プラズマSiO2 SiN SOG BPSG エッチバック技術 O<sub>3</sub>-TEOS 薄膜形成 スパッタ Cu配線 メテルシリサイドCVD ブランケットメタルCVD EB蒸着 配線 バリアメタル バイアススパッタ 選択メタルCVD

表しプロセス技術のトレンド DRAMをテクノロジードライバーに、ほぼ3年を1世代として新技術開発を進めている。

注:略語説明 CVD (Chemical Vapor Deposition), SOG (Spin on Glass), NA (Numerical Aperture), nMOS (n-type MOS), PSG (Phospho-Silicate Glass), BPSG (Boro-Phospho-Silicate Glass), TEOS (Tetra Ethyl Ortho Silicate), CMOS (Complementary MOS), EB (Electron Beam), Bi-CMOS (Bipolar CMOS), RTA (Rapid Thermal Anneal), SEM (走査電子顕微鏡), TEM (透過電子顕微鏡), AFM (Atomic Force Microscope)

レーザ測長

これらの結果,制御が難しかったシリサイドを含むゲート電極の高精度加工やAl合金膜・積層膜加工での精度も向上してきた。

SEM

光学顕微鏡

今後の大きな課題は、高アスペクト比化の問題である。代表的な例は、酸化膜に開口させる持続穴パターンである。レジストのパターンで2~5のアスペクト比、エッチングされる酸化膜で2~3のアスペクト比が発生する。このような穴の中で、マイクロローディング効果を防いで均一性を出し、下地とレジストに対して十分な選択比をとり、サイドエッチを起こさずに、かつ低ダメージの高速エッチを行うことが要求されている。また、エッチング制御が非常に難しくなるだけでなく、検査も困難になっている。従来の走査電子顕微鏡式検査装置では、発生する二次電子が高アスペクトの穴の側面にトラップされ戻ってこなくなるためである。

今後、このような課題に対して十分なマージンを持つエッチング装置や検査装置の開発が望まれる。

## 3.3 薄膜形成技術

インライン外観検査SEM TEM

レーザ拡散異物検査 パターン検査 FIB加工・修正

測長SEM

素子の立体化・多層配線化に伴って、薄膜形成技術がきわめて重要な技術となってきた。その目的・用途から材料、形成法、プロセスに至るまで多岐にわたって新技術が展開しており、現在最も技術革新の激しい分野である。

高解像TEM AFM

溝底・溝深さ計測

TEM

DRAMの容量絶縁膜としては、5ないし10 nm程度のきわめて薄い絶縁膜が必要である。これを高信頼度の絶縁膜として形成するためには、形成時にできる自然酸化膜を除去する必要があり、前処理と成膜装置の一体化、酸化防止のロードロック形CVD装置、極薄膜制御のための枚葉処理化などの技術開発が進められている。同時に、従来シリコン窒化膜では電気特性的に限界であり、より誘電率の大きい材料(タンタル酸化膜などで)の開発も次世代技術として進められている。これら新装置開発と新材料開発は、今後のDRAM技術の重要なポイントとなっている。

多層配線という面では,多層化に対して平たん化をどうす

計測·解析

るかという点と、微細化に対して高信頼度な配線材料をどう するかの2点が重要課題である。

平たん化に関しては、素子の立体化に対応した平たん化と 多層配線化に対応した平たん化の技術が要求される。前者に 対しては、BPSG(Boro-Phospho-Silicate Glass) 膜のリフロ 一技術がサブミクロン時代から主流になってきたが、ますま すの立体化といっそうの低温化に対応するために、よりカバ レッジがよく平たん化されやすい形成法が追求されている。

多層配線の平たん化は、従来低温CVD絶縁膜とSOG(Spin on Glass)の組み合わせが用いられてきたが、(1)高アスペクト 構造の平たん化, (2) 信頼度向上のための低応力化・低温化の 観点から、プラズマCVD膜の改良 (O<sub>3</sub>-TEOS (Tetra Ethyl Ortho Silicate)など〕やSOG膜の改良が進められている。

一方、配線の微細化に伴って、エレクトロマイグレーショ ン,ストレスマイグレーション<sup>8)</sup>が非常に重要な問題となって きた。従来のAl合金膜では、この問題に対して十分なマージ ンが確保できず,マイグレーションに強い高融点金属膜の導 入が不可欠である。

微細配線としてはW(タングステン)膜が適しており、この 実用化のためCVD-W技術9が新しい装置とともに開発されて いる。CVD法による金属膜形成は、初めての本格的な技術で あり今後のCVD技術の展開として注目される。

より大電流を流す配線材料としては、W膜は抵抗値が大き く、このため、高融点材料とAlとの積層膜構造が採用されて いる。高融点金属材料としては、MoSi、TiW、TiN、Wなど が用いられている。これらの材料はスパッタ法による形成が 一般的であり、マルチチャンバ化による連続形成が重要にな ってきている。

多層配線の微細化・多層化に伴い、配線間の接続部での信 頼度問題が非常に大きな課題となってきている。高アスペク ト 穴形状となることからの金属配線膜のカバレッジ不足,平 たん化の目的で採用しているSOG膜が接続穴の側面に露出す ることによる金属配線膜の膜質劣化などが大きな問題となっ ている。これに対応するため、カバレッジのよい配線膜形成 法、接続穴への電極材料の積極的埋め込み技術、SOG膜をエ ッチバックする平たん化技術が開発されている。

なかでも、接続穴への選択的CVD法によるW電極の形成技 術が注目される。配線材料への全面CVD-W技術と穴部への選 択CVD-W技術がセットになって開発され、今後の金属材料の CVD法への発展が期待される。

一方, 従来技術のAl合金スパッタ法に関しても, 品質向上 のための高真空化とカバレッジ向上のための温度コントロー ル化が進められている。

## 3.4 酸化・熱処理・イオン打ち込み技術

ゲート酸化膜に関しても,いっそうの薄膜化と高信頼度化 が要求されており、初期欠陥、潜在欠陥をいかに低減するか が重要課題である。

サブミクロン時代から縦形酸化装置に変わり, 空気の巻き 込みが減少し、大口径化にも対応可能となってきたが、さら に性能を向上させるためには, 自然酸化膜の形成を防ぐ酸化 システムが必要となる。このためには, 前処理技術の向上と 空気(酸素と水分)巻き込みの防止, およびそれらの一体化が 今後の方向と思われる。

最近、前洗浄・前処理および結晶自体の酸化膜質への影響 が注目されている。例えば, 前洗浄を過度に行うと酸化膜質 が低下する。そのときSi表面が原子レベルで凹凸が激しくなっ ていることなどがわかってきた。これらは、高解像度TEM (Transmission Electron Microscopy)の一般化, STM (Scanning Tunneling Microscope) · AFM (Atomic Force Microscope) などの原子レベルでの観察装置の出現,極微量コ ンタミネーション計測の実用化など従来考えられなかった高 感度の計測・分析装置の実用化による成果100の一例である。こ れら装置によってSi表面の原子レベルでの観察が可能となり、 その詳細な観察から従来経験的に判断されていた事柄に対し 明確な判断ができるようになってきた。同時にこのことは, 今後のデバイスプロセスの開発には原子レベルでの解析が本 質的に重要になってきたことを示している。

イオン打ち込み装置の課題は、イオン打ち込み時に持ち込 まれる装置からの金属汚染と発生するチャージアップの問題 である。デバイスの微細化に伴い浅い接合化、薄い酸化膜化 が進み、これらが大きな問題となっている。

本格的なイオン打ち込み系のクリーン化とチャージアップ 対策が進行中であり、高真空化も進んでいる。

#### 今後の製造装置の動向と課題

ハーフミクロン時代に必要とされる製造装置面の課題は, 前章の中で個々に述べた。ここで今後の装置の動向と特徴を まとめると、表2のようになる。

基本的な動向として次のように考えられる。(1) 高精度制 御・高品質化、(2) 大口径化対応、(3) 自動化 イコール 一貫化 のニーズに対応して、クリーン化・枚葉処理化・連続処理化 が標準的な装置構成要素となり、これをベースとした基本フ レームの上に,新技術対応のプロセス装置が構成される。

まず、プロセスを原子レベルで制御する必要から、装置と してはウェーハ上での環境をクリーンにすることがまず基本 である。このために処理室だけでなく、配管・バルブなどの 部品,使用するガス・薬液など,ウェーハから見える環境を クリーンにすることが現在集中的に行われてきている11)。

次に、枚葉化が一段と進んできた。残る分野は酸化炉と低 圧CVD装置であるが、これらも薄い膜を形成する工程では枚 葉化の方向である。高精度化と高品質化は進んできており, 今後の課題は高スループット化と低価格化である。

表 2 ハーフミクロン装置の動向 16 MDRAMから量産で 8 インチウェーハを採用する予定のメーカーが急増している。この動きは、枚葉化や連続処理化の動きに拍車をかけている。

| 技術     | ポイント                          | 装 置                                                         |

|--------|-------------------------------|-------------------------------------------------------------|

| 熱処理    | 自然酸化膜防止<br>短時間アニール            | L/L酸化炉 →前処理付き<br>ランプ・アニール                                   |

| 前処理•洗浄 | 自然酸化膜除去                       | →前処理室付き                                                     |

| CVD    | 極薄膜化対応<br>自然酸化膜防止             | 枚葉低圧CVD →前処理付き                                              |

| 多層配線   | 埋め込み電極対応<br>W配線対応<br>積層AIスパッタ | 選択CVD-W(前処理付き枚葉装置)<br>全面CVD-W(前処理付き枚葉装置)<br>前処理付き連続CVD-スパッタ |

| エッチ    | 高選択比, 低ダメージ<br>積層膜エッチ         | 低温枚葉エッチ<br>連続エッチ・防食一貫処理                                     |

注:略語説明 L/L(Load Look)

以上二つをベースに、より高度なプロセスの実現と自動化・一貫化を目指し、連続処理化が次の課題となっている。 ウェーハをクリーンのまま処理するには連続処理が理想であり、これによって従来どうしても発生した工程間での汚染の侵入、界面での酸化膜などの形成等の問題が防げる。そして、理想としての一貫自動化ラインへつながっていく。

この流れは、基本となる装置の構成がほぼ標準化できることを意味する。従来の装置の問題点は、工程・プロセスごとに、装置メーカーごとにまったく装置が異なり、ユーザーも選択・習得・保守などに困るし、メーカーもハードからソフトまですべての面の開発・製造・サポートが必要で非常に負担が大きかった。基本的なハード面、ソフト面の標準化が図られると、ユーザー、メーカーとも非常に負担が軽減される。この方向に標準化が進んでいくことが望まれる。

## 5 おわりに

ハーフミクロン製造技術として、その課題と最近のプロセス技術の動向について概説し、将来への展望と装置開発の課題をまとめた。

基本的な背景は、立体構造化、多層配線化、素子特性の限界である。この流れの中で、基本となる微細加工技術は限界に近づいてきた。露光技術としては、短波長化・高NA化だけ

では対処できず、レジスト材料の向上で対応し、次世代技術としては、位相シフト技術が注目される。加工面では、高アスペクトパターンをどう加工するか、どう検査するかが問題であり、今後の課題である。立体化・多層化に伴い膜形成技術は、新材料・新プロセスの技術開発が最も急な分野となってきており、CVD-Wによる配線・電極技術がその代表例である。装置開発を伴って現在大きく変化している。同時にこれらを支えるクリーン化、計測・分析技術が非常に重要になってきており、原子レベルの分析に見られるような計測技術に支えられた技術開発が、今後の技術開発の方向を示している。

半導体製造技術の問題はますます難しくなっており、製造装置・計測装置だけでなくさまざまな分野の新技術を必要としている。それらが有機的に同期をとって開発が進められ、 量産化技術として確立できる総合的力が重要になってきている。

## 参考文献

- 1) R. H. Dennard, et al.: Design of Ion-implanted MOS-FET with Very Small Physical Dimensions, IEEE J. Solid-State Circuits, Vol.SC-9, p.256(1984)

- 2) 日経マイクロデバイス:セミコン・ジャパン90, No.65, 92~ 124(1990)

- 3) H. Fukuda, et al.: A New Method for Enhancing Focus Latitude in Optical Lithography, FLEX: IEEE EDL EDL-8, 179~180 (1987)

- 4) 長谷川,外:位相シフト法(1),(2),第49回応用物理学会学術 講演会予稿集,497(1988)

- 5) 大高,外:電子ビームを用いた半導体プロセス評価装置,日立 評論,71,5,401~407(平1-5)

- 6) S. Tachi, et al.: Low Temperature Microwave Plasma Etching, Ext. Abst. 19th Conf. on Solid State Devices and Mat. 553~556 (1988)

- 7) H. Shinriki, et al.: 1988 Symp. on VLSI Thech., 29(1988)

- 8) 岡林:LSI Al配線のストレスマイグレーション,応用物理, 59,11,35~47(1990)

- 9) N. Kobayashi, et al.: 第22回固体素子・材料コンファレンス, C~3(1990)

- 10) 第38回応用物理学関係連合講演会予稿集: (1991)

- 11) 大見,外:超クリーン化技術,日経マイクロデバイス別冊 No.2(1988)