# ノマディック時代のSH、SH-DSPマイクロプロセッサ

SH and SH-DSP Microprocessors for the Nomadic Age

Tôru Baji

川崎郁也\*

Ikuya Kawasaki

Norishige Kawashimo

野口孝樹\*

Kôki Noguchi

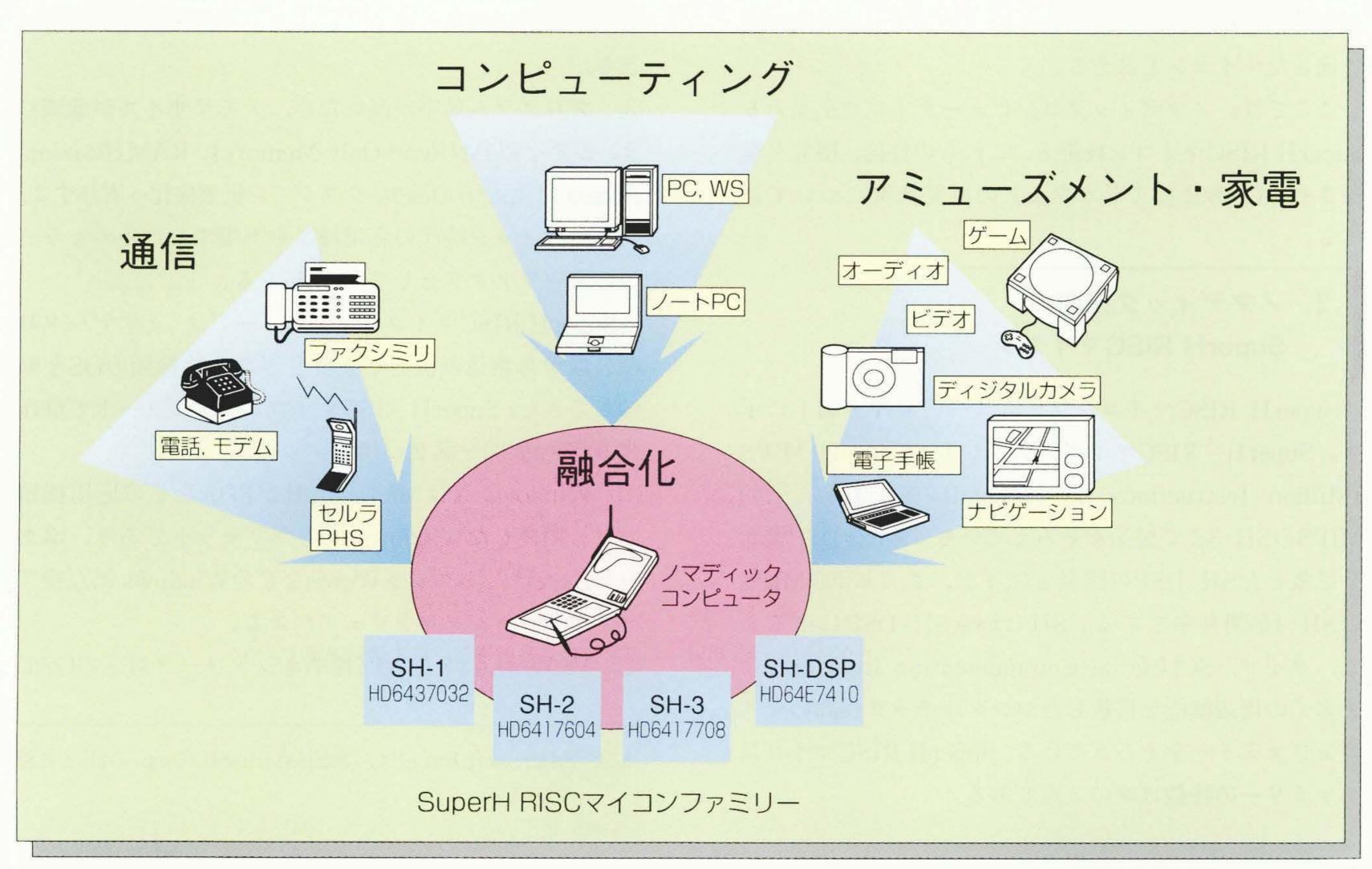

注:略語説明 PHS (Personal Handyphone System), PC (Personal Computer), WS (Workstation), RISC (Reduced Instruction Set Computer)

#### ノマディックコンピューティングを支えるSH(SuperH RISC)マイコン

情報機器の高機能化、小型化に伴って、通信、コンピューティング、アミューズメント・家電分野の融合が見られ、この融合を実現する応用 機器に求められるのが高性能,低消費電力,低価格のマイコンである。SuperH RISCマイコンファミリーは,このニーズにこたえるものであり, PDA (Personal Digital Assistant), ゲーム, カーナビゲーション, セルラ電話などに広く使われている。

ハードウェアとソフトウェアの進歩により、情報機器 の高機能化,小型化が近年加速されている。その一つの 大きな流れとして、通信、コンピューティングおよびア ミューズメント・家電分野の融合,すなわちCCC(Communication—Computing—Consumer)の融合が見える。

半導体およびこれを支えるミドルウェアの進歩によ り、これらの機能の携帯機へのインテグレーションが進 んでいる。これらを統合するOS(Operating System)が 加わって, 真のノマディックコンピューティング環境が 完成する。

半導体の核となるデバイスはマイコンである。上記機

能を実現するためには単なる性能だけではなく、低消費 電力,低コストなどが大きな要素となってくる。

SuperH RISCマイコンはこれらの用件を満たすため に開発したものである。SH-1,-2の小型・高性能RISCコ アを出発点に、SH-3では高度なOSサポートを実現する MMU (Memory Management Unit), SH-DSPでは汎用 DSP(Digital Signal Processor) クラスの高速信号処理 能力を得た。また、これらを実現したアーキテクチャ技 術とともに、その性能を発揮させるためのOS、ミドルウ エアを開発した。

<sup>\*</sup>日立製作所 半導体事業部

#### 1. はじめに

日立製作所の32ビットRISCマイコン「SuperH RISCマイコン」はCCC融合の応用機器からのニーズを先取りしたマイコンで、PDA、ゲーム、カーナビゲーション、セルラ電話などに広く使われており、ノマディック時代に適したマイコンと言える。

ここでは、ノマディックコンピューティングを支える SuperH RISCマイコン技術と、これらの性能、機能を発 揮させるOSおよびミドルウェアの開発状況について述 べる。

# 2. ノマディック指向の SuperH RISCマイコン

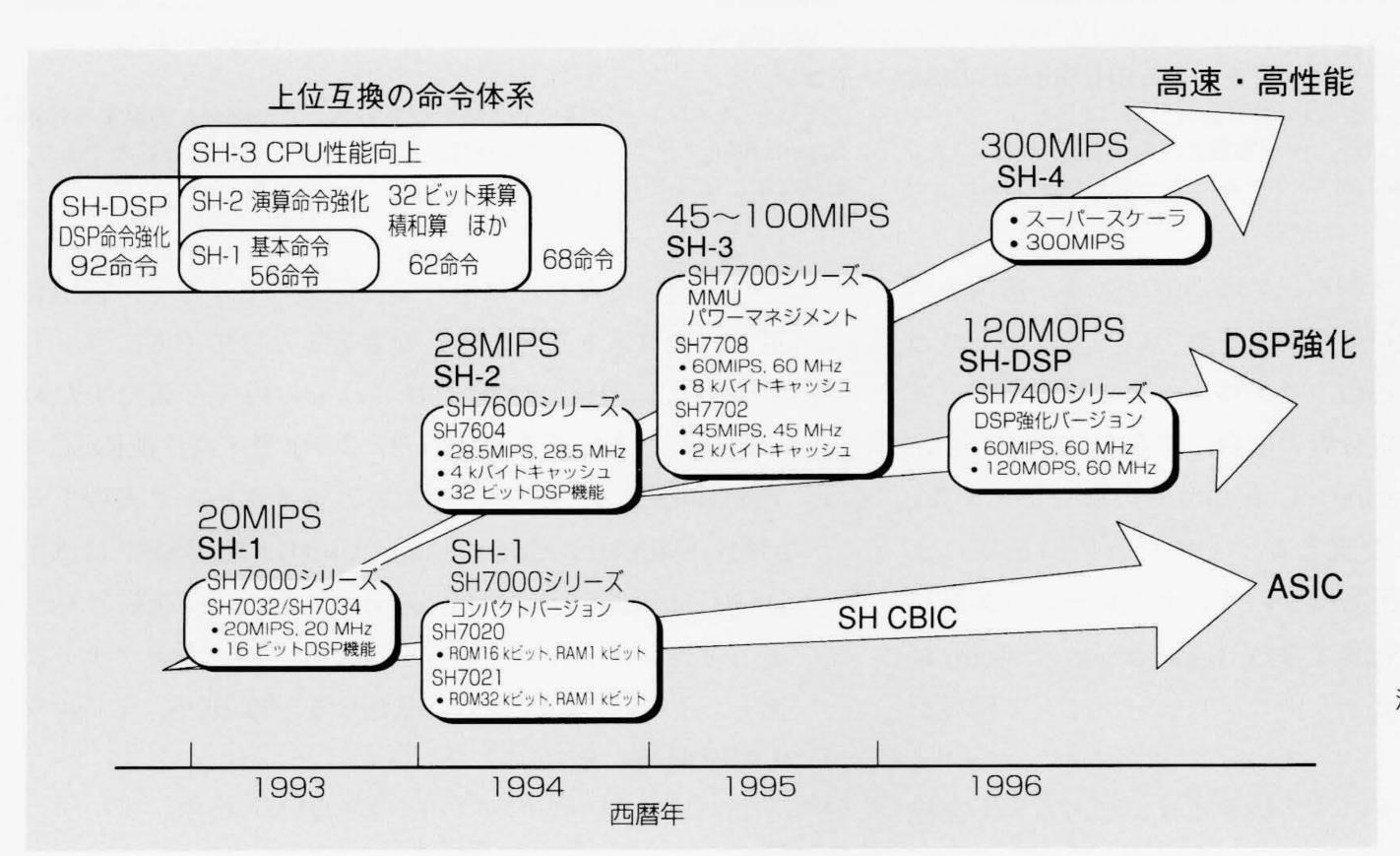

SuperH RISCマイコンファミリーの展開を図1に示す。SuperH RISCマイコンファミリーでは、20 MIPS (Million Instructions per Second)のSH-1から、100 MIPSのSH-3まで製品をそろえている。また、DSP機能を拡張したSH-DSPの開発も完了し、さらに300 MIPSのSH-4を開発中である。SH-1からSH-DSPに至るまで、タイマ、SCI(Serial Communication Interface)など多くの周辺機能を搭載したシングルチップ指向のマイコンファミリーをそろえている。SuperH RISCマイコンファミリーの特徴は次の3点である。

- (1) MIPS/W(SH-3で150 MIPS/W)が高いため、高速・高性能を実現しながら低消費電力化も実現できる。 また、バッテリ動作時の動作時間が長くなる。

- (2) CPU (Central Processing Unit) コアサイズが小さいため、周辺機能を多く内蔵でき、高集積化が容易であり、外付け部品の減少、システムの低価格化が実現できる。

- (3) プログラム効率が高いため、メモリサイズが低減でき、必要なROM (Read-Only Memory)、RAM (Random Access Memory)の減少、システムの低価格化へ寄与する。 ノマディック時代の応用機器を実現するためのもう一つのキーファクタとして、OSがある。

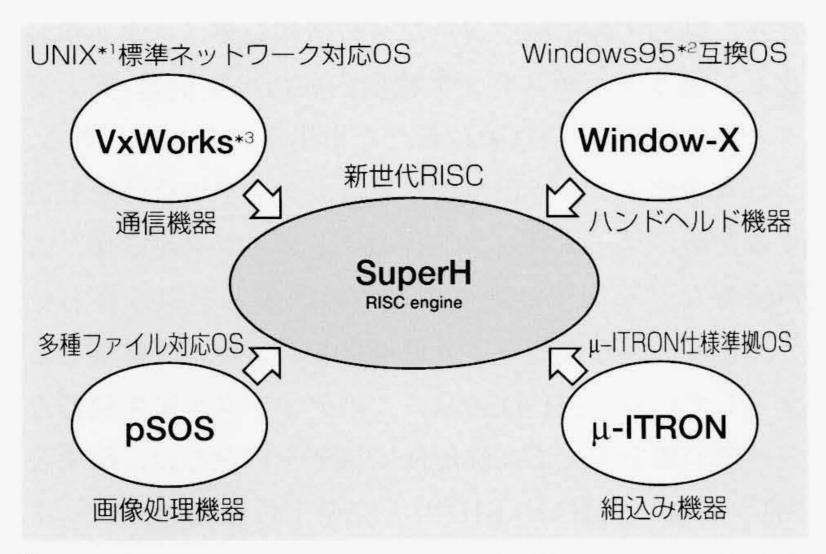

SuperH RISCマイコンファミリーでは、まずデータ処理装置から組込み機器で必要とされる数種類のOSを整. 備してきた。SuperH RISCマイコンファミリー上で動作するOSの展開を図2に示す。

- (1) Windows-XはMicrosoft社がPDAなどの応用機器向けに開発したWindows 95のサブセットであり、ポケットExcel\*1)、ポケットWordsなどのWindows 95互換アプリケーションソフトウェアがある。

- (2) VxWorksは、UNIX標準ネットワーク対応のOSで

<sup>※1)</sup> Microsoft Excelは、米国Microsoft Corp.の商品名称 である。

注:略語説明 MOPS (Mega Operation Per Second) CBIC (Cell Based IC) ASIC (Application Specific IC)

図1 SHマイコンファミリー展開

SH-IからSH-DSPに至るまで、タイマ、SCIなど多くの周辺機能を搭載したシングルチップ指向のマイコンファミリーをそろえている。

#### 注:

- \*1 UNIXは、X/Open company Limitedがライセンスしている 米国ならびに他の国における登録商標である。

- \*2 Windowsは、米国およびその他の国における米国Microsoft Corp.の登録商標である。

- \*3 VxWorksは、米国Wind River Systems, Inc.の商品名称 である。

#### 図 2 SuperH RISCマイコン用OS

SuperH RISCマイコンファミリーは多種のOSを整備しており、ノ マディック指向のマイコンと言える。

あり、インターネット端末で多く使われているJava\*2)と 組合せが可能であり、通信機器で使われている。

- (3) pSOSは、多種のファイルシステムをサポートでき るOSであり、画像処理を必要とするマルチメディア機器 で使われている。

- (4) μ-ITRONは、OSのカーネルサイズが小さいことか ら、PDA以外にもセルラ電話、CD-ROM (Compact Disc ROM) などの通信分野,民生機器に幅広く使われている。 以上のように、SuperH RISCマイコンファミリーは、 多種のOSを整備しており、ノマディック指向のマイコン と言える。

## 3. SH-3の開発およびノマディック 携帯機器への応用

携帯情報機器をターゲットにSH-3を開発した。携帯 情報機器には現在のパソコンに匹敵する処理能力と電池 駆動による長時間動作が要求される。このため、SH-3で はSHシリーズの特徴であるコード効率の良いRISCアー キテクチャ採用に加え、メモリ管理機構(MMU)の内蔵、 パワーマネジメント機構を採用した。

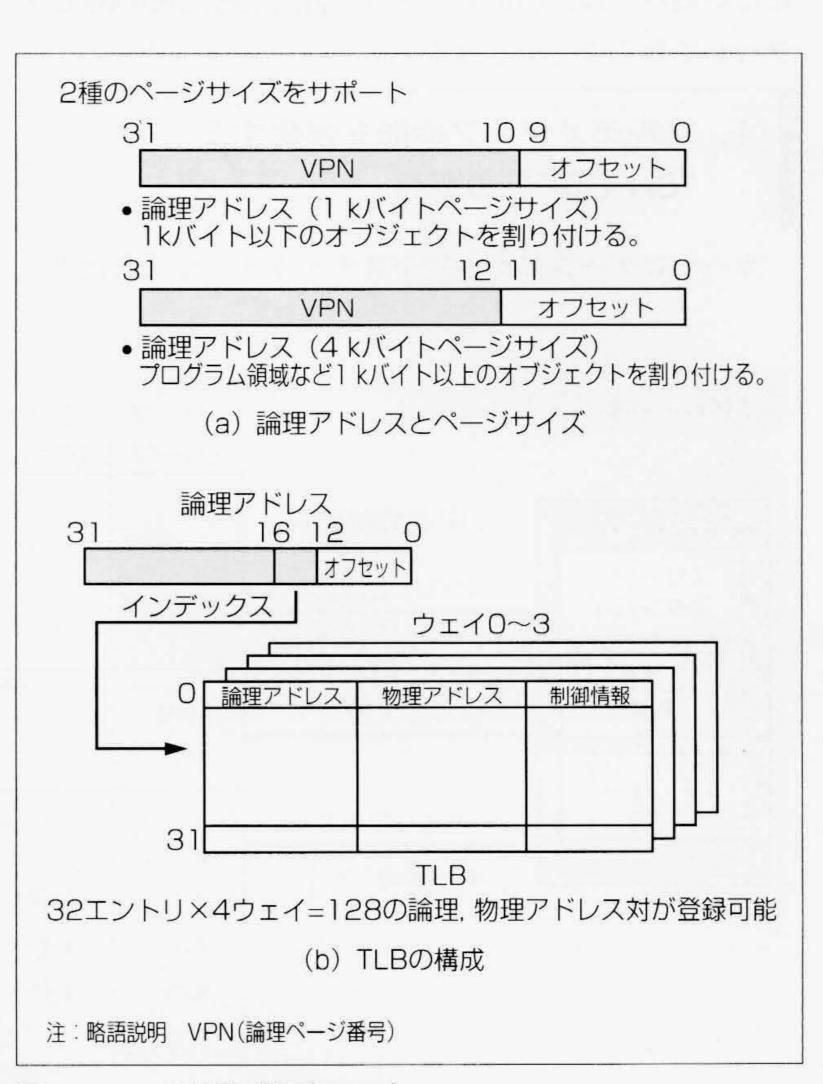

#### 3.1 MMUの内蔵

SH-3にMMUを内蔵することにより、メモリの効率的

Javaは、米国およびその他の国における米国Sun Microsystems, Inc.の商標である。

活用、メモリの保護を可能としている。サポートにあた っては、コスト(面積)と消費電力を可能なかぎり抑え、 かつ汎用OSの移植可能な機能・性能を実現するように 努めた。アドレス変換方式はページングを採用している。 論理アドレスとページサイズを図3(a)に示す。ページ サイズは標準サイズである 4kバイトに加えて1kバイ トをサポートする。

### 3.2 ソフトウェア管理TLB

TLB(Translation Lookaside Buffer)の構成を図3 (b)に示す。論理アドレスから物理アドレスへの変換は, TLBに登録されている論理アドレスを検索し,対応する 物理アドレスを読み出すことによって行われる。SH-3 の場合、128組のアドレスがTLBに登録できる。TLBに 論理アドレスが登録されていない場合,主記憶上に置か れているOSが準備したアドレス変換テーブルを使っ て変換を行う。この場合の変換はハードウェアでサポー トせず、ソフトウェアで処理する方式をとった。アドレ ス変換テーブルの構成の自由度をユーザーに残すためで ある。

#### 図3 メモリ管理機構(MMU)

TLBに登録されている論理アドレスを検索し,対応する物理アド レスを読み出してアドレス変換を行う。

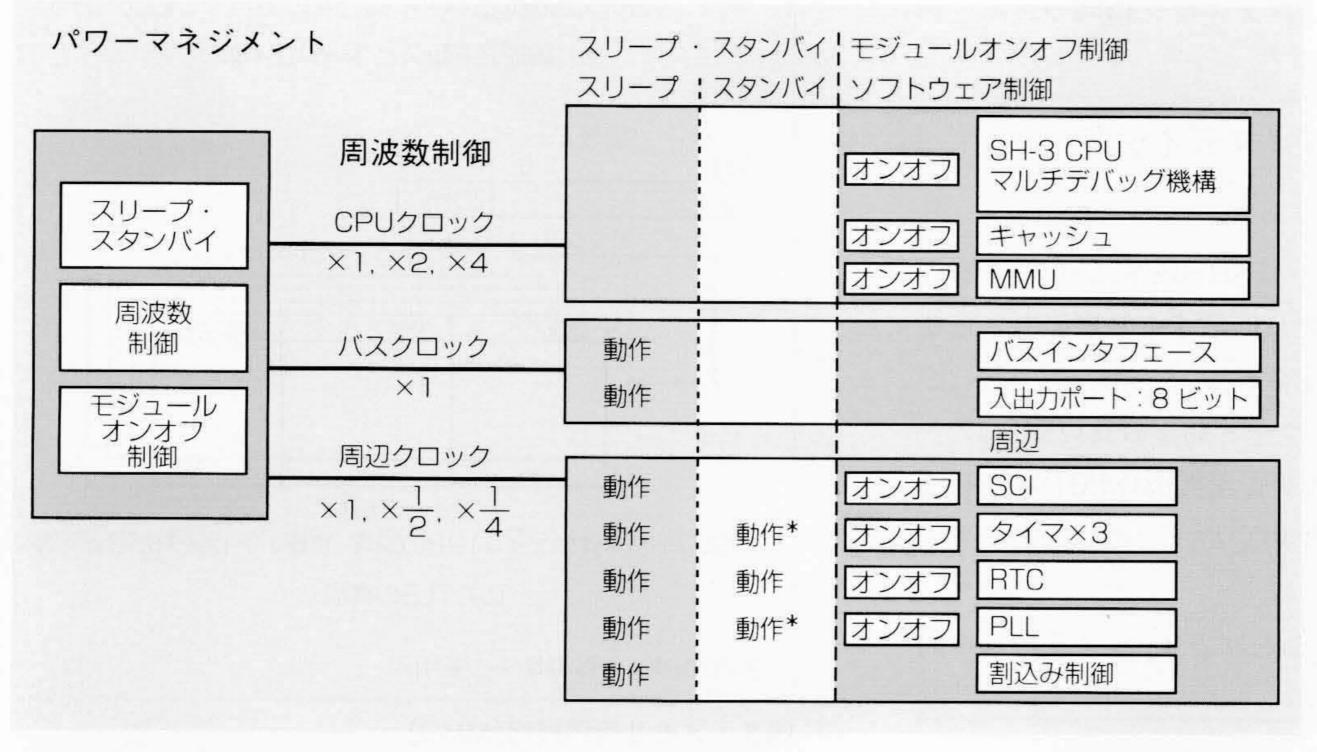

#### 3.3 パワーマネジメント機構

携帯情報機器では電池駆動の動作時間が重要である。 そのために求められるのは、手書き文字認識、音声認識 などの高性能が要求される処理、および通常時、画面表 示だけのアイドル時などその時々に必要な処理に対する 能力に応じて必要な電力しか消費しないプロセッサの実 現である。SH-3ではパワーマネジメント機構でこれを 実現している。この概要を図4に示す。

バスクロックの周波数は、バス駆動で消費される電力や接続するメモリ、システム設計のコストなどから選択される。コスト対電力の観点から、目標性能の達成できる範囲内で低周波数に設定するのが有利である。例えば、手書き文字認識に40 MIPSの性能、通常時は10 MIPSの性能が必要と仮定すると、バスクロックの周波数を10 MHzに設定すればよい。高性能が要求される処理ではCPUのクロック周波数を40 MHz、通常処理ではCPUのクロック周波数を40 MHz、通常処理ではCPUのクロック周波数を10 MHz、アイドル時にはスリープまたはスタンバイモードと動的に切り換えることにより、余分な電力を消費せずに処理に合わせた必要な性能を出すことができる。また、各周辺、MMU、キャッシュも使わない処理では、制御レジスタへの書込みでそれらをオフにしておくことができる。

# 4. マルチメディア機能を強化する "SH-DSP"の開発

カーナビゲーションや電子スチルカメラなどに代表さ

れる,動画・静止画や音声などの情報をディジタル信号化して扱うマルチメディア機能内蔵の民生機器(ディジタル民生機器)が,急激に新たな市場を形成しつつある。これらのディジタル民生機器では、システム全体を制御するためのマイクロコントローラとディジタル画像、音声情報などを加工処理するためのDSPとを組み合わせて、より高度な機能をより低価格なシステムで実現しようとしている。SH-DSPは、このディジタル民生機器などへの適用を考えて高性能DSP機能を内蔵した、従来のSHマイコン(SH-1、SH-2)と完全上位互換の32ビットシングルチップRISCである。

SH-DSPの命令セットを図**5**に示す。SH-2の命令セットに対して完全上位互換で、リピート命令(3命令)、16ビットDSP命令(3命令)、および32ビットDSP命令(4×21命令)を追加した。SH-3で強化された命令も、命令コードとして取り込める。

追加命令であるリピート命令は、ディジタル信号処理 などで多用される繰返し処理の最終部分にあるプログラ ムジャンプを、ハードウェア処理によって実行時間0で 高速に実行する。

16ビットDSP命令では、新たに拡張したDSP演算用レジスタと内蔵メモリとの間で、それぞれ独自にアドレシングした二つの16ビットデータを1クロックサイクルで同時に転送処理することもできる。32ビットDSP命令では、このデータ転送処理に加え、これと同時に実行可能な積和演算などのDSP処理を指定する。

#### 注:略語説明ほか

RTC (Real-Time Clock)

PLL (Phase-Locked Loop)

- (1) 「動作」は、スリープ・スタンバイ中に動作するもの。

- (2) 「オンオフ」は、制御レジスタの 設定によって停止することので きるモジュール

- (3) CPUクロック, バスクロック, 周辺クロックの3種類のクロックがあり, 制御レジスタの設定によって動的に周波数を変更することができる。

- \* RTCクロック使用時だけ動作

#### 図4 パワーマネジメント機構

必要な処理能力に応じて必要な電力しか消費しないプロセッサの実現が望まれ、SH-3ではパワーマネジメント機構でこれを実現している。

注:

\*1 演算命令は32 ビット命令で、並列にX/Yメモリにアクセス可能 算術演算(PADD PMULS, PSUB PMULS, PADD, PSUB, PMULS, PABS, PCMPなど)

論理演算 (PAND, POR, PXORなど) シフト命令 (PSHA, PSHL)

MACH/MACLとDSPレジス夕間の転送命令(PSTS, PLDS)

\*2 データ転送命令は16 ビット命令

X/Yメモリとのデータ転送命令 (MOVX.W, MOVY.W) 任意メモリとのデータ転送命令 (MOVS.W, MOVS.L)

#### 図 5 SH-DSPの命令セット

SH-2の命令セットに対して完全上位互換であり、SH-3で強化さ れた命令も命令コードとして取り込むことができる。

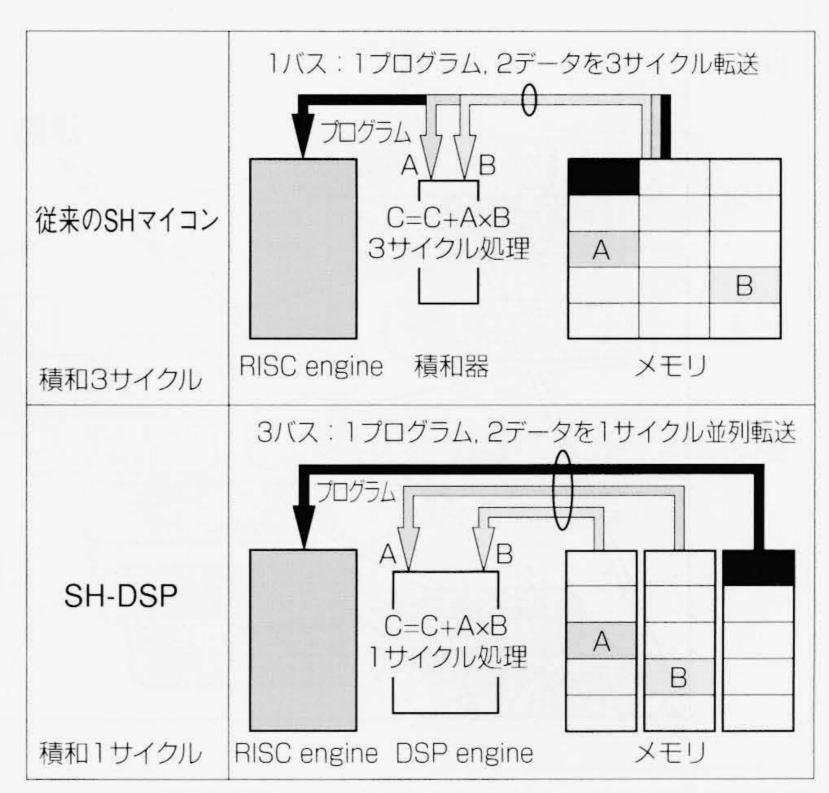

SH-DSPの内部バス構成を、従来のSHマイコンとの 比較で図6に示す。SH-DSPで新たに設けられたXおよ びYバスは、新規DSP命令の実行で二つの16ビットデー タ転送に用いられる。従来の内部バスで命令フェッチが 行えるので、二つの16ビットデータ転送と積和演算など のDSP処理を、同時に1クロックサイクルで連続実行す ることが可能になる。

SH-DSPのCPU性能は、動作周波数60 MHzなので、 SH-2の約2倍, 60 MHz動作のSH-3とほぼ同程度の60

図 6 SH-DSPの内部バス構成

SH-DSPで新たに設けられたXおよびYバスは,新規DSP命令の実 行で二つの16ビットデータ転送に用いられる。

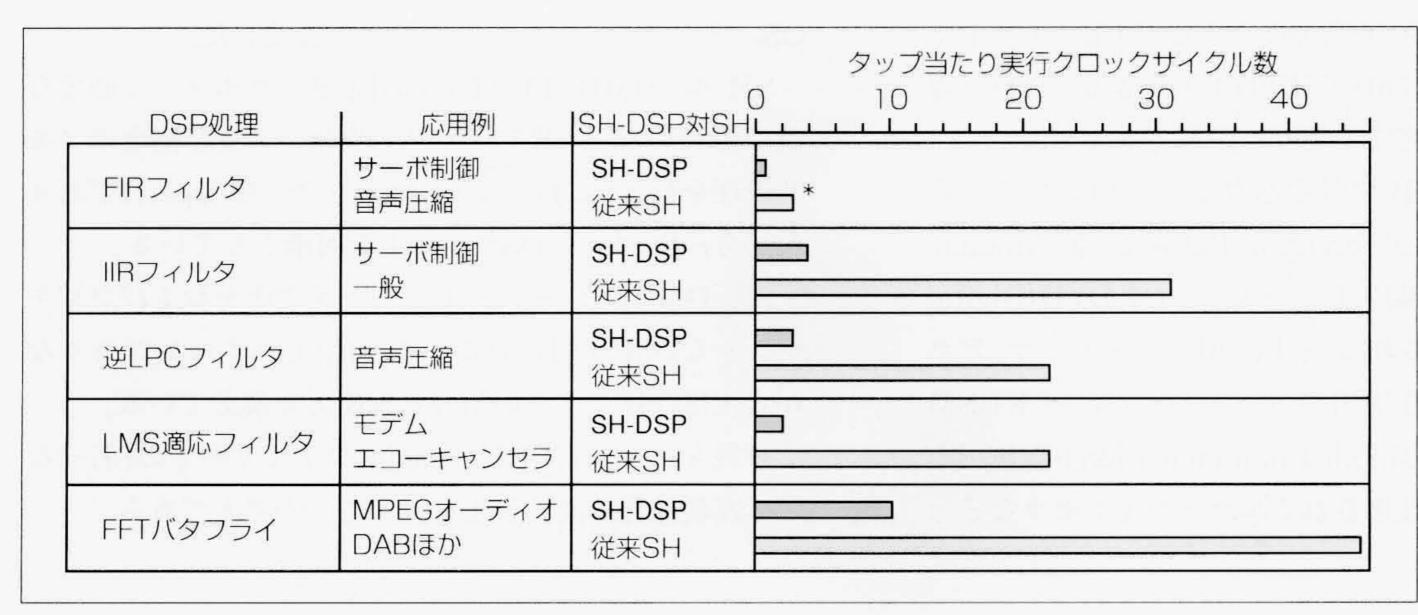

MIPSである。一般的なDSP処理に必要な実行クロック サイクル数を従来SHとの比較で図7に示す。新規に追 加されたリピート命令およびDSP命令の効果で,一般的 なフィルタ処理などは、従来SHの実行クロック数の も 以下で実行が可能になる。そのため、従来SHと比較して、 より低い動作周波数で要求DSP処理性能が実現できるの で、装置の低消費電力化にも大きく寄与できると考える。

# 5. ノマディックコンピューティングを 支えるミドルウェア

ノマディックコンピューティングは操作の根幹となる

注:略語説明ほか FIR (Finite Input Response) IIR (Infinite Input Response) LPC (Linear Predictive Coding) LMS (Least Mean Square) FFT (Fast Fourier Transform) DAB (Digital Audio Broadcasting) \*SHベンチマーク値は リピートおよびモジュ ロアドレッシングを実

行していない。

#### 図7 一般的なDSP処理の実行クロックサイクル数

新規に追加されたリピート命令およびDSP命令の効果で,一般的なフィルタ処理などは,従来SHの実行クロック数の一以下で実行が可能になる。

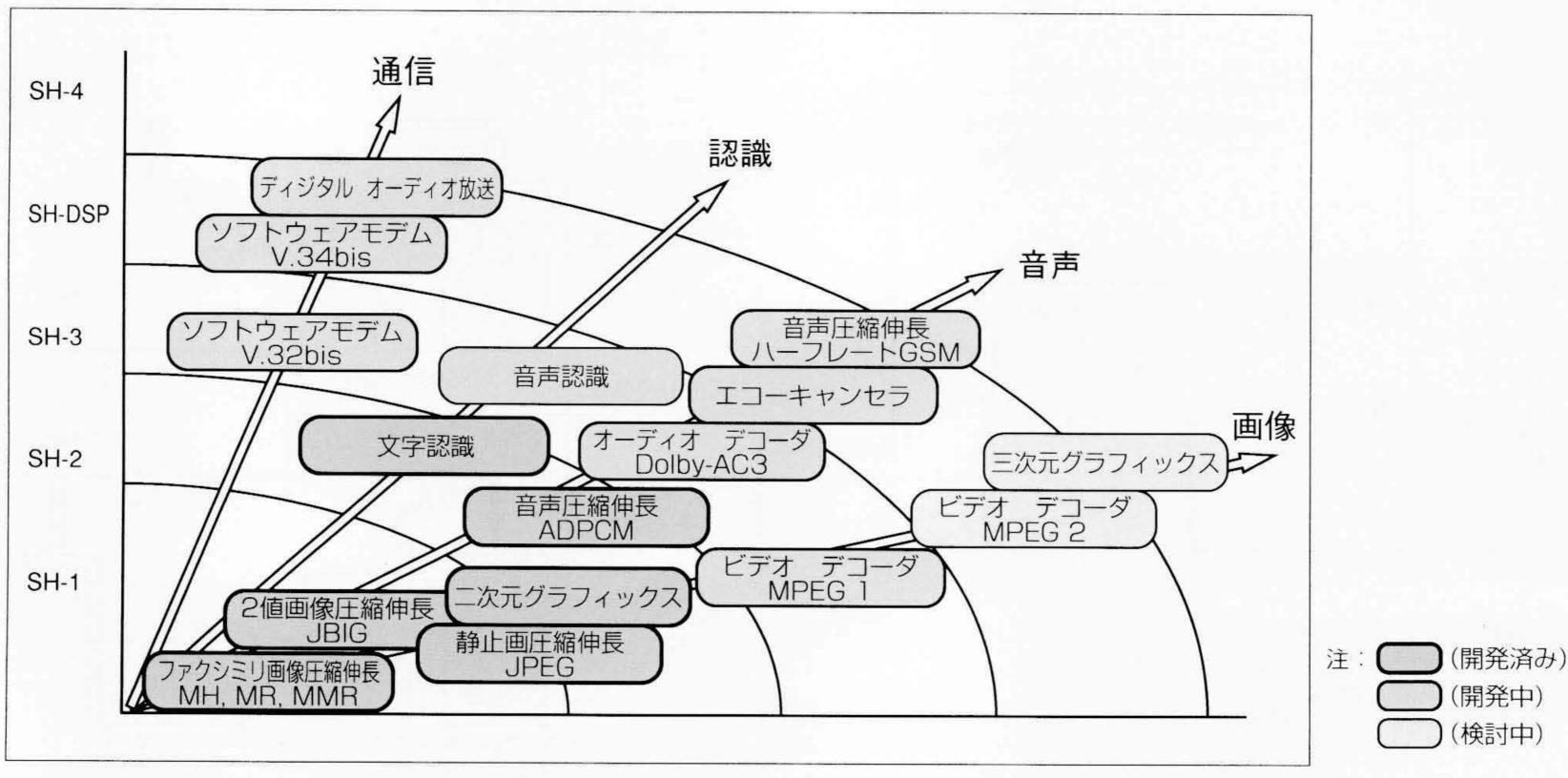

図8 SuperHファミリーのミドルウェア開発計画

CPUコアの開発と並行してミドルウェアの開発も進めている。SuperHファミリーを使用すればノマディックコンピューティングに必要な画像,音声,認識,通信などの処理がソフトウェアで実現できる。

OSのほかに、これを支えるミドルウェア(応用ソフトウェア)が不可欠である。SuperHファミリーでは、コアの開発と並行してノマディック、マルチメディア機器に多用されるミドルウェアを整備してきた。

このミドルウェアの開発計画を図 8 に示す。画像分野では、ファクシミリに使用されるMH/MR/MMRやJBIG(Joint Bi-level Image Coding Experts Group)の2値静止画圧縮伸長、JPEG(Joint Photographic Experts Group)静止画圧縮伸長、MPEG1(Moving Picture Experts Group 1)デコーダ、二次元グラフィックスなどのミドルウェアが開発済みまたは開発中である。

60 MHz SH-DSPの場合, DSPの並列命令, 1サイクル積和を活用して640×480画素(Y:Cr:Cb=4:1:1)のカラー画像を0.36秒でJPEG圧縮できる。これは専用ハードウェアで処理する速度に匹敵する。

音声分野では、PHS携帯電話などに使用されているADPCM (Adaptive Differential Pulse Code Modulation)音声圧縮伸長を開発している。また、DVD (Digital Video Disc)に使用されるDolby-AC3オーディオ デコーダ、セルラ携帯電話用フル・ハーフレートGSM (Global System for Mobile Communications)音声圧縮伸長、テレビ会議に使用されるエコーキャンセラなどを

開発中である。

通信分野ではモデムの国際標準規格であるV.32 bis (通信速度14.4 kビット/s), V.34 (通信速度28.8 kビット/s), インターネットの通信プロトコルのTCP/IP (Transmission Control Protocol/Internet Protocol)処理を開発中である。

### 6. おわりに

ここでは、ノマディック時代のコンピューティングを 支えるSuperH RISCマイコン技術について、SH-3の MMU、およびSH-DSPのアーキテクチャを中心に述べ た。また、これらのプロセッサの性能、機能を引き出す OS、ミドルウェアの開発状況にも言及した。

SH-3のMMU, TLBでは、高機能OSサポートに必要な 論理アドレス、物理アドレスの変換、および高度のメモ リ管理を行う。これにより、コンパクトなSuperHであり ながら、PC並みのOSサポートを可能としている。

SH-DSPは、ハーバードアーキテクチャおよびフレキシブルなDSP並列命令により、RISCマイコンでありながら汎用DSPクラスの信号処理能力も備えている。

今後も、SuperH RISC engineファミリーでのSH-4などの高機能化、高性能化を図っていく考えである。

#### 参考文献

1) 舘内,外:携帯型情報端末用低電力マイクロコンピュータ,日立評論,77,10,685~690(平7-10)