# 最先端半導体プロセス・製造技術の展望

## **Outlook for Advanced Semiconductor Process and Manufacturing**

尾内享裕 Takahiro Onai 木村紳一郎 Shin'ichirô Kimura

譲 Yuzuru Ôji 大 路 金井史幸 Humiyuki Kanai 山中俊明 Toshiaki Yamanaka

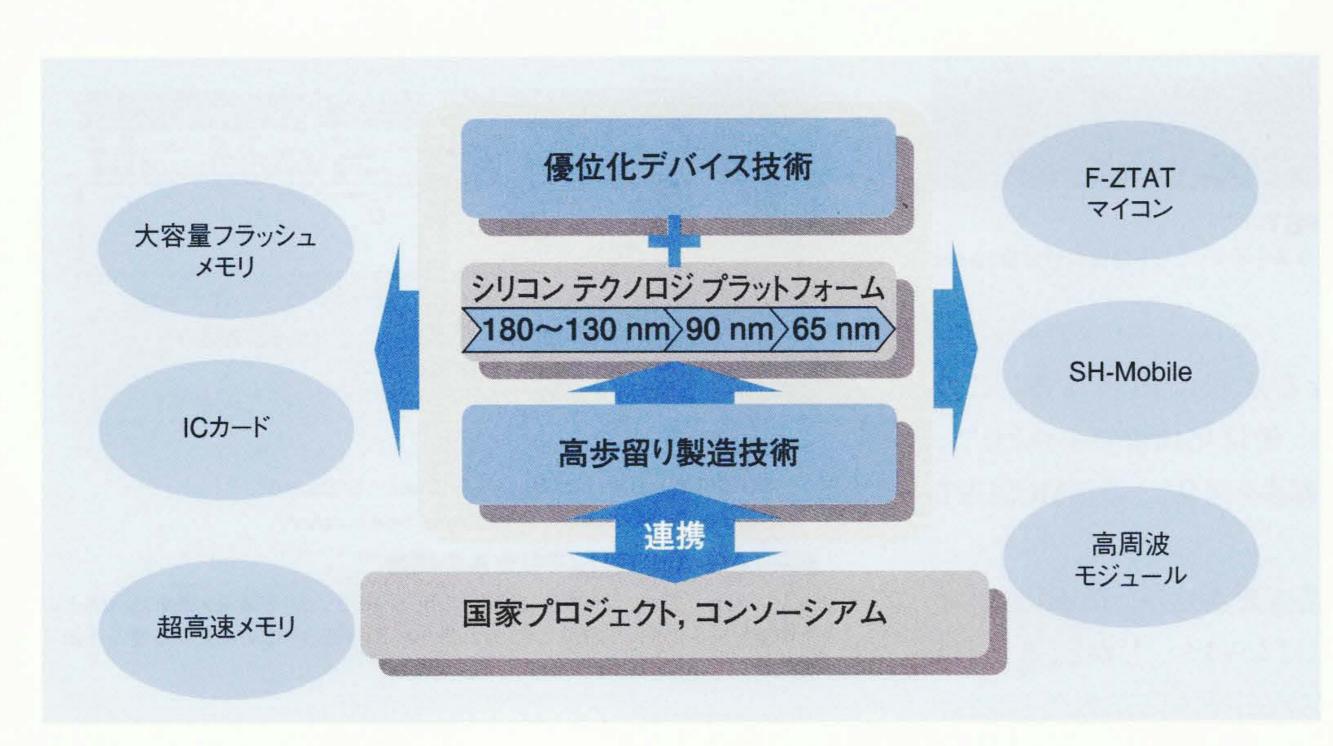

#### 優位化デバイス戦略

プラットフォームで開発した技術と優 位化デバイス技術により、特にマイコン を中心とした付加価値の高い製品へ展 開する。

#### 注:略語説明

IC (Integrated Circuits) FZTAT (Flexible Zero Turnaround Time)

日立製作所は,三菱電機株式会社と共同で株式会 社ルネサス テクノロジを設立し、シナジーによる半導 体事業の発展を図っていく。特にマイコンを中心とし た特徴製品のラインアップにより、ベストソリューショ ンとなるLSI(Large Scale Integration)の提供を強 化する。このためには、性能や機能だけでなく、「低コ スト」、「高信頼」、および"Time to Market"にも重点 をおいた開発を進める。これらを支えるのが、日立グ ループの半導体製造装置や、国家プロジェクト、コン

ソーシアムで開発した共通技術と高信頼・高歩留りの 製造技術である。

日立グループは、このような製造技術をベースに開 発したシリコン テクノロジ プラットフォームと優位化デ バイスを組み合わせることにより、F-ZTATマイコン、 SH-Mobile, 高周波モジュール, 大容量フラッシュメ モリ、ICカード、超高速メモリなどの特徴的な製品を 開発し、ユーザーの要求に迅速にこたえていく。

# はじめに

半導体産業は2001年に大きく落ち込み, DRAM (Dynamic Random Access Memory)を例にとると、価格の下落 などにより、1995年のピーク時(約5兆円)に比べて市場規模 は一十にまで縮小した」。2002年の回復にも勢いは見られず、 本格的な回復は2003年後半になるものと予測されている。こ のような厳しい状況に加えてメーカーの寡占化が進んでおり、 一つの製品の市場を多くのメーカーで分け合うという構図は、 大きく変わりつつある。

一方で、携帯電話、ディジタル家電、ビデオゲーム機などで 使われている特徴のある製品はフル生産状態にあり、優位技 術に支えられた競争力のある製品が重要になってきている。

日立グループは、このような状況を踏まえ、優位化技術の創 生と製品への展開を推進している。

ここでは、日立グループが取り組んでいる最先端半導体プ ロセスと製造技術について述べる。

# 最先端微細化技術

#### 2.1 CMOSデバイス技術

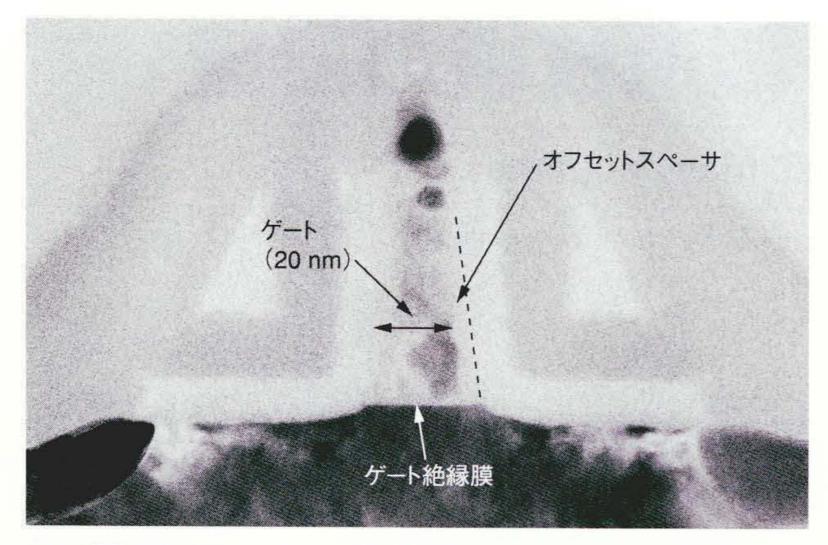

半導体デバイス・LSIの高性能化・高機能化の基本は微細 化である。日立グループは、ゲート電極寸法がわずかに 20 nmというMOSFET (Metal-Oxide Semiconductor Field Effect Transistor)を試作し、動作を実証するとともに、 微細化による性能向上を確認している20(図1参照)。これは,

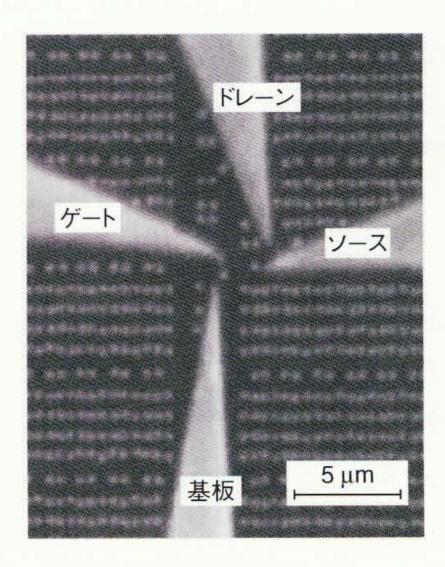

図 1 試作した20 nmゲートMOSFET

試作したMOSFETの断面電子顕微鏡写真を示す。ゲート電極の寸法は20 nm (0.02 µm)である。

3世代先の技術で必要となる寸法に相当する。この MOSFETを試作するにあたり、優位化技術の一つとして、 窒素を高濃度に含んだゲート絶縁膜を開発し、微細MOSFET の実現を可能にした<sup>3)</sup>。

ゲート絶縁膜はMOSFETの基本要素であり、微細化に伴って物理的な膜厚を薄くしなければならない。しかし、3 nm以下になるとトンネルリーク電流がゲート電極と基板間を流れ、低電力化の妨げとなる。今後要求されるゲート絶縁膜の膜厚は1.5 nm以下であり、リーク電流の低減が急務となっている。この課題に対する現実的な対策の一つが絶縁膜への窒素の導入であり、これまでもシリコン酸化膜を窒素プラズマ中で処理する方法が検討されてきた。窒素を導入することで絶縁膜の誘電率が大きくなり、物理膜厚を確保しながら、MOSFET特性に影響する電気的膜厚を薄くすることができる。

日立グループは、窒化膜の酸化という、従来とは異なる手法を用いて、膜中の窒素濃度を増やしながら、MOSFET特性に重要な影響を及ぼすゲート酸化膜と基板の界面での窒素濃度を抑制することに成功した。これにより、1.4 nmという極薄膜のゲート絶縁膜が開発できた。また、高濃度の窒素はp型ゲート電極から基板へのボロンの拡散も抑制することがわかり、これによる性能向上も観測している。

#### 2.2 大容量フラッシュメモリ

モバイル機器と家庭やオフィスをつなぐブリッジメディアとして、データ記憶用フラッシュメモリが生活の中に浸透し始めている。アプリケーションの一つは、その携帯性を生かしたプライベートネットワークである。ディジタルカメラで撮った画像をパソコンで編集したり、インターネットからダウンロードした音楽や動画コンテンツを、PDA (Personal Digital Assistant)や携帯電話で再生するなどの用途があげられる。もう一つは、企業や金融関連のデータを記憶するパブリックネットワークであり、顧客情報をフラッシュメモリに記憶し、出張先でPDAを使って確認するなどの使い方ができる。

このようなフラッシュメモリでは、以下の2点が重要な課題と

#### 注:略語説明

STI(Shallow Trench Isolation), D(Drain), S(Source) F-N(Fowler-Nordheim), SSI(Source Side Injection)

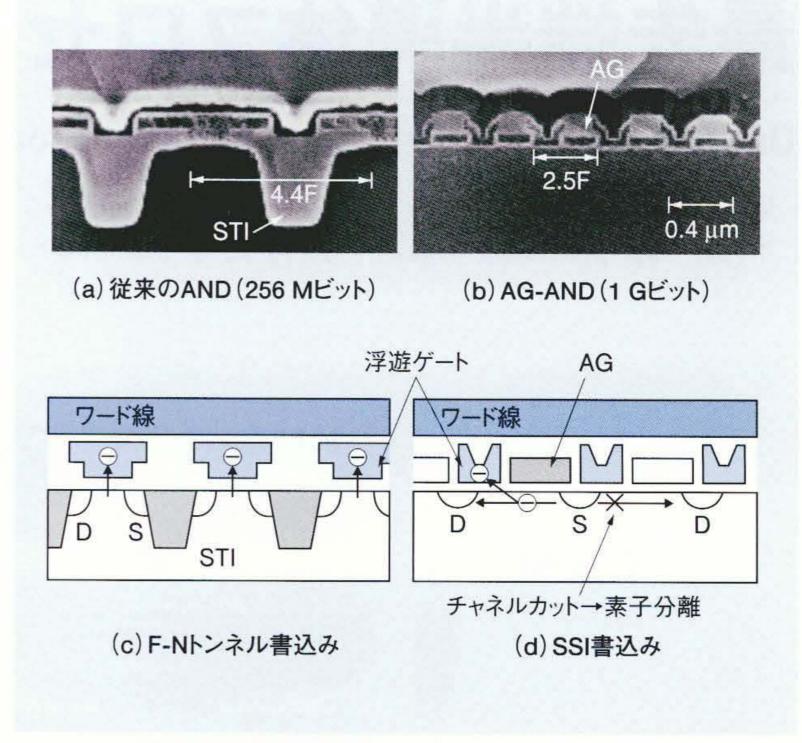

#### 図2「AG-AND型」メモリセルの構造

AG(Assist Gate)を持つAND型新フラッシュメモリセルと従来のAND型セルとの比較を示す。4.4F, 2.5Fは、それぞれ最小加工寸法(F)の4.4倍, 2.5倍の寸法である。

なる。第1は大容量化によるビットコストの低減である。このためには、一つのメモリセルに2ビット分のデータを記憶する多値記憶と、微細なメモリセルの組み合わせが有効である。第2は書込み速度の向上である。CD1枚分の音楽データ[MP3 (MPEG audio layer 3)方式で約64 Mバイト]を、ストレスなく数秒以下で記憶するためには、10 Mビット/sという従来の4倍以上の書込み速度が要求される。

日立製作所は、低コストと高速書込みを実現するフラッシュメモリとして、1 Gビット「AG (Assist Gate) - AND型」を開発した。(図2参照)。この方式では、メモリセル間の干渉を防ぐアシストゲートとデータを記憶する浮遊ゲートとを交互に配置した独自のメモリセル方式を採用している。これにより、溝を作ってセルを分離する従来のSTI (Shallow Trench Isolation)に比べ、セル面積を縮小することができる。また、書込み高速化のために、書込み方式を従来のF-N (Fowler-Nordheim)トンネル方式からホットエレクトロン方式に変更した。アシストゲートを用いてホットエレクトロンをソース側から注入することにより、浮遊ゲートへの注入効率を上げ、高速かつ並列の書込みを実現した。このメモリセルを0.13 μmプロセスで作ることにより、1 Gビット品では業界最小のチップ面積 (95 mm²)と、多値記憶では初めての10 Mビット/sの書込み速度を達成している。

今後は、このAG-AND型フラッシュメモリセルを優位技術とした各種フラッシュカードやシステムを製品化するとともに、0.09 μmプロセスの適用によっていっそうの低価格・高性能化を図り、顧客のニーズにこたえるメモリソリューションを提案していく。

|             | 浮遊ゲート型           | スプリットゲート型 | MONOS型  |         | FeRAM     | MRAM    | 相変化                                |

|-------------|------------------|-----------|---------|---------|-----------|---------|------------------------------------|

|             |                  |           | 全面記憶    | 局所記憶    | renaivi   | IVITANI | <b>ТНЖТЬ</b>                       |

| 記憶方法        | 浮遊ゲート            | 浮遊ゲート     | 窒化膜トラップ | 窒化膜トラップ | 強誘電体分離    | 磁気抵抗効果  | 相変化                                |

| 書換え電圧       | ±10 V            | 10~12 V   | ±6 V    | ±6 V    | <5 V      | <3 V    | <3 V                               |

| 書換え回数       | ~10 <sup>5</sup> | ~105      | 105~106 | ~105    | 1010~1012 | ~1016   | 10 <sup>10</sup> ~10 <sup>12</sup> |

| デバイス構造(模式図) | 浮遊ゲート            | 00000     | 窒化膜     | 窒化膜     | 強誘電体膜     | TRM     | カルコゲナイド                            |

注:略語説明 FeRAM(Ferroelectric RAM), MRAM(Magnetic RAM), TRM(Tamper-Resistant Module)

#### 図3 不揮発性メモリの比較

マイコンに混載の可能な不揮発性メモリとして期待されているメモリデバイスの特性比較を示す。

#### 2.3 優位化技術としてのメモリ混載

SoC(System on a Chip)は、デバイスの多機能化にとっ て不可欠であり、特に、不揮発性メモリの混載は優位技術と なる。不揮発性メモリにはさまざまなタイプがあり(図3参照), デバイスの用途,必要なメモリ容量,コストや各社の技術の 違いによってその選択肢が決まる。日立グループは、混載用 不揮発性メモリとして、ONO(酸化膜・窒化膜・酸化膜)を利 用したMONOS型メモリを他社に先駆けて開発し、ICカード用, CIM (Computer Integrated Manufacturing)カード用の チップとして実用化してきているが。このMONOS型不揮発性 メモリに関する研究と製品化で、第34回市村産業賞功績賞 を受賞した6。

MONOS型不揮発メモリでは、窒化膜(N)を酸化膜(O)で サンドイッチしたONOを使い、窒化膜中に電荷を蓄えることで 記憶保持動作を行う。浮遊ゲートを利用したメモリセルとは異 なり、酸化膜に欠陥があってもすべての電荷が消失すること はないので、信頼性に優れた不揮発性メモリを構成すること ができる。また、浮遊ゲートがないことから、低コスト化の点で も優れている。近年、このMONOS構造の優れた特徴を生か し、窒化膜中の複数個所に電荷を蓄える多値メモリ構造も提 案されているで。

日立グループは、このMONOS型メモリを優位技術として 位置づけ、さらなる改善を加えてSOCの高性能化・高機能化 を推進していく。

# 高歩留り・高信頼度の製造技術

#### 製造プロセスと加工ばらつき

ゲート寸法の微細化とともに, 高精度微細加工技術の重要 性が加速度的に高まってきた。90 nmノードの光リソグラフィー 技術では、KrF光 (λ=248 nm) から短波長化したArF光 (λ =193 nm)を露光波長に用いるとともに,「NA (Numerical Aperture)=0.75以上」の超高NA投影レンズを搭載したスキャ ン露光装置を適用する。

さらに、解像限界付近で低光学像コントラスト領域を使うた

め、位相シフトマスク露光法やOPC(Optical Proximity Effect Correction)技術といった超解像技術, 転写精度高 精度化技術が必須となる。

より短波長のF2光( $\lambda=157$  nm)を用いた露光装置,プロセ スの開発も進められているが、量産対応装置が90 nmノード 量産時期に間に合わないことから、90 nmノード以降でもArF 露光技術のさらなる延命化が必要である。

一方で短波長化に伴う大幅なコストアップが問題となる。こ のために、プロセス制御技術などの高度化によって寸法ばら つきを低減しつつ、製造コストアップを抑制することが製品競 争力をつけるうえで不可欠である。リソグラフィー工程での寸 法精度の劣化要因は,装置起因,プロセス起因などさまざま である(表1参照)。

特にMEF (Mask Error Enhancement Factor)が急増 しており、さらに高精度のマスクが必要となる。マスク面内寸 法の均一性の向上, OPC処理で発生した微小パターンの解 像性能などのマスク描画の高精度化と, 相反する描画時間 の短縮化が、OPC運用とマスク描画(EB:Electron Beam) 装置性能向上のかぎである。

また、露光装置では、ユーザー側で適用可能なレンズの収 差評価技術が広まってきたこともあり、レンズ収差量の低減が 進んできた。低次側収差量管理では十分であるとは言えない ので、いっそう高次側収差まで含めたレンズの低収差量化が

#### 表1 リソグラフィーでの寸法精度劣化の要因

精度劣化要因には装置起因、製造プロセス起因、マスク起因などさまざまなもの があり、特にマスク精度向上が必要となる。

|      | ショット内                                                 | ウェーハ内                                                    | ウェーハ間                                    |

|------|-------------------------------------------------------|----------------------------------------------------------|------------------------------------------|

| マスク  | マスク寸法のばらつき                                            |                                                          |                                          |

| 装置   | レンズ収差<br>フレア(レンズ, 照明系)<br>装置精度<br>(フォーカス,ステージ同期)      | 装置精度                                                     | 装置の安定性<br>(露光装置,レジスト処理装置)                |

| プロセス | 光近接効果<br>OPC補正誤差<br>レジストパタンラフネス<br>基板平坦度<br>(微小段差含む。) | レジストパタンラフネス<br>基板平坦度<br>(微小段差含む。)<br>下地膜分布<br>(膜厚, 光学特性) | 安定性<br>レジスト感度の変動<br>処理雰囲気の変動<br>下地膜のばらつき |

不可欠である。収差制御技術の優劣がデバイス性能の優劣 にまで直接影響する時代になってきた。露光装置には、極限 まで低収差化を図るとともに、光学条件、転写パターンに応じ た収差制御の実現が望まれる。

### 3.2 製造・検査装置への要求

一方,目標寸法精度がナノメーターレベルまで厳しくなり、 寸法ばらつき要因に占める測定ばらつき成分が無視できない ほど大きくなっている。また、OPC技術では、ルール作成と評 価のために、さまざまなパターンに対応する大量の寸法・形状 評価が必要とされる。さらに、生産効率を重視する生産ライン では、前述の多様な寸法ばらつき要因をインラインで確実に制 御することも必要である。

このため, 寸法・形状評価技術の高精度化, 高機能・高速 化,自動化への要求も強く,従来のインラインCD-SEM (Critical Dimension SEM)の改良に加えて、AFM (Atomic Force Microscope) や非破壊断面計測技術 (スキャタロメ トリ)などの新しい評価技術の導入も重要となっている。

さらに、これら技術を活用した間断なく稼動する装置により、 従来のロット管理よりも網羅的な品質制御を可能とする枚葉管 理手法を適用して、短TAT (Turnaround Time)でウェー ハを完成させる生産方式の確立が急務である。 具体的には, 以下に述べる要素技術開発が積極的に進められている。

(1) 複数工程連携Fab-wide APC(Advanced Process Control)

リソグラフィープロセス変動補正に加えてエッチングプロセス 変動補正までを含めたレジストパターン寸法フィードバック制御 技術と、レジスト寸法からエッチング工程でのスリミング量を制 御するフィードフォワード制御技術の開発である。

### (2) インテグレーテット、メジャメントと枚葉制御

リソグラフィーシステムとスキャタロメトリ、合せ測定など光学 式計測装置のシステム融合による枚葉制御化が推進されて いる。スキャタロメトリの機能検証が完了し、プロセス最適化 や異常検知機能も統合化が進められている。

#### (3) デバイスパターンの高速, 高精度計測

今後ますます狭小化するプロセスウインドウの評価とプロセ ス最適化のための高速多点寸法および形状計測技術では, 特に、デバイスパターンの二次元形状やインラインでの断面形 状管理化が必要である。デバイス特性に直接影響するゲート 寸法の制御の観点から、パターンエッジラフネスの定量評価 技術の確立が早急の課題となっている。

最後に、デバイス性能に対する寸法ばらつきの影響度が大 きいことから, 微細加工技術と設計技術とのいっそうの連携 を高め、ロバスト[強靱(じん)]なプロセス設計の実現がたい へん重要となる。これと同時に, 生産ラインでの装置動作情 報管理による装置安定稼動,変動要因の把握も必要となる。

高歩留り・高信頼度を図るために、多岐にわたるプロセス情

報の管理技術と, 随時最適化を広範に行う制御技術の統合 も必須である。

#### 3.3 Cu配線技術

130 nmノード・ダマシンCu製品では、トレセンティテクノロジー ズ社の300 mmウェーハ枚葉処理ラインを活用して, 2002年 下期から量産している。この製品は、メタル7層構造(Cu配線 5層構造)を持ち、層間容量低減のために低誘電率のフッ素 ドープSi酸化膜(FSG:誘電率3.7)と炭素ドープSi窒化膜 (SiCN:誘電率5)を適用することで、信号伝搬の速い高性能 配線を実現した(図4参照)。

Cuプロセスは、ライン構成やプロセスフローでAlプロセスと 大きく異なる。自己イオン化スパッタ装置やめっき装置に代表 される新タイプの製造装置が使用され, 配線加工にダマシン 法が用いられるが、さらに今回のケースでは300 mm製造ライ ンという特殊性が加わっている。200 mmからの移行に伴うプ ロセス上の大きな変更点は、(1) FSG成膜原料にTEOS (tetraetyl orthosilicate)を用いることで接着強度を向上さ せ、エッジ部のFSGはく離を防止したことと、(2)メタル研磨 残り防止のために非選択研磨スラリを導入し、メタル研磨時 に層間膜までも削り込んで局所と広域の両方の平坦性を実 現したことの2点である。

今後の技術動向については,次世代以降の配線容量低 減のため、90 nmノードでは炭素を含むSi酸化膜(SiOC)が、 65 nmノードではポーラス材料がそれぞれ用いられると言われ ている。低誘電率化のトレードオフとしては、機械的強度や耐 化学性の不足が問題になっている。これらの材料では、機械 的強度の指標であるヤング率(たわみ剛性)がSi酸化膜の 約号以下になる。そのため、膜界面の接着強度だけでなくバ ルク強度自体も小さくなり、Cu研磨でのはく離やスクラッチな ど加工プロセスの課題はいっそう厳しい方向に向かうことにな

図4 130 nmノード製品のCu5層配線の断面

Cu配線はデュアルダマシン法によって加工する。層間膜にフッ素ドープSi酸化膜 (FSG:誘電率3.7)と炭素ドープSi窒化膜(SiCN:誘電率5)を使用し、配線容量を低 減した。

る。研磨荷重の低減とともに、スラリ材料のさらなる改良が必 要である。補強対策としてSi酸化膜を積層する場合もあるが、 積層することで誘電率が増大してしまうという課題がある。こ のようなキャップ層を最小限にとどめる、あるいは最終的には 残さないために、プロセス技術が複雑化している。

また、層間膜の機械的なぜい弱さはパッケージング時のボ ンディングはがれなどの不良原因になる場合があり、後工程も 踏まえたLSI構造設計を広範囲で考える必要がある。現状で はすべての層間膜をLow-k(低誘電率)で構成することが難 しく、上層Cu配線でFSGを用いるなど、混用するケースも見 られる。

Low-k材料の耐化学性の不足も、やはりプロセスフローや 装置の仕様を大きく変える。レジスト除去工程では、高温化の 酸素プラズマ処理が使用できない。Low-k材料中に含まれる 炭素が抜けて,変質してしまうからである。

そのため、低温低圧条件下での酸素プラズマ、還元性プ ラズマの適用によって変質を防いでいる。また、耐化学性を 意識した処理が必要な工程として層間膜エッチング, Via洗 浄、Low-k上キャップ膜形成などがあり、場合によっては適宜、 表面処理を施す必要がある。

このように、世代交代のたびに新コンセプトに基づく装置と 材料の変更が必要となる可能性がある。これは, 設備投資 の増大や開発期間の長期化につながり、そのため、国家機 関や複数の企業との連合によって装置やプロセス開発が進 められている。

### 開発垂直立ち上げ技術

#### QTAT開発

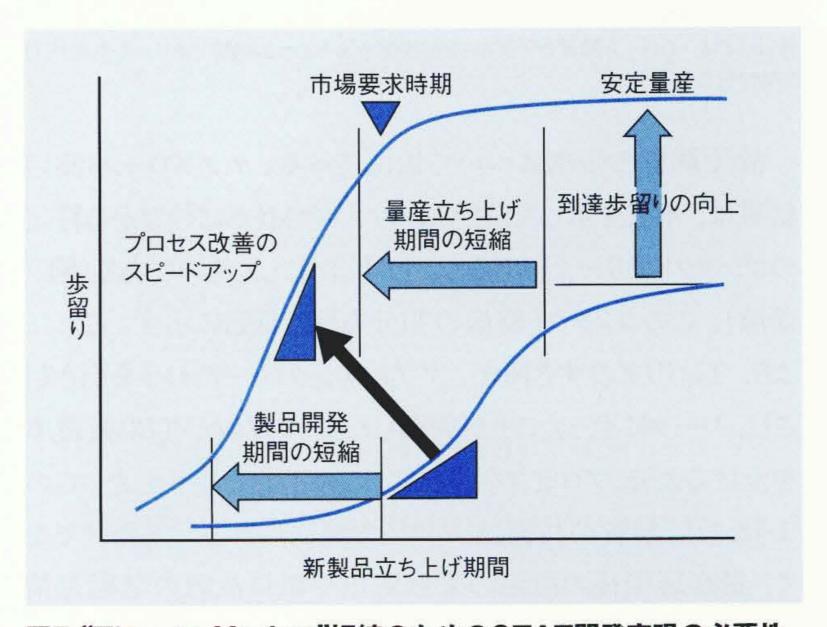

急速に変化する市場のニーズにこたえるためには、スピー ドとコストの改善が絶対条件である。製品開発と量産立ち上 げのスピードの向上, 安定した品質の高歩留り生産維持は, 半導体ULSI(Ultra Large-Scale Integration)での競争力 の強化に重要な要素である。安定量産に到達するまでの時 間を短縮するためには、開発段階で生ずるデバイス、プロセ スでの課題をいかに速く解析し、フィードバックするかがポイン トとなる(図5参照)。

#### 4.2 故障解析の技術

製品試作で発生した故障については、次の段階を踏んで 解析する。

- 論理解析による故障回路の部位の特定

- レイアウト上での故障位置の特定

- 物理解析による故障原因、発生メカニズムの特定

- プロセス履歴の解析による故障原因の特定

- プロセス改良へのフィードバック

これらの解析を短時間で行うためには上述の(1)~(4)を 「特定」しなければならないが、実際には「推定」である場合が 多い。 特に(1)については、90 nm以降の大規模なULSIに 対して,故障位置の特定を確実に短時間で行うための革新 的な技術開発が求められている。(3)についても確実なメカニ ズム解析を行うために、これまで以上に高い空間分解能と分 析感度が望まれている。このようなニーズに基づき, 日立グ ループは、ナノプローバ<sup>8)</sup>とTEM-EELS<sup>9)</sup> (Transmission Electron Microscope-Electron Energy Loss Spectroscopy)を開発し、QTAT(Quick Turnaround Time)開発 を実現している。

ナノプローバは、先端径がサブミクロンの4本のプローブを 任意の電極や配線、コンタクトに当てて、デバイス単体の電気 特性を評価するものである(図6参照)。この装置により、あら かじめ絞り込まれたいくつかの故障個所候補の単体特性を 測定し, 真の故障個所を特定する。これによって故障部位の 構造観察が確実に行えるだけでなく、構造と電気的な症状を ダイレクトに対応させることができる。一方, TEM-EELSは TEMの分解能で元素分析や結合状態が評価できるもので あるが, これを半導体の不良解析に適用できるように高感度 化することにより、TEMで確認された故障部位の詳細分析と、 その発生メカニズムの解析を可能にした。

図5 "Time to Market"短縮のためのQTAT開発実現の必要性 市場要求に合わせた量産の実現には、開発段階で生じた問題をすばやく解析し、 フィードバックすることが重要となる。

図6 ナノプローバの測定

ナノプローバは, 先端径がサブミク ロンの4本のプローブによって単体デ バイスの電気特性を評価する。

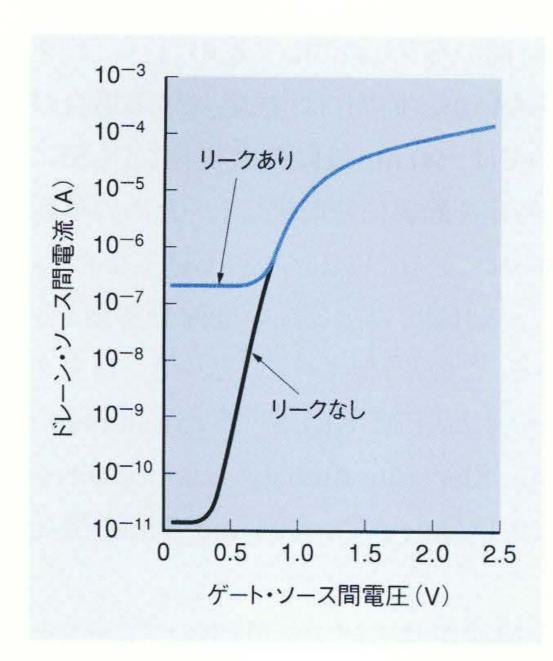

#### 図フ コンタクト評価 の結果

故障部SRAMを構成 する6個のMOSトランジス タで、当該部につながる 特定のコンタクトでリーク 電流があることが確認さ れた。

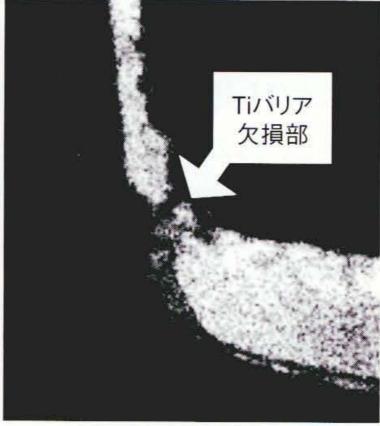

(b) Ti元素分布像

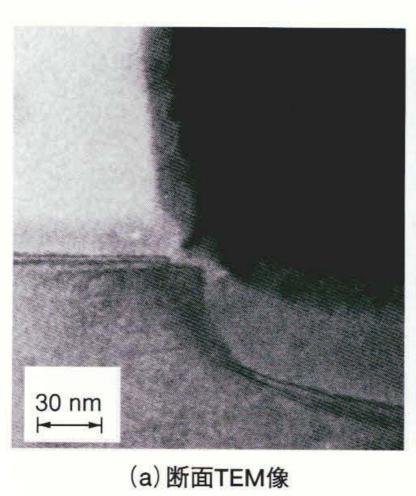

#### 図8 TEM-EELSによるTiバリア評価

断面TEM像(a)では、コンタクト底のおおよその構造が推定できる。Ti元素分布 像(b)では、Tiバリア膜厚が不均一で欠損部があることが明瞭であり、不良原因が 特定できる。

故障解析の事例について次に述べる。ナノプローバ測定 結果は,不良を示したSRAMの六つのMOSにつながる特定 のコンタクトでリークがあることを明らかにしたものである(図7 参照)。このコンタクト断面のTi分布像を図8に示す。これに より、Tiバリアのすき間が、ダブルエンクローチメントを引き起 こし、リークに至ったことが判明した。そのため、Tiの被覆率 を上げるようにプロセスを改良し、この不良を完治した。この ような故障解析の技術は、QTAT開発に寄与するだけでな く、量産展開後の故障の未然防止や類似故障の早期対策 を可能にする。

デバイス微細化は90 nm, 65 nm, 45 nmと, そのスピード を緩めてはいない。分析・解析技術が微細化を加速しかねな い状況にあり、いっそうの開発加速、技術革新が求められる。

# おわりに

ここでは、今後期待される優位化デバイスと、それを支える プロセス・製造技術として、ばらつき制御・信頼性の確保と いった「歩留り作り込み」の技術やQTAT開発・故障解析技 術が重要になることについて述べた。

日立グループは、製造装置開発とデバイス開発との緊密な

連携を図りながら新製品の早期立ち上げに取り組んでいる。 また、これらの製造技術や、シリコン テクノロジ プラットフォー ム、優位化デバイスを垂直統合することによってシナジーを生 かし、顧客のニーズにこたえるベストソリューションを提供して いくつ

#### 参考文献など

- 1) WSTS (World Semiconductor Trade Statistics:世界半導体市場 統計)

- 2) R. Tsuchiya, et al.: VLSI Technology Digest of Technical Papers 2002 Symposium, 150 (2002)

- 3) S. Tsujikawa, et al.: VLSI Technology Digest of Technical Papers 2002 Symposium, 202 (2002)

- 4) T. Kobayashi, et al.: Electron Devices Meeting, 2001. IEDM Technical Digest. International 29 (2001)

- 5) 神垣, 外:応用物理, 71, 9, 1138(2002)

- 6) http://www.sgkz.or.jp/nenpoh/34\_sangyo/index.html

- 7) B. Eitan, et al.: Ext. Abstract, 1999 Int. Conf. Solid State devices and Materials, 522 (1999)

- 8) S. Terada, et al.: Journal of Electron Microscopy 51(5), 291 (2002)

- 9) Y. Mitsui, et al.: Microelectronics Reliability 41, 1171 (2001)

### 執筆者紹介

#### 尾内享裕

1984年日立製作所入社,中央研究所 ULSI研究部 所属 現在, 半導体プロセス・デバイス技術の研究開発に従事 工学博士

応用物理学会会員, IEEE会員 E-mail: onai @ crl. hitachi. co. jp

#### 木村紳一郎

1980年日立製作所入社,中央研究所 ULSI研究部 所属 現在, 微細デバイス, 混載用不揮発メモリ, SOIの研究開 発に従事

工学博士 応用物理学会会員, IEEE会員 E-mail: sayo @ crl. hitachi. co. jp

#### 大路 譲

1977年日立製作所入社、株式会社ルネサス テクノロジ 生産 技術本部 ウエハプロセス技術統括部 先端デバイス開発部 所属

現在, 半導体先端プロセス・デバイスの開発に従事 IEEE会員

E-mail: oji. yuzuru@renesas. com

### 金井史幸

1981年日立製作所入社、株式会社ルネサス テクノロジ 生産 技術本部 ウエハプロセス技術統括部 プロセス開発部 所属 現在, 半導体プロセス技術および生産技術の開発に従事 E-mail: kanai. fumiyuki @ renesas. com

#### 山中俊明

1982年日立製作所入社、株式会社ルネサス テクノロジ 生産 技術本部 ウエハプロセス技術統括部 第三デバイス開発部 所属

現在、先端LSIプロセス・デバイスの開発に従事 IEEE会員

E-mail: yamanaka. toshiaki @ renesas. com