## Memory Technologies for the Multimedia Market

Katsuyuki Sato, Ph.D. Yoshikazu Saito Hitoshi Miwa Yasuhiro Kasama OVERVIEW: Different mobile multimedia-oriented products are successfully being introduced to the digital consumer-equipment market. These products include portable music players, digital video cameras and cellular phones that connect to various networks, centered around the Internet. In order to respond to these trends and the need for mobile equipment to be smaller, thinner and lower-power, Hitachi is promoting the development of largecapacity flash memory devices, SRAM devices intended for use in mobile equipment that use less power than conventional devices, and space-saving DRAM devices with wider bit configurations. Meanwhile, the high-end information equipment market, typically represented by servers and workstations, is growing significantly in line with the rapid penetration and expansion of the Internet. The capacities of built-in memory are also becoming larger. This is supported by the increased demand for larger builtin memory units. These market situations have led Hitachi to introduce new large-capacity memory modules.

### INTRODUCTION

INCREASING numbers of mobile multimedia products are successfully being introduced to the digital consumer-equipment market and demand for these products is expected to continue to grow strongly in the near future. Such products include handheld PCs, digital still cameras, and smart phones, as well as portable music players, digital video cameras, and cellular phones for connection to the Internet and other networks.

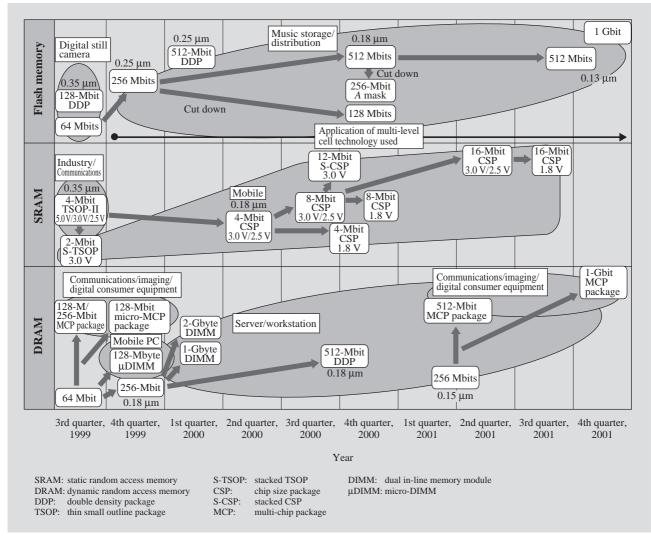

On the other hand, the memory capacity of highend information equipment such as servers and workstations is constantly being increased to keep pace with the rapid penetration and expansion of the Internet and intranets (see Fig. 1).

The following is a description of the types of memory products used in the latest multimedia equipment and their specifications.

### THE NEED FOR FLASH MEMORY

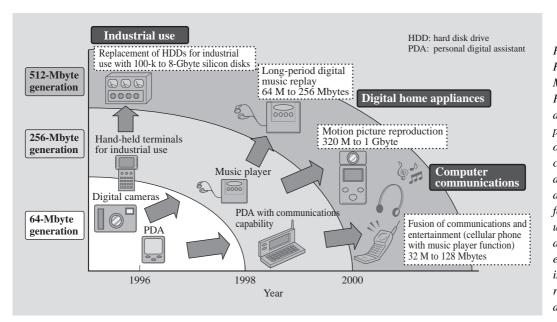

Large-capacity flash memory devices were initially used as external storage media for portable PCs in industrial applications. Makers of digital still cameras then started to employ flash memory in their products, and this generated a significant expansion in demand. The fields of application now include Internet- and other network-connectable portable music players, digital video cameras and cellular phones (see Fig. 2). In the industrial field, the use of silicon disks is becoming widespread as small HDDs are replaced by flash memory devices.

# LARGE-CAPACITY FLASH MEMORY DEVICES

Users in the ever-increasing number of fields of application for flash memory require products that consume less power and are contained in smaller packages so that they have a smaller mounting area. Larger and larger capacities are also required to support the growth of the Internet. Hitachi has developed multilevel flash memory technology and has used its 0.18µm technology to successfully realize the world's first 512-Mbit flash memory.

### Hitachi's Development Plan for Large-Capacity Flash Memory

In response to the increasing demand for largecapacity flash memory devices, Hitachi has developed AND-type memory cells that enable high-density, high-speed writing, erasing and reading with equal efficiency. In the 4th quarter of 1999, Hitachi succeeded in developing a 0.25-µm 256-Mbit flash memory device. This was achieved by adding multilevel cell technology for recording 2 bits in a single

Fig. 1— Hitachi's Development of Memory Devices in Response to the Advance of Multimedia Applications. Hitachi is developing a wide variety of SRAM- and DRAM-based memory products in response to the steady growth of the multimedia market.

Fig. 2—Market Penetration of Flash Memory. Flash memory devices have penetrated the fields of computer communications and digital home appliances. Demand for flash memory for use in industrial applications is also expanding, as, for instance, HDDs are replaced by silicon disks.

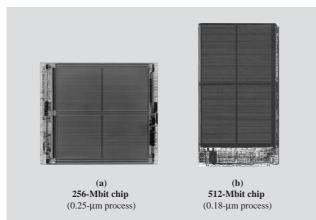

Fig. 3— AND-Type Multi-Level Flash Memory Chips. The above figure shows the 256-Mbit and 512-Mbit flash memory chips developed to meet the demand for large-capacity memory devices. The 0.18-µm technology used to produce the 512-Mbit flash memory device succeeded in cutting the chip area by approximately 10% compared with that of 256-Mbit flash memory devices using 0.25-µm technology.

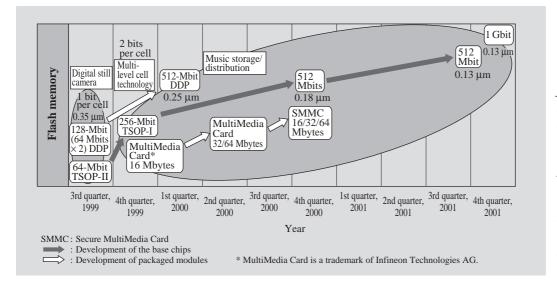

memory cell. Fig. 3 (a) is a photograph of the chip. Hitachi plans to take the lead in the large-capacity flash memory business with the new products it is introducing in the near future. These will include (1) the 512-Mbit DDP (double density package) contained in TSOP (thin small outline packages) configured by stacking two 256-Mbit flash memory chips, (2) a 512-Mbit monolithic and a 1-Gbit DDP flash memory device based on 0.18-µm technology, and (3) a 0.13-µm technology-based 1-Gbit monolithic flash memory device (see Fig. 4).

### 0.18-µm 512-Mbit Flash Memory

The pursuit of finer patterning of 256-Mbit flash

memory devices led to the development of the 512-Mbit flash memory device [see Fig. 3 (b)].

The 0.18-µm technology used to produce the 512-Mbit flash memory device succeeded in cutting the area of memory cells by 50% and the chip area by 10% compared with the corresponding areas of the 0.25-µm technology-based 256-Mbit flash memory device.

The 512-Mbit flash memory device will operate on 1.8 V, as well as on the 3.3-V operating voltage. Its power-saving design has reduced the amount of current used for reading by 60% compared with the figure for the 256-Mbit flash memory device, and this significantly affects the battery life in actual use.

These features make the new device more suitable for use in digital still cameras and digital music players. A single chip in a music player is now able to record up to one hour of music (equivalent to a CD) while a chip in a digital still camera is able to store over 300 million pixels of image data.

In the current 0.25-µm generation, Hitachi has introduced MMC (MultiMedia Card) and MS (Memory Stick) products that are suitable for a wide variety of applications. The same effort will be maintained in the 0.18-µm generation, based on the 512-Mbit flash memory device, in order to meet the rising demands of customers.

# LOW-POWER SRAM FOR MOBILE EQUIPMENT

### The Application of Low-Power SRAM

In the cellular phone industry, there are strong demands for smaller phones, and for multiple functions to allow users to enjoy a variety of Internet services

Fig. 4— Hitachi's Development Plan for AND-Type Flash Memory Devices. Multi-level cell technology and state-of-the-art fine patterning technology are being employed in the development of flash memory devices of greater capacity than ever before. and longer calling/waiting times.

Two types of memory are installed in cellular phones. NOR-type flash memory is used to store programs and low-power SRAM (static random access memory) is employed as the working memory in the processing of various tasks.

Many requirements are imposed on the working memory. For instance, its mounting area must be small; it must consume little power so that battery-powered operation remains convenient; the supply voltage range must be wide; the operating temperature range must be wide; and it must be capable of holding data at low voltage levels (so that a button battery can be used to retain data stored in memory).

### Features of Low-Power SRAM

In response to these requirements of cellular phones, Hitachi has developed low-power SRAM devices that allow high-density assembly.

Their features for use with mobile equipment are: (1) the world's smallest mounting area, (2) low levels of power consumption, (3) high operating speeds and (4) a wider range of operating supply voltages (see Table 1).

State-of-the-art 0.18-µm CMOS (complementary metal-oxide semiconductor) technology and the latest circuit technology have been applied to SRAM to realize working memory devices with unrivaled capacity, high performance, a small mounting area and low power consumption. Their wider supply voltage

## TABLE 1. Major Specifications of Low-Power SRAM Devices for Cellular Phones

State-of-the-art processing technology, the latest circuit technology and CSP assembly technology have been combined to realize world-class performance.

|                       | 4-Mbit low-power                         |                | 8-Mbit low-power                         |                   |

|-----------------------|------------------------------------------|----------------|------------------------------------------|-------------------|

|                       | SRAM device                              |                | SRAM device                              |                   |

| Configuration         | 256 k words $\times$ 16 bits             |                | 512 k words $\times$ 16 bits             |                   |

| Supply voltage        | 2.2 - 3.6 V                              | 1.65 – 2.2 V*1 | $2.2 - 3.6 \; V$                         | $1.65 - 2.2 \; V$ |

| Operating temperature | $-40 - 85^{\circ}C$                      |                | -40 - 85°C                               |                   |

| Address access time   | 70 ns                                    | 85 ns          | 55*²/70 ns                               | 85 ns             |

| Operating current     | 25 mA<br>(max.)                          | Same as left   | 35 mA<br>(max.)                          | 25 mA<br>(max.)   |

| Standby current       | 0.8 µA<br>(standard)                     | Same as left   | 1.5 μA<br>(standard)                     | Same as left      |

| Package               | 48-pin CSP                               |                | 48-pin CSP                               |                   |

| Overall size          | $6.5 \times 6.5 \times 1.2 \text{ (mm)}$ |                | $9.8 \times 6.5 \times 1.2 \text{ (mm)}$ |                   |

\*1: Under development.

\*2: Development is planned

ranges make them most suitable for battery-powered systems. Low levels of power consumption and noise are achieved by arranging the memory cells in such a way that they are only activated when writing or reading starts.

Ease of handling and high densities of assembly are realized by the small chips, which have been made possible by the use of 0.18-µm CMOS technology (i.e., state-of-the-art fine-patterning technology) and CSP (chip size package) technology.

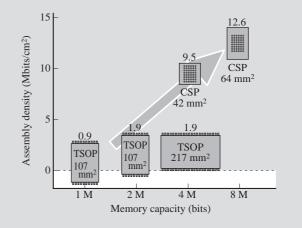

Fig. 5 shows a comparison of the assembly densities of the low-power SRAM devices and Fig. 6 shows the 4-Mbit SRAM chips.

TSOP: thin small outline package, CSP: chip size package

## Fig. 5— Changes in the Density of Assembly of Low-Power SRAM Devices.

High-density assembly is realized by state-of-the-art finepatterning technology and CSP (chip size package) assembly technology.

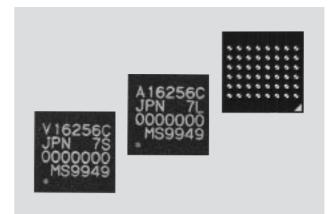

Fig. 6—4-Mbit Low-Power SRAM Chips.

The above figures show the 4-Mbit low-power SRAM chips produced by using 0.18-µm processing technology and CSP assembly technology.

### **DEVELOPMENT OF DRAM PRODUCTS**

### Application

The high-end of the information equipment market represented by servers and workstations is rapidly growing as it moves to keep pace with the increasing penetration of the Internet and the soaring numbers of subscribers, full-scale launches and rapid expansion of various forms of EC (electronic commerce) and the increasing need for small to middle-sized businessoriented CAD/CAM image-editing equipment. The capacity of the memory devices built into individual servers and workstations is rapidly being expanded to meet these needs, and this in turn is increasing the demand for large-capacity memory modules. In the digital consumer-equipment market, mobile multimedia products like handheld PCs, digital still cameras, and smart phones are recording rapid rates of growth and forever changing our lifestyles. Since these products must be compact and have a low profile to be suitable for mobile use, DRAM modules for use in such products must have space-saving features and wide bit configurations.

# Developing Large-Capacity Modules Based on the 256-Mbit SDRAM Device

To keep pace with the enhanced capabilities of the CPUs, larger and larger memory capacities are required on those servers and workstations that carry out vast numbers of arithmetic operations. At the same time, the memory is required to consume less power. Memory capacities of several dozen gigabytes are now required for individual machines. However, when such restrictions as the space for memory assembly on the system and the number of slots available are considered, this requirement cannot be met unless single memory modules are capable of providing memory capacities as high as 1 Gbyte.

Chip sets capable of supporting 1-Gbyte and larger memory units are beginning to appear on the market. However, when the current mainstream 64-Mbit SDRAM (synchronous DRAM) device is used, only 128 Mbytes are available in a single memory module. Even when stacked TCP (Tape Carrier Package) technology is used, 256 Mbytes is the upper limit. In spite of these difficulties, however, Hitachi has

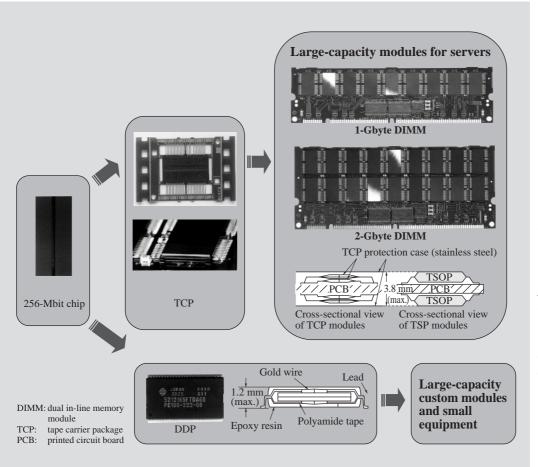

Fig. 7-256-Mbit SDRAM for Large-Capacity Modules (512-Mbit DDPs of 1- and 2-Gbyte DIMMs). TCP technology has made these largecapacity modules possible. The 1- and 2-Gbyte modules are created by using thirty-six and seventy-two 256-Mbit SDRAM chips, respectively. The capacity of individual SDRAM chips is also increased thanks to DDP technology.

succeeded in developing 1 and 2 Gbyte modules. Thirty-six or seventy-two 256-Mbit SDRAM chips (TCP; respective totals of 1 and 2 Gbytes) are assembled on a single printed circuit board, making large-capacity, compact systems possible (see Fig. 7).

As for expanding the capacity of individual SDRAM chips, Hitachi has applied DDP technology to successfully produce a 512-Mbit product. Two 256-Mbit SDRAM devices are placed back-to-back in a single package. The pin layout on this product is upwardly compatible with that of the 256-Mbit SDRAM chips. The result is twice the memory capacity and the same assembly area for 54-pin, 400-mil (approximately 10.16 mm) TSOP-II packages. Although this product will be mainly used to configure large-capacity modules, demand for its use in small portable equipment is also expected.

### Space-Saving SDRAM Chips

Hitachi has introduced the micro-DIMM (Dual Inline Memory Module) and MCP (multi-chip package) SDRAM chips to meet the strong demand for space-saving products for use in digital consumer equipment.

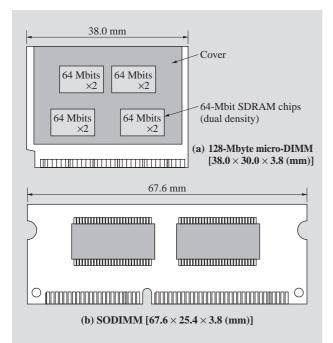

## Fig. 8— A Comparison of the Appearance of SODIMM and Micro-DIMM Packages.

The width and area of a micro-DIMM module are approximately 1/2 and 2/3, respectively, those of an SODIMM. Stacked-TCP technology allowed the assembly of sixteen 64-Mbit SDRAM chips on both sides of a 128-Mbyte product. These products are configured from 64-Mbit SDRAM chips — one of the world's smallest chip products — and by employing high-density assembly technology.

### Micro-DIMMs

Space-saving SODIMMs (small outline DIMMs) used to be employed as the memory units of notebook PCs. However, the growing market for smaller sub-notebook PCs demands DIMMs that are even more space-saving. The micro-DIMM was thus proposed to meet this demand and is already employed in some sub-notebook PCs. The mounting area of a recent micro-DIMM is only about 2/3 the area required by an SODIMM (see Fig. 8).

Hitachi used its stacking technology to introduce the world's first 128-Mbyte product of which eight TCPs were assembled on one side. 64- and 32-Mbyte products were then added to create a lineup that fully meets the current needs of customers.

### MCP-SDRAM Products

Customers required more compact SDRAM products for use in digital consumer equipment such as digital cameras, and used to complain that the conventional TSOPs were too large.

TABLE 2. Comparison of the External Appearance of MCP-SDRAM Products

The MC-FBGA (multi-chip fine-pitch ball grid array) supports up to  $\times$  32 bit organization and the MC-BGA (multi-chip ball grid array) up to  $\times$  64, compared with the  $\times$ 4/ $\times$ 8/ $\times$ 16 supported by standard SDRAM products.

|                     | MC-BGA                                                      | MC-FBGA                       | Standard package     |

|---------------------|-------------------------------------------------------------|-------------------------------|----------------------|

| External appearance |                                                             |                               |                      |

| Package             | BGA                                                         | FBGA                          | TSOP                 |

| Number of pins      | 108                                                         | 90                            | 54                   |

| Memory capacity     | 256 M/128 M bits                                            | 128 M bits                    | 128 M/64 M bits      |

| Bus width           | ×64/×32                                                     | ×32                           | ×16/×8/×4            |

| Size (mm)           | $14.0 \times 22.0$                                          | $10.0 \times 13.0$            | $11.76 \times 22.22$ |

| Thickness (mm) max. | 2.35                                                        | 1.45                          | 1.20                 |

| Applications        | Communication/<br>imaging/<br>digital consumer<br>equipment | Digital consumer<br>equipment | General purpose      |

MC-BGA: multi-chip ball grid array, FBGA: fine pitch BGA

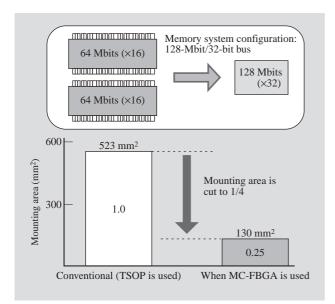

Fig. 9— The Space-Saving Effect of the 128-Mbit MC-FBGA. Employing a 16-Mbyte  $\times$  32 bit product, widely used in digital cameras and PDAs (personal digital assistants), allowed the chip-mounting area of the SDRAM on the bus system to be cut to 1/4 of the value for a TSOP.

To solve this problem, Hitachi developed an MCP (Multi Chip Package)-SDRAM product with multiple SDRAM chips assembled on a single substrate (see Table 2).

Space-saving and support for multiple bit organization are features of this product. For the 128-Mbit/32 bit bus systems widely employed in the digital cameras of today, Hitachi has succeeded in cutting the mounting area to 1/4 of the value for a TSOP, realizing a long-awaited saving of space (see Fig. 9).

The MC-FBGA (multi-chip fine-pitch ball grid array) supports up to ×32 bit organization and the MC-BGA (multi-chip ball grid array) up to ×64, compared with the  $\times 4/\times 8/\times 16$  supported by standard SDRAM products. This wide bit-configuration expands the scope of application to include the communications and image-processing fields.

### CONCLUSIONS

Of Hitachi's many memory products, this article has focused on large-capacity flash memory, lowpower SRAM, and large-capacity, space-saving DRAM products. The technologies used in these products and their current and future fields of application have been described.

In the coming information society, centered around the Internet, customers will increasingly demand that memory products for use in a wide variety of equipment be smaller, more energy efficient and capable of handling larger amounts of data. Hitachi will keep responding to such needs by constantly increasing its reliable, user-oriented product lineup.

### **ABOUT THE AUTHORS**

#### Katsuyuki Sato

Joined Hitachi, Ltd. in 1976, and now works at the 2nd Product Strategies Department of the Technical Marketing Division, Semiconductor & Integrated Circuits. He is currently engaged in the development of technology for DRAM products. Dr. Sato is a member of the IEEE Solid State Circuits Society, and can be reached by e-mail at sato-katsuyuki@elpida.com.

#### Yoshikazu Saito

Joined Hitachi, Ltd. in 1982, and now works at the SRAM Design Department of the System Memory Business Division, Semiconductor and Integrated Circuits. He is currently engaged in the design of SRAM. Mr. Saito can be reached by e-mail at saito-yoshikazu@hitachi-ul.co.jp.

### Hitoshi Miwa

Joined Hitachi, Ltd. in 1985, and now works at the Flash Development Center of System Memory Business Division, Semiconductor & Integrated Circuits. He is currently engaged in the development of AND-type flash memories. Mr. Miwa can be reached by e-mail at miwa-hitoshi@sic.hitachi.co.jp.

#### Yasuhiro Kasama

Joined Hitachi, Ltd. in 1984, and now works at the HNS Support Engineering Department of the DRAM Business Division, Semiconductor & Integrated Circuits. He is currently engaged in starting up the volume production of DRAM products. Mr. Kasama can be reached by e-mail at kasama-yasuhiro@sic.hitachi.co.jp.