# 118

# Semiconductor Yield Enhancement Solutions for Next Generation

Yasutsugu Usami Naoyuki Eguchi Seiji Isogai OVERVIEW: Among LSI (large-scale integration) manufacturers, yield enhancement is one of the essential means of securing a profit. For this purpose, semiconductor inspection systems are required to handle a larger number of defects to be detected and localize the faulty points. To cope with the above, Hitachi High-Technologies Corporation has been offering the following solutions for supporting efficient review of such a large number of defects and enhancing yield: (1) "yield enhancement system" for connecting inline inspection tools and defect review tools, (2) "inline inspection solution" for inline control of wafer production process and localization of a faulty process causing the detected defects.

# INTRODUCTION

PROCESS engineers have been focusing on the "improving yield control" and their activities have significantly benefited the profitability of the worldwide semiconductor device business. LSI manufacturers have continuously improved measurement and inspection tools to obtain higher sensitivity and throughput in order to improve yield.

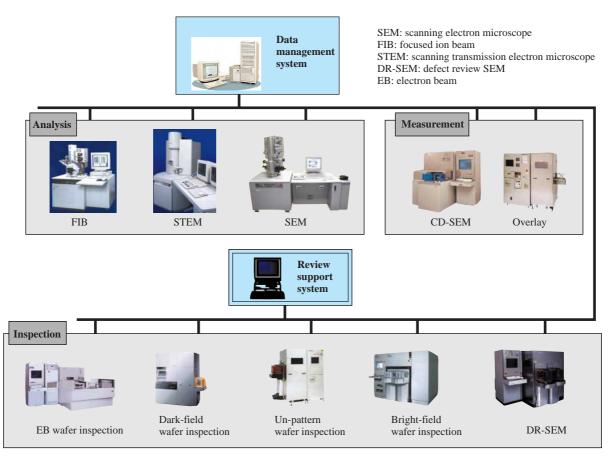

Fig. 1 —Hitachi's Semiconductor Inspection Systems.

Hitachi has proposed a total solution for semiconductor yield enhancement with a review system for connection between inspection tools and integrated control systems for each tool for measurement, inspection, and analysis on semiconductor manufacturing lines.

Around ten years ago, the ratio of inspection tools for process control to the total investment for production equipment was about 5%. In recent years, the ratio has risen to 10% to 20%. However, the recent framework in which more advanced inspection tools are installed to collect defect data from multiple processes and feed it back to the process has brought about a fall in productivity. This situation is directly related to inspections and the extension of the data analysis time due to a rapid increase in the inspection output data, which has entailed an undesirable effect, i.e., additional labor costs. Thus, the simple improvement model "yield improvement = installation of high-sensitivity inspection tool" is becoming inappropriate. Abiding by this trend, it is important for the next-generation yield-control systems to integrate high-performance semiconductor tools and evaluation tools organically and utilize them as a total system so that they can analyze the cause of a yield reduction speedily and feedback the result to the line without degrading the improvement of production efficiency irrespective of finer semiconductor devices and the complexity of the process.

In consideration of the above background, this paper introduces performance-upgraded semiconductor inspection and evaluation tools, applicable to 90-nm nodes and beyond, and describes solutions for semiconductor yield enhancement (see Fig. 1).

# HITACHI'S SEMICONDUCTOR MEASUREMENT AND INSPECTION SYSTEMS

Hitachi has been offering high-performance semiconductor and evaluation tools applicable to 130to 90-nm nodes as systems to support yield enhancement in semiconductor manufacturing. We have offered inline inspection solutions, control of the wafer production process, classification of the detected defects, and an evaluation system solutions for analyzing the cause of each problem identified during an inline inspection. Also, in response to the recent "e-manufacturing formation," Hitachi has begun an examination of integrated metrology and has been stepping up its approach to tools, such as an in-situ floating particle monitor for real-time measurement of particle behavior around a wafer and an optical CD (critical dimension) for measuring surface film thickness and the cross section. Such integrated metrology will upgrade Hitachi's APC (advanced process control) technology and provide solutions to the problems that contradict each other; "productivity improvement [QTAT (quick turnaround time) of production]" and "yield improvement (increase of inspection time)."

This section will introduce the inline inspection solutions.

## Hitachi's Inline Wafer Inspection Tools

A high sensitivity/throughput inline inspection tool is applied for tracking the yield of a production line in real time. At present, inline inspection tools are classified into three categories. First, the laser inspection tool (dark-field type) can detect particles and pattern defects on a wafer having a comparatively low step structure with high sensitivity and throughput, and it is efficient when used for inspections after the damascene CMP (chemical-mechanical polishing) in the Cu process, which has recently become known as a problem process. Second, the visual wafer inspection tool (bright-field type) is capable of detecting pattern defects and particles with a sensitivity as high as a few tens of nm even on a wafer having a high-step structure such as the one after etching. Third, the SEM (scanning electron microscope) wafer inspection tool (SEM type) utilizes an electron beam, and it can detect very small defects undetectable with optical inspection equipment, and electrical conductivity or nonconductivity of a deep-hole structure, such as in a plugging step resulting from a contrast due to electric potential. Hitachi can provide all three inspection tools listed above, which provide efficient use of process equipment so that it performs as intended and defects are minimized. A simple explanation is given here on the next-generation bright-field type inspection tool and a system which classifies detected defects speedily and enhances yield.

# Hitachi Bright-field Type Optical Wafer Visual Inspection Equipment "HA-3000"

Table 1 shows the required inspection sensitivity for each node as described in ITRS (International Technology Roadmap for Semiconductors) on an annual basis. The numerics of inspection technology applicable to the coming 90-nm and node beyond are shown in Red Brick Wall and their solution is being sought. To answer such needs, Hitachi has marketed the next-generation inspection tool "HA-3000" as a solution.

Fig. 2 shows the appearance of this tool. It is commonly usable for 8- and 12-inch wafers with a two-cassette FOUP (front open unified pod) unit mounted at the front. The STI (shallow trench

Table 1 Technology Requirements for Defect Detection — Near Term This table shows the defect detection technology requirements from ITRS. (Node = 1/2 DRAM metal 1 pitch)

| Year<br>Technology node<br>Patterned wafer inspection, PSL sphere           | 1999<br>180 nm<br>es at 90% | 2000<br>capture, e | 2001<br>130 nm | 2002<br>sensitivity | 2003<br>y (nm) | 2004<br>90 nm | 2005 | Driver          |

|-----------------------------------------------------------------------------|-----------------------------|--------------------|----------------|---------------------|----------------|---------------|------|-----------------|

| Process R&D at<br>300 cm <sup>2</sup> /h (ITRS: 1999 edition)               | 54                          | 49                 | 39             | 36                  | 33             | 27            | 24   | 0.3 	imes DR    |

| Process R&D at<br>300 cm <sup>2</sup> /h – 1 W/h (Sc. 2.0)                  | 108                         | 98                 | 78             | 72                  | 66             | 54            | 48   | 0.6 	imes DR    |

| Yield ramp at<br>3,000 cm <sup>2</sup> /h (ITRS: 1999 edition )             | 72                          | 65                 | 52             | 48                  | 44             | 36            | 31   | 0.4 	imes DR    |

| Yield ramp at<br>1200 cm <sup>2</sup> /h – 4W/h (Sc. 2.0)                   | 144                         | 131                | 104            | 96                  | 88             | 72            | 56   | 0.8 	imes DR    |

| Volume production at 10,000 cm <sup>2</sup> /h (ITRS: 1999 edition)         | 90                          | 81                 | 65             | 60                  | 55             | 45            | 35   | 0.5 	imes DR    |

| Volume production at $300 \text{ cm}^2/\text{h} - 10 \text{ W/h}$ (Sc. 2.0) | 180                         | 150                | 130            | 120                 | 110            | 90            | 80   | $1.0 \times DR$ |

PSL: polystyren latex

[International Technology Roadmap for Semiconductors (ITRS): 1999 Edition]

Fig. 2 — Appearance of the Tool. DUV optical wafer inspection tool "HA-3000."

isolation) process and gate process in FEOL (frontend of line), both are coming close to the limit of lithography, while the difficulty experienced checking for smaller defects is becoming greater. Inspection sensitivity inside the Red Brick Wall has been realized by the "HA-3000." The greatest feature of this tool lies in that DUV (deep ultraviolet) optics are put to use in detection tasks for the first time in the world. In addition to the DUV optics, ultrahigh resolution imaging optics are used to enhance the image resolving power of fine patterns. As fine patterns become denser, the quantity of reflected light from a wafer usually decreases, so that only dark and unclear images are obtainable. These ultrahigh resolution imaging optics can resolve the images of fine patterns unattainable by using conventional optics owing to an emphatic detection of diffracted light from the patterns. As a technique applied to the fine process, reduction of image detection size (pixel size) is an important subject. However, simply reducing the pixel size entails a fall in processability, so high resolution and sensitivity detection cannot be achieved at a high throughput.

As a solution to the problem of increased investment for inspection equipment, the "HA-3000" incorporates a process unit that provides image processing performance a few times higher than that of the conventional tools. Also, to suppress noise components in the obtained image, such as image sway, high-rigidity optics and a sample stage capable of high-accuracy control are essential. Thus, the "HA-3000" employs high-accuracy and rigidity optics and a stage capable of suppressing the noise components contained in the obtained image. By improving on the image detection system, image resolution can be enhanced significantly. But such improvements alone fall short of a high defect detecting performance in actual inspections. A visual wafer inspection tool compares two images (neighboring cells in cell to cell comparison or neighboring dies in die to die comparison) and detects a subtract between them as a defect. If color variation, grain or the like has occurred on the two images, such a factor will be detected as a defect and counted as a nuisance. To circumvent detection of such nuisances, degrading inspection sensitivity is unavoidable. In the "HA-3000," a new image processing technique has been adopted to eliminate such inspection disturbing factors, thus

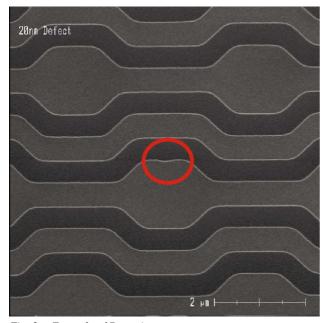

Fig. 3 —Example of Detection. This picture shows the 20-nm defect detection using Hitachi's standard wafer.

realizing high-sensitivity inspection.

Fig. 3 shows an example of detection with the "HA-3000." In this figure, detection of a defect as small as 20 nm can be confirmed. Also, since the "HA-3000" has a much higher inspection sensitivity than the conventional tool, the volume of sampled inspection data is extremely large, processing this much data would be problematic. To resolve this situation, the "HA-3000" has, on the tool side, a function for classifying the inspected contents simultaneously with inspection, hence it can notify problems in each wafer at an early point in time. In order to utilize the above inspection data efficiently for yield improvement, the following systems can be used.

# FULLY AUTOMATIC REVIEW SEM "RS-3000" AND REVIEW SUPPORT SYSTEM "RI-1000"

Along with the introduction of high-sensitivity inspection equipment such as the "HA-3000" and increases in wafer diameter, the number of defects to be detected can reach a few or a few tens of thousands. Therefore, it is becoming unrealistic to expect that an operator can review all defects. This gives rise to the need for an efficient review (image observation) tool that use high-resolution SEM. Hitachi has met this need by offering the fully automatic review "SEM RS-3000." This is a powerful tool for enhancing yield because it is capable of reviewing many defects promptly in full automatic mode and classifying them

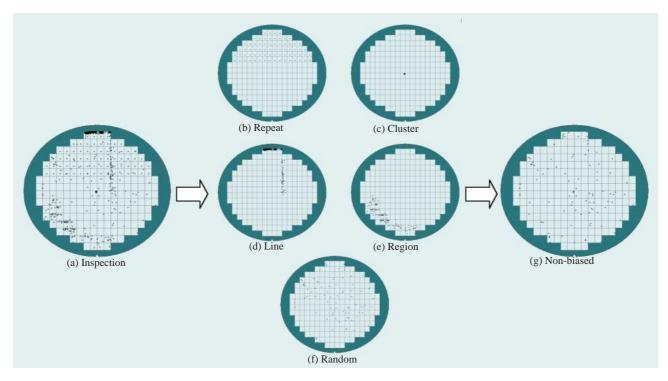

Fig. 4—Review Support System for Defects. The figure shows the flow of review support system using Hitachi's inspection tools and review system.

automatically into the ones having either a high fatality or non fatality in real time. On the other hand, there is also a need to select typical defects among a group of a few or a few tens of thousand defects and review them efficiently, and feedback the result to the yield analysis. In yield analysis, important topic now is how best to sample the defects to be reviewed among all the detected defects. To meet this, Hitachi has developed a review support system "RI-1000" and has been proposing a system composed of this efficient review tool and inspection equipment (see Fig. 4).

Though a defect inspection tool outputs large amounts of defect data as described above, a representative review tool, review SEM has a throughput of 300 to 600 DPH (defects per hour). Filling in the gap between the defect output and review throughput requires efficient selecting and reviewing of typical defects efficiently and feed back of the result to the yield analysis instead of reviewing all the detected defects. Therefore, in yield analysis, how to sample the defects to be reviewed among all the detected defects is important. Hitachi has developed a review support system "RI-1000" and has been proposing a system composed of an efficient review instrument and an inspection tool. The review support

Fig. 5 — Defect Examples Detected by Inspection Tools. The defects have been classified by "RI-1000."

system is detailed below:

#### Review Support System "RI-1000"

The review support system is intended to efficiently select the defects to be reviewed from a very large volume of defect data obtained from inspection equipment in the inspection step of the semiconductor manufacturing process.

The conventional manual sampling by an operator has involved a problem in that the contents of sampling differ among operators. And if defects gather locally on a wafer (cluster) or defects are not evenly spread on a wafer, for example, the conventional random sampling may have resulted in a local unevenness as well. To prevent this, the sampling results are checked one by one, and if there is a problem, the sampling condition has to be set again, thus consuming substantial labor and time.

In E-sampling (effective sampling) of RI-1000, the characteristic of defect distribution in a wafer is determined according to the inspection data, and defects are classified as follows according to the respective characteristics; (1) repeat defect, (2) cluster defect, (3) linear defect, (4) region defect and (5) random defect (see Fig. 5).

In reviewing, overlaying is carried out in steps of chip or shot and a common defect is classified as a repeat defect. A local wafer area where many defects have occurred is classified as a cluster defect. Defect density is judged according to the distance between defects and the number of defects in the local area. A linear defect is judged depending on the distance between defects and the linearity of the relevant defects.

A region defect is judged through detection of unevenness in the defect density spread in a wafer and pattern matching with about 3,000 kinds of circular or massive dictionary patterns.

Random defects are obtained by removing repeat, cluster, linear, and region defects from all the defects. They are the defects randomly spread in a wafer.

From the defects classified into each category, the ones to be reviewed are freely sampled so that review can reflect the defect distribution over the entire wafer.

In the examples shown in Fig. 5, the in-wafer distribution of a total of 7,846 defects (a) detected with the inspection tool is analyzed and classified into five categories. And three defects are sampled in repeat defects, three defects in cluster defects, six defects in linear defects, five in region defects, and 65 in random defects. Thus, 82 defects in total are sampled as the ones to be reviewed (g).

In addition to the method of setting the number of defects to be sampled in each defect category as

exemplified above, E-sampling allows setting of the ratio of defects to be sampled among the respective categories.

Also, the review support system provides the following functions besides the E-sampling function. (1) Filter function

(a) Category filter: Defects to be reviewed are selected based on the information categorized by the ADC (auto defect classification) function with the inspection tool or manual classification.

(b) Defect size filter: Defects to be reviewed are selected according to a defect size detected with the inspection tool.

(c) Previous-process defect filter: Under conditions of the same lot and same wafer, coordinates are compared between the results of the previous and latest inspections, and judgment is made whether each defect is attributable to the previous process or it has been detected in the latest process. According to the result of this judgment, defects to be reviewed are selected.

(d) Filter for common defects between wafers: In the inspection of two or more wafers under the same lot and process conditions, coordinates are compared between the results of the latest inspection and the one just before it, and judgment is made whether each defect is common among the wafers. According to the result of this judgment, defects to be reviewed are selected.

## (2) Sampling function

(a) Concentric sampling: A wafer is divided into concentric circles and a sampling ratio is set for each area after division.

(b) Angle-division sampling: A wafer is divided into angles and a sampling ratio is set for each after division.

(c) Chip-specified sampling: Sampling is carried out with a chip number (X, Y) specified.

(d) Chip-based sampling: Defect density is calculated on each chip and defects are automatically selected from a chip in which defect density is higher.

The defects to be reviewed can be restricted by the combined use of the filter function and sampling function.

In addition, combinations of those functions can be registered and saved as defect sampling recipes for each product (kind) and inspection process. When inspection data is sent from the inspection tool to the review support system with the recipes registered in advance, sampling will be automatically carried out according to a recipe that matches the relevant product and inspection process, thereby preparing the data of the defects to be reviewed. The review tool has only to acquire the prepared data, so more efficient review work can be achieved.

Besides the above-mentioned filter and sampling functions, the RS-1000 can control not only review data, but also defect inspection data by the functions for (1) lot list display, (2) map display, (3) review image display, etc.

## YIELD CONTROL SYSTEM "MI-7000"

For yield improvement in mass production, it is important to arrange the inspection process effectively based on the data accumulated in the stage of development and trial manufacture and analyze yield by a statistical method.

Yield control system "MI-7000" has the greatest feature in its automatic acquisition, saving, and analysis of large-volume inspection data from the inspection tool. In particular, its analysis software called "trace report function" has many applications as a yield analysis method, by which the correlation between the defect detected in each inspection process (adder defect) and probe inspection data is quantified as yield's influence (yield impact) and a fatality ratio of defect (killer ratio). The trace report function has realized a very fast processing of yield correlation analysis through the introduction of the dedicated DWH (data warehouse) for analysis, and it can determine the process which has caused a fall in yield. Therefore, countermeasures can be taken earlier than before.

In yield analysis, classification of defects provides important data. The defects effectively sampled with the review support system are automatically classified and categorized quickly by the ADR (auto defect review)/ADC function of a review SEM. The categorized review result data is sent to the yield analysis system via the review support system. In trace report, yield impact, and killer ratio are computed based on the defects detected in each inspection process and the probe inspection data. For this computation, the defect classification information sent from the review support system is utilized as effective data. The result of classification with the review instrument is registered as category data in a trace report and the yield impact in each category can be analyzed by selecting the category of the defect to be analyzed.

As mentioned above, integration of the inspection

tool, the review support system, and the yield control system enables the review support system to efficiently sample the data from the high-sensitivity inspection equipment. Further, the data directly concerning the yield degrading factors can be offered to users by letting the yield control system analyze the result of classification with the review tool.

## CONCLUSIONS

This paper has introduced semiconductor yield enhancement support systems for the next generation.

For responding to 90-nm and even finer-node devices, not only the tool must have a high sensitivity, but also a solution needs to be offered so as to cover the entire line including the yield enhancement support systems, yield control systems, etc. Hitachi offers state-of-the-art yield enhancement support tools covering inline measuring instruments, inline inspection equipment, and troubleshooting systems.

Hitachi will continue to supply and propose inspection systems in response of customers' needs. Also, in response to the recent popularization of IT (information technology), Hitachi has begun an examination of "e-manufacturing formation" and "integrated metrology," techniques for incorporating measuring instruments in manufacturing tools and has been stepping up its approach to instruments, such as an in-situ floating particle monitor for real-time measurement of particle behavior around a wafer under processing, and a built-in type optical CD capable of measuring the surface film thickness and the physical shape and dimensions of a wafer. Such response is Hitachi High-Technologies Corporation's solutions to the problems contradictory to each other; "productivity improvement" and "yield improvement." We will supply and propose inspection systems also in the future for answering customers' need.

## REFERENCES

Y. Usami et al., "Approach to e-manufacturing for Realizing Next-generation Semiconductor Production," *Hitachi Hyoron* 84, pp. 226-230 (Mar. 2002) in Japanese. Semiconductor Yield Enhancement Solutions for Next Generation 124

- (2) N. Eguchi et al., "Semiconductor Yield Enhancement Solution for Next Generation," *Hitachi Hyoron* 84, pp. 261-266 (Mar. 2002) in Japanese.

- (3) Y. Usami, "Next-generation Surface Inspection and Evaluation System for Semiconductor Wafers," Non-destructive Test Vol. 50, No. 5 (2001).

- (4) Y. Usami et al., "Semiconductor Inspection Systems for the 130 nm Generation," *Hitachi Hyoron* 82, pp. 667-670(Oct. 2000) in Japanese.

- (5) Y. Usami et al., "Semiconductor Inspection Systems for Yield Enhancement," *Hitachi Hyoron* **81**, pp. 661-666 (Oct. 1999) in Japanese.

#### **ABOUT THE AUTHORS**

#### Yasutsugu Usami

Joined Hitachi, Ltd. in 1984, and now works at the Products Marketing Department, the Device Manufacturing Systems Business Group of Hitachi High-Technologies Corporation. He is currently engaged in marketing semiconductor inspection systems. Mr. Usami is the SEAJ EES Committee chairman, and a member of the Vacuum Society of Japan and Japanese Society of Electron Microscopy, and can be reached by e-mail at usami-yasutsugu@nst.hitachi-hitec.com.

#### Naoyuki Eguchi

Joined Hitachi, Ltd. in 1992, and now works at the Products Marketing Department, the Device Manufacturing Systems Business Group of Hitachi High-Technologies Corporation. He is currently engaged in marketing semiconductor inspection systems. Mr. Eguchi can be reached by e-mail at eguchi-naoyuki@nst.hitachi-hitec.com.

#### Seiji Isogai

Joined Hitachi, Ltd. in 1981, and now works at Naka Division, the Design & Manufacturing Group of Hitachi High-Technologies Corporation. He is currently engaged in development of semiconductor inspection and yield management support systems. Mr. Isogai is a member of the Japan Society of Applied Physics (JSAP) and the Institute of Electronics, Information and Communication Engineers (IEICE), and can be reached by e-mail at isogai-seiji@naka.hitachi-hitec.com.