アニーリング型/ゲート型量子コンピュータの研究開発

ハイライト

古典コンピュータでは計算ができなかった大規模問題を扱う手段として,量子コンピュータが期待を集めている。日立は,顧客にとってより良いソリューションを提供することを目的として,アニーリング型とゲート型に分類される量子コンピュータの開発を行っている。

アニーリング型については,2013年よりCMOSアニーリングマシンの研究開発を開始した。これは量子効果を用いないQuantum Inspired Computerであるため,大規模問題を扱うことができ,多くの顧客連携を経て2020年に事業化発表を行うまでに至った。ゲート型については,英国の日立ケンブリッジラボでの基礎物理中心の研究に対して2018年にギアチェンジし,日本も含めて開発体制を強化して,大規模問題が扱えることを特長としたシリコン量子コンピュータの研究開発を開始した。本稿では,これらの取り組みについて述べる。

1. はじめに

量子コンピュータはAI(Artificial Intelligence)と並ぶ先端技術として大きな期待を集めている。量子コンピュータはコンピューティングの世界にいわゆる0→1の変化をもたらす可能性を秘めているが,一方で,日立の社会イノベーション事業の下での独自ハードウェア開発にはどのような意味があるのか。近年の先進IT企業に見られる共通した傾向は,水平分業から垂直統合へのバリューチェーンの変化である。その中心にはサービスがあるが,ハードウェアはこれらの企業のサービスを顧客に届ける箱・手段の一つとして位置づけられており,顧客リレーションシップを優位に構築するための鍵にもなっている。サービスやソリューション・アプリケーションのコモディティ化の影響もあると考えられるが,独自ハードウェア開発への投資はエッジ側に加えてクラウド側にも展開されている。このように,ハードウェア・ソフトウェア・サービスの壁,さらには,業種の壁をも越えて顧客満足度にのみ注力している強い姿勢(既存企業や中間業者に対するデジタルディスラプション)が見て取れる。量子コンピュータの開発は先端IT企業においてもまだ道半ばではあるが,顧客満足度を起点に研究開発が行われている。

これらの動向を通じて,社会イノベーション事業の下での新しいコンピュータの開発とは,「顧客にとってのより良いソリューションの提供に役立つもの」であるということが改めて確認できる。したがって,日立の開発する量子コンピュータの比較対象は,現在のソリューションを実現している既存の古典コンピュータであり,他社の量子コンピュータではない。

2. 日立の量子コンピュータ研究開発

前述したとおり,日立にとってのコンピュータ開発は「顧客にとってのより良いソリューションの提供に役立つもの」である。現在の古典コンピュータでは解けない問題,例えば大規模な問題を扱えることが量子コンピュータ開発の目的である。実際に現在の多くの問題は大規模になると計算爆発などで効率的に計算できず,できる範囲の近似解で済ませたり,あるいは,問題規模を小さくして解き,その解を本来得たい解の代替として使用したりしている。以下,量子コンピュータをアニーリング型とゲート型に分け,それぞれの取り組みについて述べる。

2.1 日立のアニーリング型量子コンピュータ CMOSアニーリングマシン

2011年7月に当時の日立製作所中央研究所で新世代コンピューティングプロジェクトが発足し,顧客にとってのより良いソリューションの提供に役立つ,新しいコンピュータの研究開発がスタートした。2011年5月にカナダのD-Wave Systems Inc.が「世界初の商用量子コンピュータ」をうたったD-Wave※1)Oneを発表した年である。同ニュースは世の中を駆け巡ったが,同時に明らかになってきたのは,それは量子コンピュータとして教科書などに記載されているものとは異なる種類の量子コンピュータであるという点であった。これはいわゆるアニーリング型の量子コンピュータであり,特定問題(組合せ最適化問題)向けの専用機である。また,同社の量子コンピュータの量子コヒーレンス寿命※2)は短く,量子計算による高速化には至っていないのではないかというのが当時の多くの見方であった。日立は,組合せ最適化問題の解法であれば,特に量子効果を使わなくても古典コンピュータより優位になる可能性があると考え,2013年にCMOS(Complementary Metal-oxide Semiconductor)アニーリングマシンの研究開発をスタートした。現在ではQuantum Inspired Computer(量子に触発されたコンピュータ)と呼ばれているが,正にその道を切り拓いてきた。

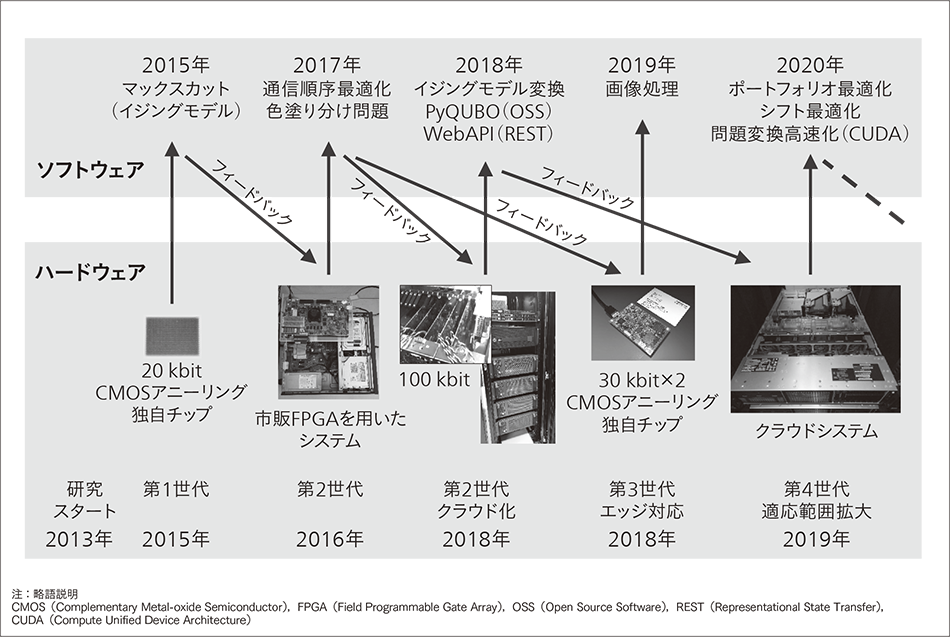

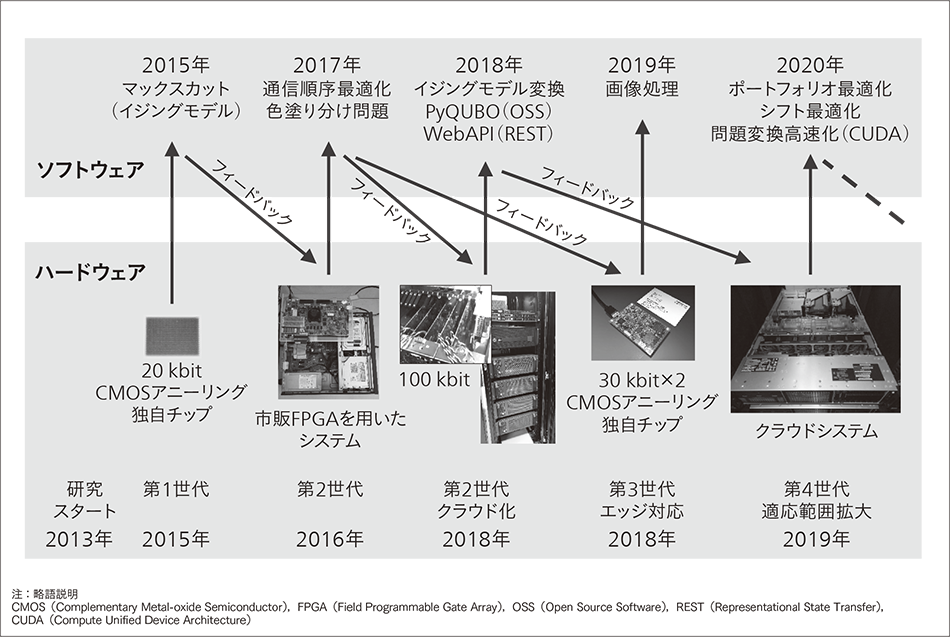

図1にCMOSアニーリングマシンのこれまでの開発の流れを示す。「顧客にとってのより良いソリューションの提供に役立つもの」になるには,ソフトウェアとハードウェアのコ・デザイン(チックタック開発)が鍵である。顧客業務をCMOSアニーリングマシンで解けるモデルに落とし込む,あるいはCMOSアニーリングマシンが適用可能な業務を見つけ出すという進め方は,顧客業務が既存のものであれば既存ソリューションの代替となり,参入が難しい。一方で,例えば従来1秒で解いていたものを0.01秒で解けるようになったとしても,既存の性能値で間に合っていたためにその新しい性能値に対して大きなメリットを生み出せず,CMOSアニーリングマシンを導入する意欲が顧客に生まれない。この均衡状態を打開するには,新しいハードウェアを用いたPoC(Proof of Concept),PoV(Proof of Value)を具体的に行い,その結果をフィードバックして次のハードウェアおよびソフトウェア,そしてそれらを用いたアプリケーションの開発を行うというサイクルを何度も繰り返す方法が有効である。そのため,CMOSアニーリングマシンの開発にはSE(System Engineer)が積極的に関わり,顧客とのPoCを行い,実際に損害保険ポートフォリオ最適化の実証実験も行っている1)。また,中央研究所においても,COVID-19拡大の状況下で密にならずに研究活動を継続するため,CMOSアニーリングを用いた研究員のシフト作成を行い,それに従った勤務を行うことでアプリケーションの効果を実証した。これらの取り組みの結果,2020年に勤務シフト最適化ソリューションとして事業化発表を行うまでに至っている2)。

- ※1)

- D-Waveは,D-Wave Systems Inc.の登録商標である。

- ※2)

- 量子効果の一つである,コヒーレンス状態を維持し続けられる時間。

図1|CMOSアニーリングマシンのこれまでの開発の流れ  ソフトウェアとハードウェアのコ・デザイン(チックタック開発)の流れを示す。

ソフトウェアとハードウェアのコ・デザイン(チックタック開発)の流れを示す。

2.2 日立のゲート型量子コンピュータ 大規模集積シリコン量子コンピュータ

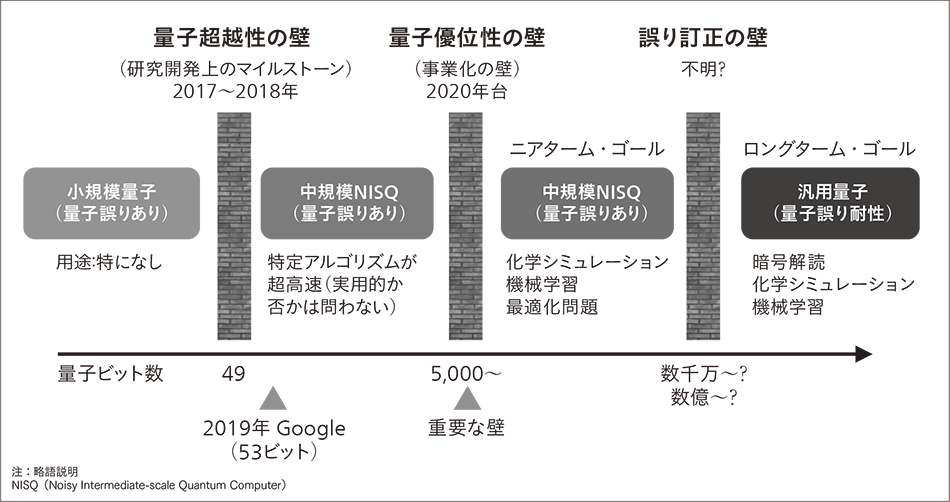

図2|量子コンピュータの開発における壁  2019年に米国カリフォルニア工科大学のJohn Preskill教授によって提唱された汎用量子コンピュータ実現までの壁を示す。

2019年に米国カリフォルニア工科大学のJohn Preskill教授によって提唱された汎用量子コンピュータ実現までの壁を示す。

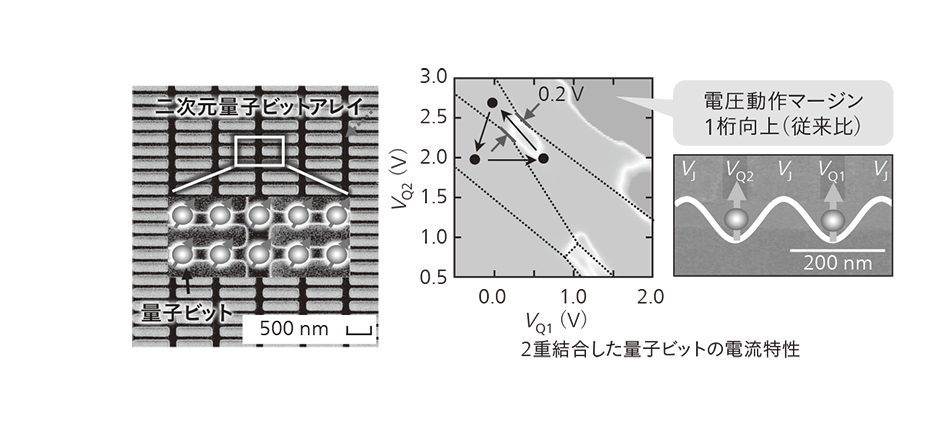

図3|シリコン量子ビットアレイの基本技術  日立は,量子基礎物理と大規模半導体メモリ制御技術を融合し,半導体チップの上に多数のシリコン量子ドットを二次元状に配列して制御するアレイ基本技術を開発した。動作検証を行ったところ,電子1個を閉じ込める箱となる「量子ドット」を,所望の位置に二次元アレイ状に形成できることが確認できた。さらに従来構造に比べて,大規模量子ドットの安定動作につながる動作電圧マージンが一桁向上することを確認した。

日立は,量子基礎物理と大規模半導体メモリ制御技術を融合し,半導体チップの上に多数のシリコン量子ドットを二次元状に配列して制御するアレイ基本技術を開発した。動作検証を行ったところ,電子1個を閉じ込める箱となる「量子ドット」を,所望の位置に二次元アレイ状に形成できることが確認できた。さらに従来構造に比べて,大規模量子ドットの安定動作につながる動作電圧マージンが一桁向上することを確認した。

図2は,2018年に米国カリフォルニア工科大学のJohn Preskill教授によって整理された量子コンピュータの開発における壁を図示したものである。一つ目の壁は量子超越性の壁(Quantum Supremacy)と呼ばれるもので,実用的か否かは問わない特定のアルゴリズムで量子コンピュータが古典コンピュータの性能を凌駕するというものである。この壁は,2019年にGoogle社によって突破された3)。これは研究開発上の重要なマイルストーンの一つであるが,開発された量子コンピュータの産業・社会的な価値はまだ明らかではない。次の壁は量子優位性の壁(Quantum Advantage)と呼ばれる壁であり,産業・社会的に有用なアルゴリズムで量子コンピュータが古典コンピュータの性能を凌駕するというものである。この壁は未だ誰にも破られていない。さらにその次の壁を突破して教科書に書かれているような汎用量子コンピュータを実現するには長い年月が必要だが,一方で,その手前の段階でも産業・社会的に有用な量子コンピュータが存在し得ることが分かる。これはNISQ(Noisy Intermediate-scale Quantum Computer)と呼ばれているが,量子力学的な振る舞いをシミュレーションすることや高次元のデータを扱うことが得意であり,多体問題など量子力学が深く関わる量子化学計算による薬や触媒など材料の設計,また機械学習の高速化への貢献が期待されている。

量子コンピュータは「顧客にとってのより良いソリューションの提供に役立つもの」という観点では,まさに前述のNISQが目標になるが,この実現には量子コンピュータの「質」と「量」の双方の観点での向上が課題となる。これまで日立では,英国の日立ケンブリッジラボにてシリコン量子ビット素子の基礎物理研究を進めてきており,量子状態の読み出しで高精度なスピン状態読み出しを達成するなどの成果4)を挙げている。他社においても量子ビット素子の完成度向上を重視して,二つ,三つと次第に量子ビット数を増やしていく「質」を重視したボトムアップ的なアプローチが主流である。超電導量子ビットを用いることで50量子ビットを超えるものも開発されているが,この延長線上に量子優位性の壁を突破するNISQを実現することは困難であると言わざるを得ない。

日立は,この状態から2018年度に大きくギアチェンジを行い,従来とは逆のトップダウン方式を取ることに決めた。すなわち,均一な特性の素子を多数集積可能であるというシリコン半導体技術の優れた集積性を最大限に生かして,初めから「量」を重視した量子コンピュータをターゲットにする。次に,表面符号などの誤り検出・訂正手法の検討に加え,同様にシリコン高集積性によって可能になる二次元量子ビットアレイ,極低温CMOS回路・実装システム,ホットシリコン量子ビット,キャリブレーション・デジタル補正といったさまざまな技術を開発することで「質」を向上させる。このトップダウン方式に従い,2020年に64量子ビットが形成可能な量子ビットアレイの基本構造を試作した5)。セルフアラインプロセスによる狭ピッチ量子ビット・結合制御MOS形成や,SOI(Silicon on Insulator)とイントリンシック型チャネルを用いた高安定量子ビット形成などの技術を使用することで,電子1個の格納された量子ドットをアレイ上の所望の位置に安定的に形成できることを確認した。図3にシリコン量子ビットアレイの基本技術の概要を,図4に量子ビットアレイの基本構造を試作したチップの外観を示す。今後,本アレイ構造を用いて量子ビット操作の実証に取り組み,大規模集積化が可能なシリコン量子コンピュータの開発を加速させていく予定である。

3. おわりに

2020年,日立は内閣府のムーンショット型研究開発制度を通じたシリコン量子コンピュータの研究開発を開始した。さらに東京大学・慶應義塾大学で推進する量子イノベーションイニシアティブ協議会を通じて「IBM Q Network※3)」へ参加し,IBM社(International Business Machines Corporation)の量子コンピュータ「IBM Q」を使った量子アルゴリズムの共同研究も開始している。量子優位性の壁をいち早く突破することを目標に掲げ,今後もハードウェア・ソフトウェア・サービスの壁を越えた取り組みを推進していく予定である。

- ※3)

- 量子コンピューティングを進化させることを目的とした団体であり,参加組織はクラウドを介して量子コンピュータ「IBM Q」を利用できるほか,IBM社が保有する量子技術に関するリソースにアクセスできる。

謝辞

CMOSアニーリングマシンの成果の一部は,国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO:New Energy and Industrial Technology Development Organization)の委託業務(JPNP16007)の結果として得られたものである。

参考文献など

- 1)

- 日立ニュースリリース,半導体ベースの新型コンピュータを活用した損害保険ポートフォリオ最適化に関する実証実験を開始(2020.1)

- 2)

- 日立ニュースリリース,数十人,数百人規模の最適な勤務シフトを作成するソリューションを提供開始(2020.10)

- 3)

- F. Arute et al.: Quantum supremacy using a programmable superconducting processor, Nature, Vol.574, pp. 505-510(2019.10)

- 4)

- I. Ahmed et al.: Radio-Frequency Capacitive Gate-Based Sensing, Physical Review Applied, Vol.10, Iss.1, 014018 (2018.7)

- 5)

- N. Lee et al.: Enhancing electrostatic coupling in silicon quantum dot array by dual gate oxide thickness for large-scale integration, Applied Physics Letters, Vol.116, Iss.16, 162106(2020.4)